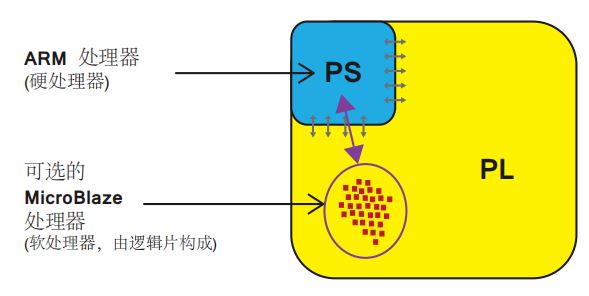

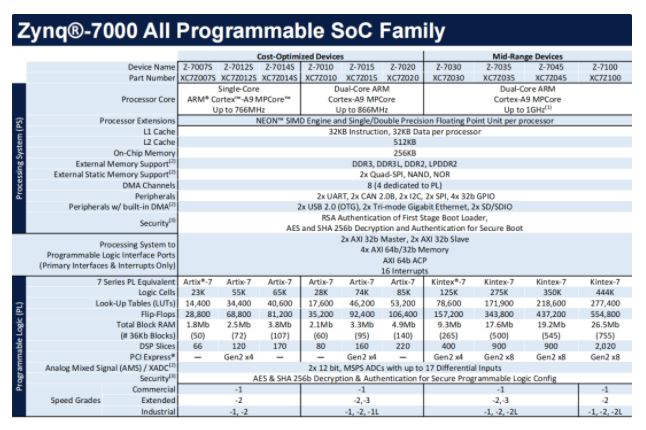

知道ZedBoard是性價比相對比較高的入門FPGA+ARM架構(gòu)設(shè)計的開發(fā)板,網(wǎng)上關(guān)于它的資料也是特別豐富。今天給大家推薦的這個中英文的《The Zynq Book》是全面的介紹Zynq Soc的較好的材料。 所有的Zynq-7000芯片具有相同的架構(gòu),是以ARM處理器系統(tǒng)為基礎(chǔ),它包含了一顆雙核ARM Cortex-A9處理器,它與軟核Microbraze是不同的,它是一顆專用的“硬核”,不占用FPGA的邏輯資源,并且比Microbraze有更高的性能。

Zynq-7000系列芯片的邏輯資源(PL)是不同的,Z-7020以下是基于A7 FPGA的,Z-7030以上是基于K7的,資源數(shù)量有所不同。而我們使用的Zedboard是Z-7020的。

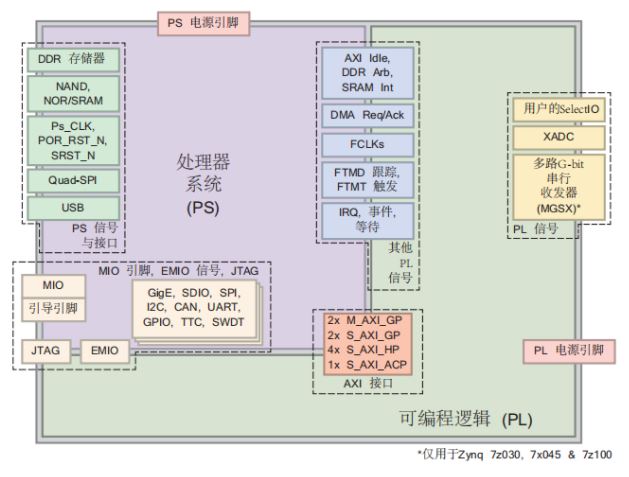

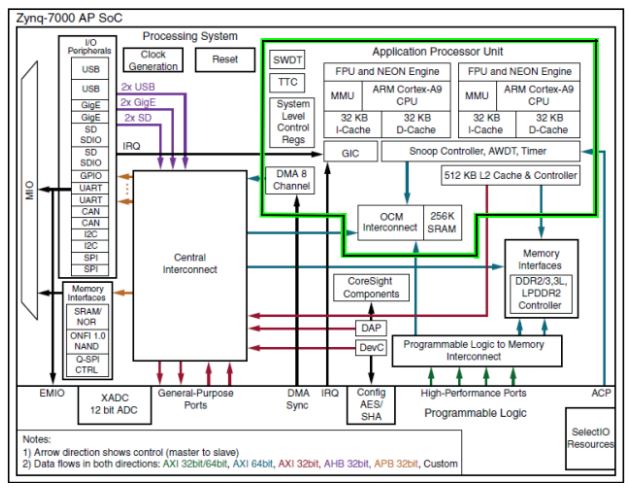

Zynq中所說的PS是指ARM處理器,PL是指FPGA部分,它們之間的主要連接方式是高帶寬低延遲的AXI接口,這也是Zynq上主要的數(shù)據(jù)通信機(jī)制,AXI_ACP是用于PL的一個cache一致性主機(jī)端口,AXI_HP用于PL的四個高性能/大帶寬主機(jī)端口,AXI_GP是通用端口,兩個主機(jī)端口,兩個從機(jī)端口。

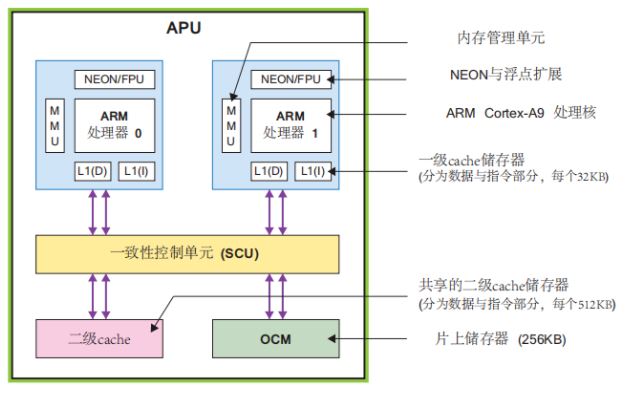

PS和PL端的協(xié)同設(shè)計是Zynq嵌入式系統(tǒng)設(shè)計的重要部分,PL適合并行流處理,而PS適合控制或具有串行執(zhí)行特性的部分以及浮點計算等。 另外,Zynq處理器系統(tǒng)并非只有ARM處理器,除了一個應(yīng)用處理器單元(APU),還有拓展外設(shè)接口、cache存儲器、存儲器接口、互聯(lián)接口和時鐘發(fā)生電路等。

其中APU主要由兩個ARM處理核組成,每個都關(guān)聯(lián)了一些可計算單元:一個NEONTM媒體處理引擎和浮點單元,一個內(nèi)存管理單元和一個一級cache存儲器等。其中NEON指令是對標(biāo)準(zhǔn)ARM指令集的拓展,可直接使用,NEON引擎實現(xiàn)了單指令多數(shù)據(jù)(SIMD)功能來實現(xiàn)媒體和DSP類算法的加速。

從編程的角度來看,對ARM指令的支持之前是由xilinx的SDK軟件來實現(xiàn)的,不過現(xiàn)在都統(tǒng)一到viTIs軟件中了,它包含了開發(fā)部署在ARM處理器上的軟件所需的全部內(nèi)容。目前最新的版本是viTIs 2022.2,我們使用的是2021.2。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<