在FPGA設(shè)計(jì)中經(jīng)常使用到邏輯復(fù)制,邏輯復(fù)制也用在很多場(chǎng)合。

1. 信號(hào)驅(qū)動(dòng)級(jí)數(shù)非常大,扇出很大,需要增加驅(qū)動(dòng)力

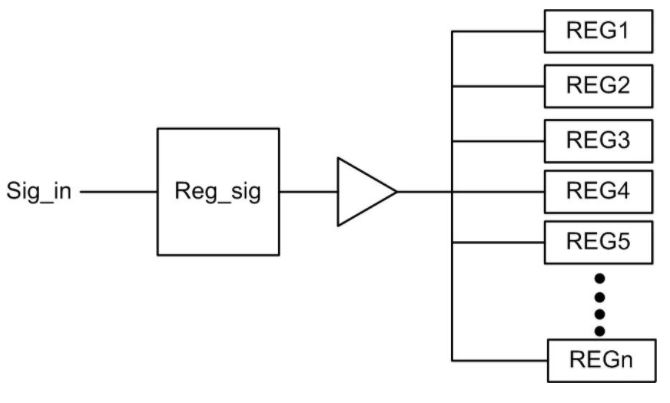

邏輯復(fù)制最常使用的場(chǎng)合時(shí)調(diào)整信號(hào)的扇出。如果某個(gè)信號(hào)需要驅(qū)動(dòng)后級(jí)很多單元,此時(shí)該信號(hào)的扇出非常大,那么為了增加這個(gè)信號(hào)的驅(qū)動(dòng)能力,一種辦法就是插入多級(jí)Buffer,但是這樣雖然能增加驅(qū)動(dòng)能力,但是也增加了這個(gè)信號(hào)的路徑延時(shí)。

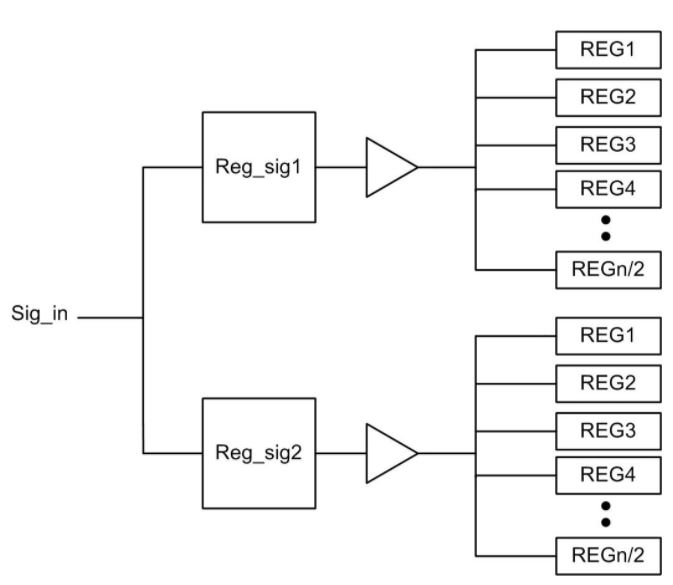

為了避免這種情況這時(shí)可以復(fù)制生成這個(gè)信號(hào)的邏輯,用多路同頻同相的信號(hào)驅(qū)動(dòng)后續(xù)電路,使平均到每路的扇出變低,這樣不需要插入Buffer就能滿足驅(qū)動(dòng)能力增加的要求,從而節(jié)約該信號(hào)的路徑延時(shí)。如從圖1.1到圖1.2轉(zhuǎn)變所示。

圖1.1 邏輯復(fù)制前

圖1.2 邏輯復(fù)制后

由于現(xiàn)在綜合器都已經(jīng)非常智能,此種場(chǎng)合的邏輯復(fù)制工作大多由綜合器完成,不需要人手動(dòng)調(diào)整。各大FPGA廠商的綜合器以及第三方綜合器都有這種功能。

2. FPGA中需要做很多重復(fù)工作

在某些FPGA設(shè)計(jì)中,需要很多重復(fù)設(shè)計(jì)的時(shí)候,這時(shí)候邏輯復(fù)制也就有用了。

例如:在某個(gè)特殊應(yīng)用場(chǎng)合需要設(shè)計(jì)方向可以任意改變的240位寬的三態(tài)IO管腳。我們先看看常用的一個(gè)位寬的三態(tài)管腳怎么設(shè)計(jì)。

module inout_interface(

dat_in,

io_out,

io_dir,

dat_out

);

input dat_in;

input io_dir;

output dat_out;

inout io_out;

assign io_out = io_dir ? dat_in : 1'bz; assign dat_out = io_out;

endmodule

如上述程序所示為單個(gè)雙向IO口的典型設(shè)計(jì)代碼,中間由IO輸入方向控制數(shù)據(jù)和高阻之間的切換,難題出現(xiàn)了,怎么設(shè)計(jì)240位寬的雙向IO口呢?難道如下列程序所示:

module inout_interface(

dat_in,

io_out,

io_dir,

dat_out

);

input [239 : 0] dat_in;

input [239 : 0] io_dir;

output [239 : 0] dat_out;

inout [239 : 0] io_out;

assign io_out = io_dir ? dat_in : 240'bz; assign dat_out = io_out;

endmodule

顯然這樣是不行的,因?yàn)楫?dāng)io_dir為240位的時(shí)候只有當(dāng)全為0的時(shí)候此式才為假,其余時(shí)候都為真,顯然達(dá)不到想要的每個(gè)IO都是雙向口的設(shè)計(jì)。

修改代碼如下:

module inout_interface( dat_in, io_out, io_dir, dat_out ); input [239 : 0] dat_in; input [239 : 0] io_dir; output [239 : 0] dat_out; inout [239 : 0] io_out; assign io_out[0] = io_dir[0] ? dat_in[0] : 1'bz; assign dat_out[0] = io_out[0]; assign io_out[1] = io_dir[1] ? dat_in[1] : 1'bz; assign dat_out[1] = io_out[1]; assign io_out[2] = io_dir[2] ? dat_in[2] : 1'bz; assign dat_out[2] = io_out[2]; . . // 此處略去1萬(wàn)行 . assign io_out[239] = io_dir[239] ? dat_in[239] : 1'bz; assign dat_out[239] = io_out[239]; endmodule

顯然這種辦法能實(shí)現(xiàn)240位寬的獨(dú)立方向控制IO,但是估計(jì)寫(xiě)代碼要累死人,有沒(méi)得更好的辦法呢?

當(dāng)然有,在verilog2001中有個(gè)邏輯復(fù)制語(yǔ)法——generate,可以對(duì)verilog模塊進(jìn)行無(wú)限復(fù)制。有了這個(gè)模塊我們即可輕松通過(guò)邏輯復(fù)制來(lái)達(dá)到我們的要求了。

// 單個(gè)雙向IO實(shí)現(xiàn)模塊 module pin_inout( indat, indir, outdat, outdaTIn ); input indat; input indir; inout outdat; output outdaTIn; assign outdat = indir ? indat : 1'bz; assign outdaTIn = outdat; endmodule module inout_interface( dat_in, io_out, io_dir, dat_out ); input [239 : 0] dat_in; input [239 : 0] io_dir; output [239 : 0] dat_out; inout [239 : 0] io_out; // 邏輯復(fù)制240次 genvar i; generate for(i = 0; i < 240; i = i + 1) begin : pin_loop pin_inout pin_inout_inst( .indat ( dat_in[i] ), .indir ( io_dir[i] ), .outdat ( io_out[i] ), .outdaTIn ( dat_out[i] ) ); end endgenerate endmodule

由上面代碼可看出,巧妙利用verilog語(yǔ)法能減少自身工作量。

3. 總結(jié)

在FPGA設(shè)計(jì)中有些情況的邏輯復(fù)制不需要我們做,但是有些情況的邏輯復(fù)制不得不手工完成,因此,熟練掌握verilog語(yǔ)法是設(shè)計(jì)出好的模型、減少工作量的前提。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<