第一部分 設(shè)計(jì)概述 /Design Introduction

1.1 設(shè)計(jì)目的

本次設(shè)計(jì)包括基于FPGA的任意波形發(fā)生器設(shè)計(jì)實(shí)現(xiàn)和基于FPGA的低通濾波器設(shè)計(jì)實(shí)現(xiàn)。

波形發(fā)生器是一種常見(jiàn)的信號(hào)源,能夠產(chǎn)生多種標(biāo)準(zhǔn)信號(hào)和用戶定義信號(hào),并保證較高精度和較高穩(wěn)定性,廣泛地應(yīng)用于電子電路、自動(dòng)控制系統(tǒng)和數(shù)字實(shí)驗(yàn)等,諸如電話、電視、收音機(jī)、高校通信系統(tǒng)實(shí)驗(yàn)等領(lǐng)域都需要用到波形發(fā)生器。本次設(shè)計(jì)基于Verilog HDL語(yǔ)言使用Artix-7系列芯片在EGO1開(kāi)發(fā)板上實(shí)現(xiàn)一個(gè)簡(jiǎn)易的任意波形發(fā)生器。該波形發(fā)生器能夠產(chǎn)生正弦波、方波、三角波與鋸齒波四種波形,可輸出頻率有:1MHz、100KHz、10KHz、1KHz、100Hz、10Hz、1Hz。波形類型選擇控制字與頻率設(shè)置控制字通過(guò)串口輸入。

低通濾波可以簡(jiǎn)單的認(rèn)為:設(shè)定一個(gè)頻率點(diǎn),當(dāng)信號(hào)頻率高于這個(gè)頻率時(shí)不能通過(guò),在數(shù)字信號(hào)中,這個(gè)頻率點(diǎn)也就是截止頻率,當(dāng)頻域高于這個(gè)截止頻率時(shí),則全部賦值為0。因?yàn)樵谶@一處理過(guò)程中,讓低頻信號(hào)全部通過(guò),所以稱為低通濾波。低通過(guò)濾的概念存在于各種不同的領(lǐng)域,諸如電子電路,數(shù)據(jù)平滑,聲學(xué)阻擋,圖像模糊等領(lǐng)域經(jīng)常會(huì)用到。在數(shù)字圖像處理領(lǐng)域,從頻域看,低通濾波可以對(duì)圖像進(jìn)行平滑去噪處理。

本次設(shè)計(jì)將用兩種方式實(shí)現(xiàn)低通濾波器。

方法一:利用Vivado自身具備的DDS和FIR的IP核實(shí)現(xiàn);

方法二:通過(guò)Verilog編程實(shí)現(xiàn)FIR的功能。

1.2 作品展示

圖1 UART串口實(shí)現(xiàn)

圖2 波形發(fā)生器仿真

圖3 低通濾波器仿真

第二部分 系統(tǒng)組成及功能說(shuō)明 /System Construction & Function Description

2.1 系統(tǒng)概述

任意波形發(fā)生器:計(jì)劃產(chǎn)生正弦波、方波、三角波與鋸齒波四種波形,可輸出頻率有:1MHz、100KHz、10KHz、1KHz、100Hz、10Hz、1Hz,利用URAT串口與串口調(diào)試助手相連進(jìn)行控制字?jǐn)?shù)據(jù)傳輸。已經(jīng)完成全部功能,由于沒(méi)有示波器,實(shí)物調(diào)試部分不完整。

低通濾波器:本次設(shè)計(jì)將用兩種方式實(shí)現(xiàn)低通濾波器。

方法一:利用Vivado自身具備的DDS和FIR的IP核實(shí)現(xiàn);

方法二:通過(guò)Verilog編程實(shí)現(xiàn)FIR的功能。

方法一使用Vivado的DDS IP核生成兩個(gè)正弦信號(hào),頻率分別為4MHz和5MHz。同時(shí)調(diào)用乘法器IP將兩個(gè)信號(hào)進(jìn)行混頻處理,乘法器將混頻信號(hào)交給FIR IP核進(jìn)行過(guò)濾處理。使用Matlab進(jìn)行濾波器的參數(shù)設(shè)計(jì),這里使用窗函數(shù)法設(shè)計(jì)FIR濾波器。窗函數(shù)法設(shè)計(jì)濾波器的基本思想是:選擇一種合適的理想頻率選擇性濾波器,然后將它的沖激響應(yīng)截短以獲得一個(gè)具有線性相位和因果的FIR濾波器,因此這種方法的關(guān)鍵是選區(qū)某種較好的窗函數(shù),在濾波器性能給定的情況下,盡量選擇主瓣窄,旁瓣峰值小的窗函數(shù)。設(shè)置好以后將FIR濾波器系數(shù)導(dǎo)出,將生成好coe文件導(dǎo)入Vivado中FIR IP核中。撰寫(xiě)TestBench文件進(jìn)行波形仿真。

方法二利用DDS 生成一個(gè)由三個(gè)正弦波疊加的待濾波信號(hào),兩個(gè)正弦波的頻率分別是200Hz、800Hz。用MATLAB產(chǎn)生頻率為500Hz的低通濾波器抽頭系數(shù),然后將待濾波信號(hào)送入Vivado,用Verilog編寫(xiě)的FIR濾波器進(jìn)行仿真,觀察濾波后的波形。

2.2 項(xiàng)目系統(tǒng)框圖

任意波形發(fā)生器:

圖4 任意波形發(fā)生器系統(tǒng)框圖

圖5 串口模塊設(shè)計(jì)框圖

圖6 DDS原理框圖

低通濾波器:

圖7 低通濾波器設(shè)計(jì)框圖

圖8 低通濾波器原理框圖

2.3 技術(shù)說(shuō)明

(1)任意波形發(fā)生器

本次設(shè)計(jì)使用到的是UART串口通信,主要用來(lái)接收串口數(shù)據(jù)發(fā)送的數(shù)據(jù),字節(jié)傳輸形式:1-0-x-x-x-x-x-x-x-x-0-1,檢測(cè)到下降沿即-1-0-(起始標(biāo)志)后開(kāi)始進(jìn)行接收字節(jié),將接收到的一一存入寄存器中,8個(gè)bit后結(jié)束接收,就是簡(jiǎn)單的1個(gè)字節(jié)的接收。其協(xié)議發(fā)送原理:

圖9 UART數(shù)據(jù)幀格式

根據(jù)URAT串口的數(shù)據(jù)幀格式,起始位為0,所以我們需要用一個(gè)下降沿檢測(cè)模塊,來(lái)判斷起始位,然后開(kāi)始準(zhǔn)備接收串口數(shù)據(jù)。

然后使用一個(gè)計(jì)數(shù)器模塊,在1Bit數(shù)據(jù)傳輸?shù)臅r(shí)間找到最佳時(shí)間來(lái)輸出讀取串口數(shù)據(jù)。在串口通信中波特率表示每秒能傳輸?shù)臄?shù)據(jù)位,9600就是每秒能傳輸9600位,1word=2byte、1byte=8bit,這里的9600位指的是9600bit。每個(gè)開(kāi)發(fā)板上都有它的系統(tǒng)時(shí)鐘,本次設(shè)計(jì)用的是EGO1開(kāi)發(fā)板,系統(tǒng)時(shí)鐘是100MHZ,我們假定波特率是9600bit/s傳輸,那么傳輸1bit就需要100M/9600個(gè)時(shí)鐘周期。那么在本次設(shè)計(jì)中傳輸1bit所需的計(jì)數(shù)值為10416,將采集數(shù)據(jù)的時(shí)刻放在波特率計(jì)數(shù)器每次循環(huán)技術(shù)的中間位置,即5208。

利用一個(gè)控制器模塊,在下降沿檢驗(yàn)通過(guò)后的信號(hào)與計(jì)數(shù)器模塊輸出的讀數(shù)據(jù)時(shí)間信號(hào)控制下,依次將8位數(shù)據(jù)放入寄存器之中,然后利用case語(yǔ)句,經(jīng)過(guò)停止位數(shù)據(jù)后停止數(shù)據(jù)接收。

最后在串口的總模塊中對(duì)上述三個(gè)模塊進(jìn)行例化,將對(duì)應(yīng)輸入輸出相連。

下面根據(jù)下圖所示的DDS技術(shù)原理框圖,當(dāng)一個(gè)參考時(shí)鐘過(guò)來(lái) 傳輸一個(gè)頻率控制字進(jìn)入累加器在累加器中加入上一個(gè)參考時(shí)鐘的數(shù)據(jù),相加后進(jìn)去寄存器,然后寄存器的輸出便是正弦查表的地址,通過(guò)這個(gè)數(shù)據(jù)在波形存儲(chǔ)區(qū)查表,再通過(guò)D/A轉(zhuǎn)換器和低通濾波器輸出。結(jié)合項(xiàng)目功能要求實(shí)際分模塊實(shí)現(xiàn)任意波形發(fā)生器。

波形類型控制字與頻率設(shè)置控制字是分別拿串口助手輸入的有效數(shù)據(jù)位的[7:6]與[5:2]位,我們注意到,串口傳輸過(guò)程是從低字節(jié)開(kāi)始傳輸?shù)模簿褪钦f(shuō)我們?cè)诖谥种邪l(fā)送的有效數(shù)據(jù)為11010011,接收到的數(shù)據(jù)為11001011,所以需要將接收到的數(shù)據(jù)倒序然后給到兩個(gè)控制字的寄存器。

圖10 DDS直接數(shù)字頻率合成技術(shù)原理

首先我們利用MATLAB新建腳本(。m文件),鍵入相應(yīng)的程序,產(chǎn)生了存放有位寬為8,位深為256的四種波形數(shù)據(jù)的COE文件。然后在Vivado中利用IP catalog中的Block Memory Generator核。分別新建四個(gè)Block Memory Generator核,設(shè)置Basic欄中的Memory Type為Single Port ROM,Port A Options 欄中的位寬為8,位深為256,最后在Other Options中,選擇加載本地文件選中MATLAB已經(jīng)生成的正弦波、方波、鋸齒波、三角波的COE數(shù)據(jù)文件,分別將它們放入了不同的Rom中,我們就可以通過(guò)Vivado進(jìn)行編程,在時(shí)鐘的驅(qū)動(dòng)下,根據(jù)地址去讀取Rom中的數(shù)據(jù)然后輸出,即可產(chǎn)生波形數(shù)據(jù)。

我們拿到URAT串口接收的頻率控制字后,利用case語(yǔ)句,根據(jù)不同的輸入,輸出不同的頻率控制字,關(guān)于頻率控制字的計(jì)算,首先系統(tǒng)的時(shí)鐘為100MHz,相位累加器為32位,232等于4294967296,想要輸出頻率為1kHz的信號(hào)為例,通過(guò)以下的計(jì)算公式,得到K約等于42950。

然后在相位累加器中以頻率控制字為步長(zhǎng)進(jìn)行周期的加法運(yùn)算,再將相位累加器的每個(gè)值的高位作為地址去讀Rom的數(shù)據(jù)。這里輸出的為8位的DAC數(shù)據(jù),所以用相位累加器的高八位作為Rom的地址輸入。

(2)低通濾波器

低通濾波器實(shí)現(xiàn):

方法一:利用Vivado自身具備的DDS和FIR的IP核實(shí)現(xiàn)

在Vivado中新建工程,創(chuàng)建Block Design,用DDS IP核生成兩個(gè)正弦波信號(hào),如圖11所示。

圖11 DDS IP核

將DDS的參數(shù)設(shè)置為圖12所示。

圖12 DDS參數(shù)設(shè)置

(2)調(diào)用乘法器,將兩個(gè)正弦波信號(hào)進(jìn)行混頻處理,乘法器設(shè)置如下圖13

圖13 乘法器IP核參數(shù)設(shè)置

(3)調(diào)用FIR IP核,對(duì)其參數(shù)進(jìn)行設(shè)置。利用Matlab對(duì)濾波器的參數(shù)進(jìn)行設(shè)置。在matlab窗口輸入fdatool,在彈出的窗口中,在Response Type(濾波器響應(yīng)類型)一欄中選擇Lowpass(低通),Desgned Method(實(shí)現(xiàn)方法)選擇Window(窗函數(shù)實(shí)現(xiàn)),即基于窗函數(shù)法設(shè)計(jì)FIR濾波器,我們?cè)贠ptions中選擇Hamming窗,F(xiàn)ilter Order中選擇Special Order,濾波器階數(shù)選擇128(階數(shù)越高,濾波效果越好,占用的芯片資源會(huì)更多些)Frequency Specializations中單位Units選擇MHz,采樣頻率Fs選擇100MHz(根據(jù)奈奎斯特低通信號(hào)采樣定理,采樣頻率至少高于信號(hào)的2倍,實(shí)際工程上一般得高于低通信號(hào)頻率的5-10倍,如果信號(hào)頻率過(guò)高的話,實(shí)際的AD采樣頻率核精度無(wú)法達(dá)到,所以工程上一般把低通信號(hào)經(jīng)調(diào)制后搬到頻率很高的載波上,再下變頻到中頻上用帶通采樣定理進(jìn)行AD采樣),之前提到采樣頻率高于信號(hào)頻率的5-10倍就可以,因?yàn)槲覀冞@里FIR濾波器時(shí)鐘是和板卡時(shí)鐘連接在一起的,沒(méi)有編寫(xiě)時(shí)鐘分頻模塊,所以這里采樣頻率直接設(shè)置為100MHz(一個(gè)周期點(diǎn)數(shù)為100MHz/2MHz=50,板卡資源會(huì)浪費(fèi)一些,但是不影響),截止頻率Fc設(shè)為2MHz(1MHz的正弦波通過(guò),9MHz的被濾除),點(diǎn)擊View和Design Filter按鈕,設(shè)計(jì)的濾波器時(shí)域和頻域波形(Time Domain and Frequency domain)以及幅相響應(yīng)(Magnitude and Phase Response),最后生成coe文件,加載到FIR IP核中。具體設(shè)置如下圖。

圖14 濾波器參數(shù)設(shè)置

(4)將各IP核之間進(jìn)行連線,生成頂層模塊。如圖15。

圖15 各IP核連線圖

方法二:通過(guò)Verilog編程實(shí)現(xiàn)FIR的功能。具體設(shè)計(jì)流程如圖16。

圖16 設(shè)計(jì)流程圖

(1)利用DDS 生成一個(gè)由三個(gè)正弦波疊加的待濾波信號(hào),兩個(gè)正弦波的頻率分別是200Hz、800Hz。

(2)用MATLAB產(chǎn)生頻率為500Hz的低通濾波器抽頭系數(shù),

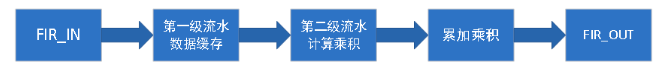

(3)Vivado進(jìn)行FIR的verilog設(shè)計(jì)。FIR的代碼實(shí)現(xiàn)流程如下圖7所示。

圖17 FIR verilog設(shè)計(jì)框圖

第一級(jí)流水線的功能是將輸入信號(hào)進(jìn)行延時(shí),每到來(lái)一個(gè)時(shí)鐘信號(hào),便將輸入信號(hào)保存到delay_pipelin1中,然后將剩下的依次移動(dòng)一位。

第二級(jí)流水線的功能是將輸入經(jīng)過(guò)延時(shí)的信號(hào)和濾波器系數(shù)相乘,每到來(lái)一個(gè)時(shí)鐘便將一個(gè)新的乘積結(jié)果更新到multi_data中。

累加積乘的主要功能是將乘積累加,累加的結(jié)果就是濾波后的信號(hào)。

(4)仿真測(cè)試,創(chuàng)建TestBench文件進(jìn)行仿真測(cè)試。

第三部分 完成情況及性能參數(shù) /Final Design & Performance Parameters

任意波形發(fā)生器

已實(shí)現(xiàn)功能:產(chǎn)生正弦波、方波、三角波與鋸齒波四種波形,可輸出頻率有:1MHz、100KHz、10KHz、1KHz、100Hz、10Hz、1Hz;利用URAT串口與串口調(diào)試助手相連進(jìn)行控制字?jǐn)?shù)據(jù)傳輸。由于沒(méi)有示波器,實(shí)物調(diào)試部分不完整。

a.串口模塊仿真分析:在Testbench中依次給串口數(shù)據(jù)(data_rx)為10 11010011 011。

圖18 URAT串口仿真波形

如上圖所示,F(xiàn)PGA接收到的數(shù)據(jù)為11001011,根據(jù)仿真結(jié)果,URAT串口測(cè)試成功。

b.任意波形發(fā)生模塊仿真分析:

圖19 波形發(fā)生模塊仿真1

圖20 波形發(fā)生模塊仿真2

如上圖所示,在仿真中分別給波形類型控制字為0、1、2、3,對(duì)應(yīng)頻率設(shè)置控制字為5、6、3、2。分別產(chǎn)生了頻率為10kHz的正弦波、100kHz的三角波、100Hz的三角波、10Hz的鋸齒波。其中100kHz的三角波為方波,詢問(wèn)老師后確定是系統(tǒng)顯示問(wèn)題,其波形數(shù)據(jù)圖 所示。根據(jù)分析知波形發(fā)生器仿真測(cè)試成功。

c.系統(tǒng)仿真測(cè)試與分析

最后通過(guò)頂層模塊,例化DDS模塊與UART模塊,將相應(yīng)輸入輸出連接起來(lái),編寫(xiě)仿真激勵(lì)文件,給串口助手發(fā)送值,驗(yàn)證波形輸出。

圖21 系統(tǒng)仿真測(cè)試1

圖22 系統(tǒng)仿真測(cè)試2

圖23 系統(tǒng)仿真測(cè)試3

圖24 系統(tǒng)仿真測(cè)試4

如上所示,根據(jù)仿真波形可知,當(dāng)仿真輸入1011010011011,F(xiàn)PGA收到11001011,類型控制字11(3),頻率設(shè)置控制字0100 (4),輸出周期為 1ms(即頻率為1KHz)的 鋸齒波;

當(dāng)仿真輸入1000011111011,F(xiàn)PGA收到11111000,類型控制字00(0), 頻率設(shè)置控制字0111(7),輸出周期為1000ns頻率 (即頻率為1MHz )的正弦波;

當(dāng)仿真輸入1001010111011,F(xiàn)PGA收到11101010,類型控制字01(1),頻率設(shè)置控制字0101(5),輸出周期為100us( 即頻率為10KHz)的方波 ;

當(dāng)仿真輸入1010011011011,F(xiàn)PGA收到11011001,類型控制字10(2),頻率設(shè)置控制字0110(6),輸出周期為10us(即頻率為100KHz)的三角波。

根據(jù)分析可知,系統(tǒng)仿真成功,接下來(lái)Run Synthesis→Run Implementation,然后在Windows的下拉選項(xiàng)中點(diǎn)擊I/O Port,根據(jù)EGO1硬件手冊(cè)上的引腳說(shuō)明綁定引腳,選擇邏輯電平為L(zhǎng)VCMOS33,然后保存即可生成引腳約束文件。最后Generate Bitstream→Open Hardware Manager→Open Target→Auto Connect→選中生成的bit文件→Program即可進(jìn)行實(shí)物測(cè)試。

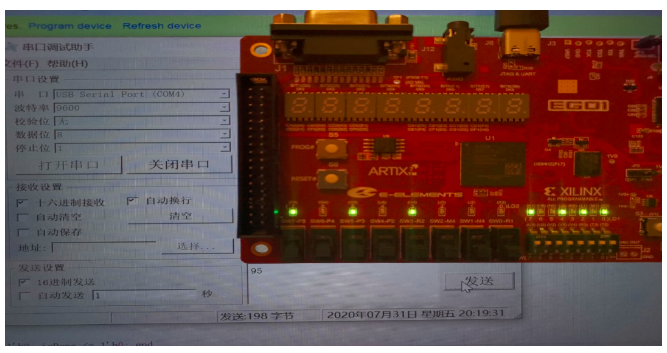

圖25 系統(tǒng)實(shí)物調(diào)試

圖26 系統(tǒng)實(shí)物調(diào)試

將BIT文件下入EGO1開(kāi)發(fā)板后,打開(kāi)串口助手,發(fā)送“de”,即二進(jìn)制的“11011110”,可以觀察到代表FPGA串口接收數(shù)據(jù)的LED1中的八個(gè)燈的數(shù)據(jù)(亮為“1”,滅為“0”)為11011110;發(fā)送“95”,即二進(jìn)制的“10010101”時(shí),LED1燈群展示數(shù)據(jù)為10010101。由于沒(méi)有示波器,不能看到波形,僅能通過(guò)LED2中的LED7—LED2顯示可以看出DDS波形發(fā)生器的波形類型控制字與頻率設(shè)置控制字?jǐn)?shù)據(jù)都是對(duì)的。至此,正確實(shí)現(xiàn)任意波形發(fā)生器功能。

低通濾波器

低通濾波器通過(guò)IP核設(shè)計(jì)得以實(shí)現(xiàn),仿真波形如下圖8所示。

圖27 FIR—IP核實(shí)現(xiàn)仿真波形

通過(guò)上面仿真波形可以看出4MHz和5MHz的正弦混頻信號(hào)經(jīng)過(guò)FIR低通濾波器后將9MHz的高頻正弦信號(hào)濾除掉了,輸出為我們需要的1MHz低頻信號(hào)。

圖27 FIR-Verilog代碼實(shí)現(xiàn)仿真波形

如上圖所示,DDS產(chǎn)生頻率為200Hz與800Hz輸入,DDS_out為疊加信號(hào),低通濾波器輸出波形不符合功能要求,未能定位到具體原因,仿真錯(cuò)誤、系統(tǒng)功能未正確實(shí)現(xiàn)。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<