ASIC設(shè)計(jì)中詳細(xì)設(shè)計(jì)方案的確定非常重要,同樣的設(shè)計(jì),別人可以用比你小30%的面積和少30%的處理時(shí)間來(lái)實(shí)現(xiàn),這才是設(shè)計(jì)工程師的價(jià)值體現(xiàn)之處。 任何設(shè)計(jì)在最開(kāi)始的時(shí)候都是一頭霧水,場(chǎng)景復(fù)雜,各種耦合。我們要做的是將所有的場(chǎng)景都整理出來(lái),然后想辦法進(jìn)行歸一。任何一開(kāi)始覺(jué)得不可能做到的任務(wù)最后都能找到解決方法。 這本來(lái)看似是沒(méi)有規(guī)律的世界,但人類就是去不斷尋找和發(fā)現(xiàn)這個(gè)物質(zhì)世界的運(yùn)行規(guī)律。 當(dāng)然,即使第一版設(shè)計(jì)我們盡可能的考慮到了更多的場(chǎng)景和實(shí)現(xiàn)方案,但是最后實(shí)現(xiàn)階段還是會(huì)有一些考慮不周全和不合理的實(shí)現(xiàn),由于時(shí)間成本原因,決定放到下一版再修改。這個(gè)過(guò)程就叫做優(yōu)化!那么,如何優(yōu)化一個(gè)設(shè)計(jì)?

找大寄存器組

首先是找設(shè)計(jì)中的大寄存器組,寄存器是面積較大的基本單元了,寄存器的數(shù)量決定了設(shè)計(jì)整體的面積數(shù)量級(jí)。小容量的存儲(chǔ)用regfile,一般寄存器組用到了上千bit,就要考慮是否用RAM。上萬(wàn)bit的就是不合理的設(shè)計(jì)。 看到大寄存器組是要重點(diǎn)關(guān)注優(yōu)化的對(duì)象,要注意的是,寄存器組是可以隨意在任意bit取值的,RAM是需要一拍一拍的讀取的,所以需要在高并行度和面積之前做折中(trade off)。 數(shù)據(jù)通路寄存器打拍過(guò)多,肯定不合理,一個(gè)數(shù)據(jù)打一拍最起碼是幾十個(gè)bit,打多拍,就上百bit。而換一個(gè)設(shè)計(jì)思路,在控制上多少邏輯,控制信號(hào)+計(jì)數(shù)器,多做幾組也就攏共幾十個(gè)bit的樣子。比如前一級(jí)模塊傳過(guò)來(lái)的數(shù)據(jù)和valid信號(hào),數(shù)據(jù)是要晚幾拍才使用,應(yīng)該做成前一級(jí)模塊先給valid信號(hào),數(shù)據(jù)晚幾拍再來(lái),避免數(shù)據(jù)打拍。 在數(shù)據(jù)通路上出現(xiàn)一些組合邏輯路徑并不長(zhǎng),打了一拍,這樣雖然時(shí)序會(huì)更好,但是最后增加的面積來(lái)說(shuō)并不值得,所以多余的寄存器打拍完全可以“干”掉。

重定時(shí)

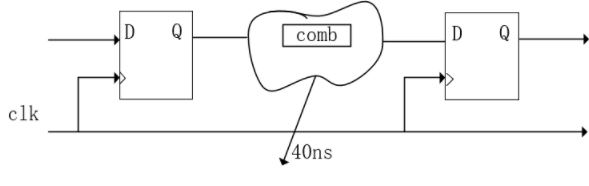

ReTIming就是重新調(diào)整時(shí)序,例如電路中遇到復(fù)雜的組合邏輯,延遲過(guò)大,電路時(shí)序不滿足,這個(gè)時(shí)候采用流水線技術(shù),在組合邏輯中插入寄存器加流水線,進(jìn)行操作,面積換速度思想。

任何的數(shù)字電路都可以等效成組合邏輯加D觸發(fā)器打拍,兩個(gè)D觸發(fā)器之間的組合邏輯路徑?jīng)Q定了,系統(tǒng)的工作頻率,決定芯片的性能。所以為了提高芯片的工作頻率,使用流水線技術(shù)在組合邏輯中插入寄存器。

插入寄存器的位置需要慎重選擇,不同的位置數(shù)據(jù)的打拍所消耗的寄存器的數(shù)量也不同,比方說(shuō)你在位置a消耗25bit寄存器,位置b消耗20bit寄存器,能省則省。

前面插入寄存器的位置使得comb1的延遲為30ns,comb2的延遲為10ns,系統(tǒng)的最高工作頻率是由最長(zhǎng)路徑?jīng)Q定的。也就是說(shuō)你這個(gè)系統(tǒng)最高工作頻率的周期,不小于30ns,前面是插入pipeline,這個(gè)時(shí)候我們不改變時(shí)序,采用重定時(shí)技術(shù),使得各個(gè)組合邏輯之間的延遲相當(dāng)。

瘋狂復(fù)用

找計(jì)算邏輯相同的單元,復(fù)用 最常見(jiàn)的就是計(jì)數(shù)器,能用一個(gè)計(jì)數(shù)器實(shí)現(xiàn)的,就別用倆,底層模塊之間相同的邏輯盡量使用一塊電路,減少重復(fù)的設(shè)計(jì)。 基本邏輯單元的共享舉例,面積:加法器 > 比較器 > 選擇器。加比選。 乘法器本質(zhì)上也是全加器。 所以就有先選后比,先選后加,先選后乘。 畫(huà)個(gè)圖意思一下。

這里的加法器可以換成任何邏輯或模塊。

乘法器分時(shí)復(fù)用度提高

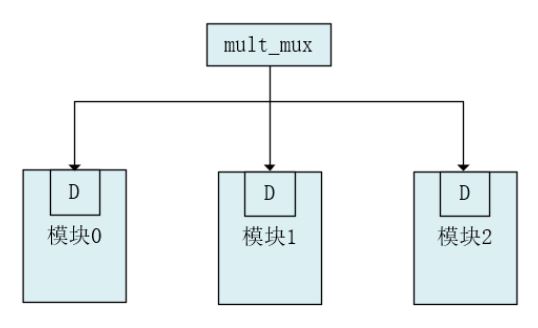

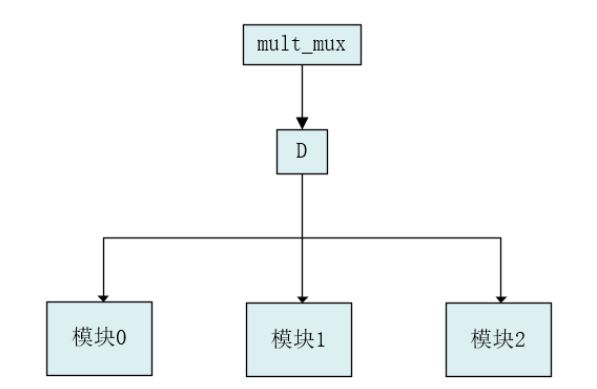

在計(jì)算模塊中乘法器也是非常大的一部分邏輯,一個(gè)設(shè)計(jì)要考慮PPA最優(yōu),就要考慮乘法器的數(shù)量多少以及復(fù)用能不能最大化,追求最好的設(shè)計(jì)是整個(gè)數(shù)據(jù)通路中乘法器空閑不下來(lái)。 乘法器調(diào)用方法,一般是在乘法器的輸入保證寄存器輸入,結(jié)果輸出到各個(gè)復(fù)用模塊時(shí)打一拍再使用。可以做成在進(jìn)行完乘法運(yùn)算后,就打拍,這樣消耗的寄存器會(huì)少很多。畫(huà)個(gè)圖意思一下(單bit)。

修改前

修改后 修改完后的寄存器省了很多,但是乘法器的輸出寄存器負(fù)載會(huì)變大,不過(guò)后端綜合時(shí)約束了max_fan_out工具會(huì)自動(dòng)插buffer和復(fù)制寄存器,經(jīng)過(guò)實(shí)測(cè)還是會(huì)節(jié)省很多面積,把一些優(yōu)化工作可以交給工具去做,了解它,信任它,使用它。

RAM的復(fù)用

從設(shè)計(jì)的整體來(lái)看,RAM也可以復(fù)用,前面處理用過(guò)的ram,現(xiàn)在空下來(lái),后面能否用。

最后

總結(jié)一下ASIC單個(gè)模塊的設(shè)計(jì)/優(yōu)化思路,列出所有條件,然后歸一,復(fù)用,面積與速度呼喚的思想貫穿始終。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<