淺談XILINX FPGA CLB單元 之 進位邏輯鏈(CARRY4原理分析,超前快速進位邏輯結(jié)構(gòu))

一、可配置邏輯塊(Configurable Logic Block, CLB)簡介

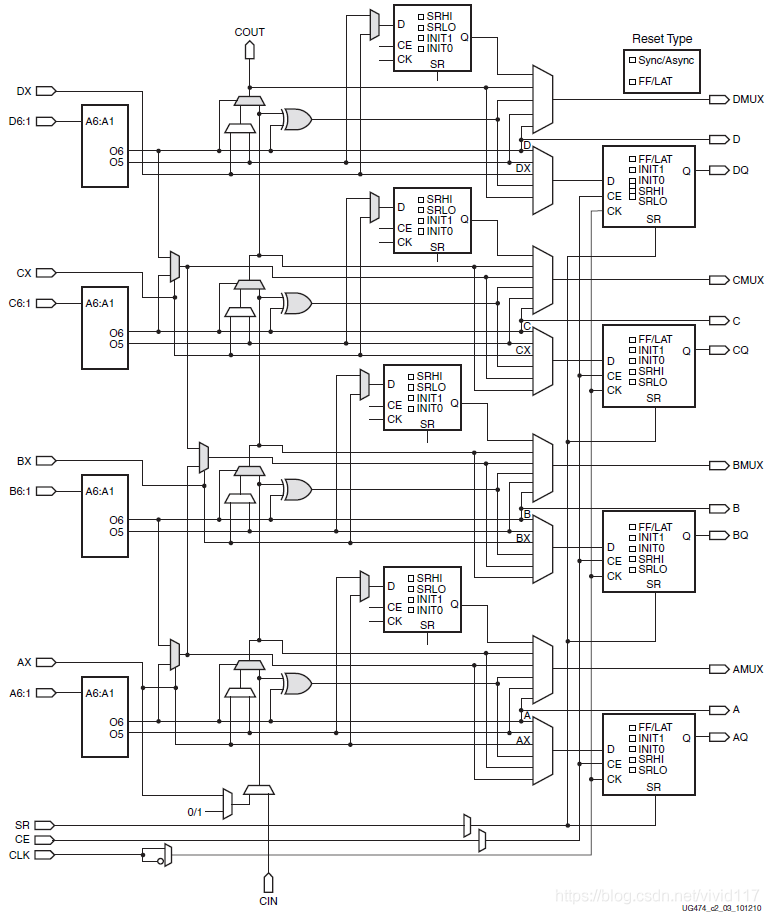

CLB可配置邏輯塊是指實現(xiàn)各種邏輯功能的電路,是xilinx基本邏輯單元。下圖給出了一個 SLICEM 的內(nèi)部結(jié)構(gòu)。

其中包含4個6輸入LUT、進位鏈、多路復(fù)用器和8個寄存器

在Xilinx FPGA中,每個可配置邏輯塊(CLB)包含2個Slice。每個Slice 包含查找表、寄存器、進位鏈和多個多數(shù)選擇器構(gòu)成。而Slice又有兩種不同的邏輯片:SLICEM和SLICEL。SLICEM有多功能的LUT,可配置成移位寄存器,或者ROM和RAM。邏輯片中的每個寄存器可以配置為鎖存器使用。今天寫這篇文章的目的主要是為了讓我們搞清楚FPGA重要資源CLB、Slice、LUT。

二、進位邏輯鏈

CLB進位模塊

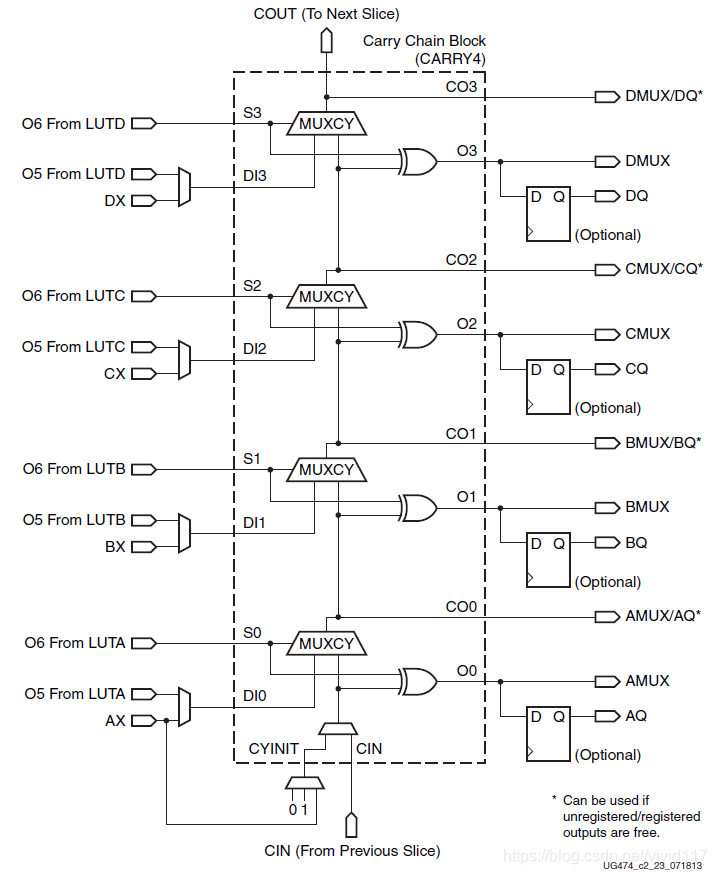

在CLB中,除了函數(shù)發(fā)生器之外,還提供了專用的快速超前進位邏輯,以slice片中執(zhí)行快速算術(shù)加法和減法。7系列FPGA CLB具有兩個獨立的進位鏈,如下圖所示。進位鏈可級聯(lián)以形成更寬的加/減邏輯。

進位邏輯鏈的結(jié)構(gòu)(CARRY4)

7系列FPGA 每個 SLICE有 4bit 的進位鏈。進位鏈向上延伸,每個slice的高度為四位。對于每個位,都有一個進位多路復(fù)用器(MUXCY) 和專用的XOR門,用于用選定的進位位加/減操作數(shù)。專用的進位路徑和進位多路復(fù)用器(MUXCY)也可以用于級聯(lián)函數(shù)發(fā)生器,以實現(xiàn)廣泛的邏輯功能。

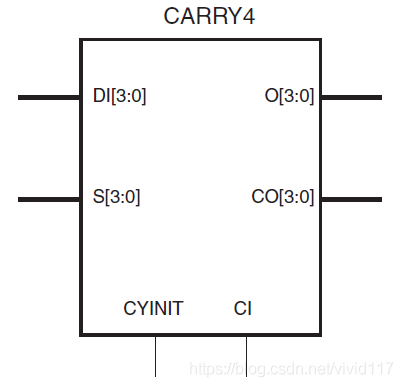

CARRY4模塊

CARRY4原語實例化每個slice中可用的快速進位邏輯。該原語與LUT結(jié)合使用以構(gòu)建加法器和乘法器。下圖顯示了CARRY4原語。綜合工具通常會從算術(shù)HDL代碼中推斷出此邏輯,從而自動正確連接此功能。

端口信號

1)總輸出-O [3:0] 總和輸出提供加/減的最終結(jié)果。它們連接到slice AMUX / BMUX / CMUX / DMUX輸出。

2)進位輸出-CO [3:0] 進位輸出提供每個位的進位。CO [3]等效于COUT。如果通過COUT將CO [3]連接到另一個CARRY4原語的CI輸入,則可以創(chuàng)建更長的進位鏈,并且專用路由將進位鏈連接到一排片上。

3)進位輸出還可以選擇連接至sliceAMUX / BMUX / CMUX / DMUX輸出。

三、CARRY4結(jié)構(gòu)能實現(xiàn)快速超前加法的原理

CARRY4的原理過程:

1)端口S[3:0]是要求數(shù)據(jù)的異或輸入;

2)端口DI[3:0]是數(shù)據(jù)的輸入(a,b都可以),通過選擇器判斷是否是進位標志;

3)MUXCY選擇器作為向下一級輸出標志的選擇端口;

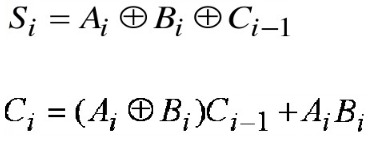

對于一個全加器

具體的原理可以參考之前的一篇博客: 數(shù)字電路基礎(chǔ)知識(四) 加法器-半加器、全加器與超前進位加法器

基本的進位標志和輸出如下。

對于CARRY4,端口S端其實是已經(jīng)做過亦或處理的輸入了。

即:

S=a@b //(@表示異或)

端口D可以任選a、b輸入當中的一個,如選擇b

輸出端:

那么O端即表示輸出端:O = S@cin = a@b@cin

進位端:

CO=(a@b)‘b +(a@b)cin //利用多路復(fù)用器:y=s'b+scin

=(a'b+ab’)‘b+(a@b)cin

=(a'b)’(ab‘)'b+(a@b)cin

=(a+b’)(a'+b)b+(a@b)cin

=(ab+b'b)(a'+b)+(a@b)cin

=ab(a'+b)+(a@b)cin

=(a@b)cin+ab

所以此CARRY4結(jié)構(gòu)能夠?qū)崿F(xiàn)快速超前進位加法器。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<