1、前言

分頻器是FPGA設(shè)計(jì)中使用頻率非常高的基本單元之一。盡管目前在大部分設(shè)計(jì)中還廣泛使用集成鎖相環(huán)(如Altera的PLL,Xilinx的DLL)來進(jìn)行時(shí)鐘的分頻、倍頻以及相移設(shè)計(jì),但是,對于時(shí)鐘要求不太嚴(yán)格的設(shè)計(jì),通過自主設(shè)計(jì)進(jìn)行時(shí)鐘分頻的實(shí)現(xiàn)方法仍然非常流行。首先這種方法可以節(jié)省鎖相環(huán)資源,再者這種方式只消耗不多的邏輯單元就可以達(dá)到對時(shí)鐘的操作目的。

2、整數(shù)倍分頻器的設(shè)計(jì)

2.1 偶數(shù)倍分頻

偶數(shù)倍分頻器的實(shí)現(xiàn)非常簡單,只需要一個計(jì)數(shù)器進(jìn)行計(jì)數(shù)就能實(shí)現(xiàn)。如需要N分頻器(N為偶數(shù)),就可以由待分頻的時(shí)鐘觸發(fā)計(jì)數(shù)器進(jìn)行計(jì)數(shù),當(dāng)計(jì)數(shù)器從0計(jì)數(shù)到N/2-1時(shí),將輸出時(shí)鐘進(jìn)行翻轉(zhuǎn),并給計(jì)數(shù)器一個復(fù)位信號,以使下一個時(shí)鐘開始從零計(jì)數(shù)。以此循環(huán),就可以實(shí)現(xiàn)偶數(shù)倍分頻。以10分頻為例,相應(yīng)的verilog代碼如下:

regclk_div10;

reg [2:0]cnt;

always@(posedge clk or posedge rst) begin

if(rst)begin //復(fù)位

cnt<=0;

clk_div10<=0;

end

elseif(cnt==4) begin

cnt<=0; //清零

clk_div10<=~clk_div10; //時(shí)鐘翻轉(zhuǎn)

end

else

cnt<=cnt+1;

end

2.2 奇數(shù)倍分頻

奇數(shù)倍分頻因占空比不同,主要有以下兩種方法。對于非50%占空比的分頻,與偶數(shù)倍分頻類似,只需要一個計(jì)數(shù)器就能實(shí)現(xiàn)特定占空比的時(shí)鐘分頻。如需要1/11占空比的十一分頻時(shí)鐘,可以在計(jì)數(shù)值為9和10時(shí)均進(jìn)行時(shí)鐘翻轉(zhuǎn),該方法也是產(chǎn)生抽樣脈沖的有效方法。相應(yīng)的verilog代碼如下:

always @(posedge clk or posedge rst) begin

if(rst)begin //復(fù)位

cnt<=0;

clk_div11<=0;

end

elseif(cnt==9) begin

clk_div11<=~clk_div11; //時(shí)鐘翻轉(zhuǎn)

cnt<=cnt+1; //繼續(xù)計(jì)數(shù)

end

elseif(cnt==10) begin

clk_div11<=~clk_div11; //時(shí)鐘翻轉(zhuǎn)

cnt<=0; //計(jì)數(shù)清零

end

else

cnt<=cnt+1;

end

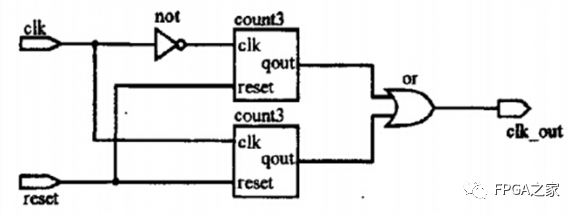

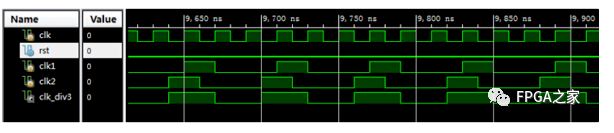

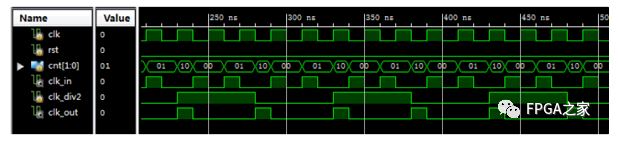

對于50%奇數(shù)分頻器的設(shè)計(jì),用到的思維是錯位半個時(shí)鐘并相或運(yùn)算。具體實(shí)現(xiàn)步驟如下:分別利用待分頻時(shí)鐘的上升沿與下降沿進(jìn)行((N-1)/2)/N分頻,最后將這兩個時(shí)鐘進(jìn)行或運(yùn)算即可。以三分頻為例,相應(yīng)的電路原理圖和時(shí)序仿真圖如圖1和圖2所示,相應(yīng)代碼如下:

reg clk1;

reg[1:0]cnt1;

always@(posedge clk or posedge rst) begin

if(rst)begin //復(fù)位

cnt1<=0;

clk1<=0;

end

elseif(cnt1==1) begin

clk1<=~clk1; //時(shí)鐘翻轉(zhuǎn)

cnt1<=cnt1+1; //繼續(xù)計(jì)數(shù)

end

elseif(cnt1==2) begin

clk1<=~clk1; //時(shí)鐘翻轉(zhuǎn)

cnt1<=0; //計(jì)數(shù)清零

end

else

cnt1<=cnt1+1;

end

reg clk2;

reg[1:0]cnt2;

always@(negedge clk or posedge rst) begin

if(rst)begin //復(fù)位

cnt2<=0;

clk2<=0;

end

elseif(cnt2==1) begin

clk2<=~clk2; //時(shí)鐘翻轉(zhuǎn)

cnt2<=cnt2+1; //繼續(xù)計(jì)數(shù)

end

elseif(cnt2==2) begin

clk2<=~clk2; //時(shí)鐘翻轉(zhuǎn)

cnt2<=0; //計(jì)數(shù)清零

end

else

cnt2<=cnt2+1;

end

assignclk_div3=clk1 | clk2; //或運(yùn)算

圖1 50%占空比的三分頻電路原理圖

圖2 50%占空比的三分頻時(shí)序仿真圖

3、小數(shù)倍分頻器的設(shè)計(jì)

3.1 半整數(shù)分頻器

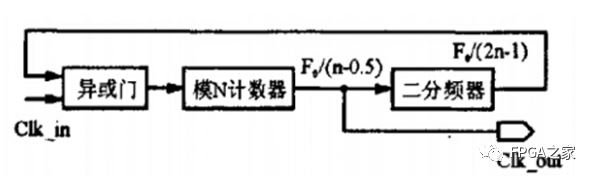

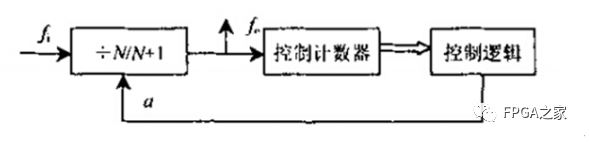

半整數(shù)N+0.5分頻器設(shè)計(jì)思路:首先進(jìn)行模N+1的計(jì)數(shù),在計(jì)數(shù)到N時(shí),將輸出時(shí)鐘賦值為1,而當(dāng)回到計(jì)數(shù)0時(shí),又賦值為0,這樣,當(dāng)計(jì)數(shù)值為N時(shí),輸出時(shí)鐘才為1。因此,只要保持計(jì)數(shù)值N為半個時(shí)鐘周期即是該設(shè)計(jì)的關(guān)鍵。從中可以發(fā)現(xiàn)。因?yàn)橛?jì)數(shù)器是通過時(shí)鐘上升沿計(jì)數(shù),故可在計(jì)數(shù)為N時(shí)對計(jì)數(shù)觸發(fā)時(shí)鐘進(jìn)行翻轉(zhuǎn),那么,時(shí)鐘的下降沿就變成了上升沿。即在計(jì)數(shù)值為N期間的時(shí)鐘下降沿變成了上升沿。也就是說,計(jì)數(shù)值N只保持了半個時(shí)鐘周期。由于時(shí)鐘翻轉(zhuǎn)下降沿變成上升沿,因此,計(jì)數(shù)值變?yōu)?。所以,每產(chǎn)生一個N+0.5分頻時(shí)鐘的周期,觸發(fā)時(shí)鐘都要翻轉(zhuǎn)一次。圖3給出了通用半整數(shù)分頻器的電路原理圖。以2.5倍分頻為例,相應(yīng)的電路verilog代碼如下,時(shí)序仿真圖如圖4所示。

//異或運(yùn)算

assignclk_in=clk^clk_div2;

//模3計(jì)數(shù)器

reg clk_out;

reg [1:0]cnt;

always@(posedge clk_in or posedge rst) begin

if(rst)begin //復(fù)位

cnt<=0;

clk_out<=0;

end

elseif(cnt==1) begin

clk_out<=~clk_out; //時(shí)鐘翻轉(zhuǎn)

cnt<=cnt+1; //繼續(xù)計(jì)數(shù)

end

elseif(cnt==2) begin

clk_out<=~clk_out; //時(shí)鐘翻轉(zhuǎn)

cnt<=0; //計(jì)數(shù)清零

end

else

cnt<=cnt+1;

end

//2分頻

reg clk_div2;

always@(posedge clk_out or posedge rst) begin

if(rst) clk_div2<=0; //復(fù)位

else clk_div2=~clk_div2;

end

圖3 通用半整數(shù)分頻器的電路原理圖

圖4 2.5倍分頻器時(shí)序仿真圖

3.2 任意小數(shù)分頻器

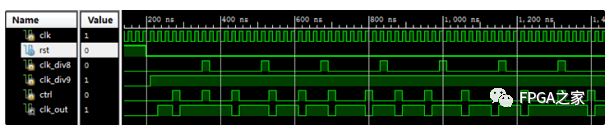

小數(shù)分頻器的實(shí)現(xiàn)方法有很多中,但其基本原理都一樣的,即在若干個分頻周期中采取某種方法使某幾個周期多計(jì)或少計(jì)一個數(shù),從而在整個計(jì)數(shù)周期的總體平均意義上獲得一個小數(shù)分頻比。一般而言,這種分頻由于分頻輸出的時(shí)鐘脈沖抖動很大,故在設(shè)計(jì)中的使用已經(jīng)非常少。但是,這也是可以實(shí)現(xiàn)的。以8.7倍分頻為例,本文僅僅給出雙模前置小數(shù)分頻原理的verilog代碼及其仿真圖(如圖6),具體原理可以參考劉亞海的《基于FPGA的小數(shù)分頻器的實(shí)現(xiàn)》以及毛為勇的《基于FPGA的任意小數(shù)分頻器的設(shè)計(jì)》。

圖5 小數(shù)分頻器的電路原理圖

//8分頻

reg clk_div8;

reg[2:0]cnt_div8;

always@(posedge clk or posedge rst) begin

if(rst)begin //復(fù)位

clk_div8<=0;

cnt_div8<=0;

end

elseif(cnt_div8==3'd7) begin

clk_div8<=1; //置1

cnt_div8<=0;

end

elseif(cnt_div8==3'd0) begin

clk_div8<=0; //置0

cnt_div8<=cnt_div8+1;

end

else

cnt_div8<=cnt_div8+1;

end

//9分頻

reg clk_div9;

reg[3:0]cnt_div9;

always@(posedge clk or posedge rst) begin

if(rst)begin //復(fù)位

clk_div9<=0;

cnt_div9<=0;

end

elseif(cnt_div9==3'd8) begin

clk_div9<=1; //置1

cnt_div9<=0;

end

elseif(cnt_div9==3'd0) begin

clk_div9<=0; //置0

cnt_div9<=cnt_div9+1;

end

else

cnt_div9<=cnt_div9+1;

end

//控制信號

parameterDiv8Num=3;

reg ctrl;

reg[3:0]AddValue;

always@(posedge clk or posedge rst) begin

if(rst)begin //復(fù)位

ctrl<=0;

AddValue<=10-7;

end

elseif(AddValue<10) begin

ctrl<=0;

AddValue<=AddValue+Div8Num;

end

else begin

ctrl<=1;

AddValue<=AddValue-10;

end

end

//選擇輸出

reg clk_out;

always @(ctrlor posedge clk or posedge rst) begin

if(rst) clk_out<=0; //復(fù)位

elseif(ctrl) clk_out<=clk_div8;

elseclk_out<=clk_div9;

end

圖6 8.7分頻器的時(shí)序仿真圖

4、總結(jié)分頻器是FPGA的基礎(chǔ),而且在FPGA邏輯電路設(shè)計(jì)的時(shí)候是經(jīng)常使用的,希望大家對以上的整數(shù)倍分頻和半整數(shù)倍分頻能熟練掌握。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<