前言

在鎖相環(huán)PLL、DLL和時鐘數(shù)據(jù)恢復(fù)電路CDR等電路的應(yīng)用中,人們普遍要求輸出時鐘信號有50%的占空比,以便在時鐘上升及下降沿都能夠采樣數(shù)據(jù),最大限度地提高數(shù)據(jù)傳輸?shù)乃俣取榱诉_到這一需求,我們經(jīng)常需要在時鐘的輸出加入脈寬調(diào)整電路來得到一個占空比盡可能達到50%的時鐘信號。

近年來誕生了許多種類的脈寬調(diào)整電路。這些電路大致可以分為以下三類:第一類最為簡單,即采用2分頻器產(chǎn)生占空比為50%的時鐘,2分頻器并不是專為調(diào)整占空比而采用的,但的確達到了這一需求;第二類通過負反饋機制,采用數(shù)字或模擬控制,調(diào)整信號占空比,這類電路最主要考慮的是系統(tǒng)穩(wěn)定性;最后一種是采用復(fù)雜數(shù)字算法的占空比調(diào)整電路,其實現(xiàn)相對比較復(fù)雜。因此本文主要分析設(shè)計前兩種類型的脈寬調(diào)整電路。

2分頻器作為脈寬調(diào)整電路

絕大多數(shù)PLL中使用2分頻prescaler電路處理VCO輸出的高頻信號,既實現(xiàn)了反饋路徑上的預(yù)分頻要求,降低了后續(xù)反饋分頻電路的工作頻率和功耗;又實現(xiàn)了對輸出信號脈寬的調(diào)整,基本滿足了50%占空比的要求。但其最大的缺點在于減少了壓控振蕩器VCO一半的輸出信號范圍,對于高頻信號的50%占空比需求,這一缺點體現(xiàn)得比較明顯。

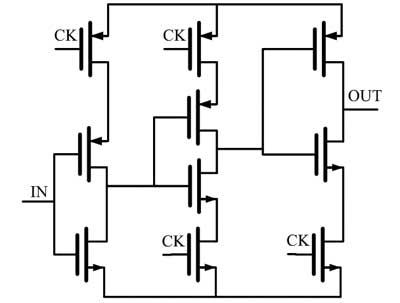

通常我們采用靜態(tài)D觸發(fā)器實現(xiàn)2分頻,為了實現(xiàn)在高頻工作時降低功耗,現(xiàn)在越來越多采用動態(tài)邏輯電路實現(xiàn)2分頻。圖1是一種傳統(tǒng)的九管實現(xiàn)的動態(tài)2分頻器。當時鐘¢為低電平時,第一級時鐘開關(guān)導(dǎo)通,采樣輸入信號,這時第二級輸出的高電平保證了該電路的即時輸出是前一次采樣保持得到的信號,該信號電荷儲存于輸出節(jié)點的寄生電容。由于現(xiàn)代CMOS工藝已經(jīng)進入深亞微米階段,晶體管的漏電流現(xiàn)象越發(fā)明顯,因此,該電路正常工作的頻率不能太低。當¢變?yōu)楦唠娖胶螅谝患墑偛潘蓸拥男盘栒_到達第三級的輸入端,¢的高電平使得這一級成為普通反相器,實現(xiàn)了觸發(fā)器的功能。由于采用了動態(tài)機制,利用寄生電容采樣保持信號,減少了直流通路,降低了功耗,與靜態(tài)邏輯實現(xiàn)方法相比,所用晶體管數(shù)量大大減少。該電路設(shè)計中,主要考慮時鐘MOS開關(guān)的導(dǎo)通電阻和開關(guān)速度的折中以及信號上升下降時間的大致匹配。為提高該電路的速度,可以按照圖2所示改進,與圖1電路相比,時鐘MOS開關(guān)更靠近電地,因此速度更快。對圖2電路仿真結(jié)果表明,該電路最高工作頻率可以達到12GHz。

圖1 傳統(tǒng)的動態(tài)觸發(fā)器

圖2 改進的動態(tài)觸發(fā)器

負反饋脈寬調(diào)整電路

同鎖相環(huán)電路利用負反饋機制鎖定相位的原理類似,我們同樣可以利用負反饋機制構(gòu)建簡單系統(tǒng)來調(diào)整信號占空比。該系統(tǒng)主要有以下幾個模塊構(gòu)成:壓控脈寬調(diào)整器、脈寬電壓轉(zhuǎn)換器和電壓比較器等。系統(tǒng)模塊圖如圖3所示。

圖3 負反饋脈寬調(diào)整電路模塊

壓控脈寬調(diào)整器可由壓控延時線VCDL和鑒相器PD組成。簡單的VCDL可以由一串反相器構(gòu)成,其輸出信號是輸入信號的延時,延時大小由控制電壓VC決定;鑒相器PD可由靜態(tài)RS觸發(fā)器構(gòu)成。兩個同頻存在延時的信號輸入鑒相器后,檢測的是兩信號上升沿之差,即產(chǎn)生了脈寬與延時成線性關(guān)系(延時小于一個周期)的同頻輸出,延時越長(在一個周期范圍內(nèi)),則PD輸出信號的占空比越大。因此,要實現(xiàn)寬范圍信號占空比的調(diào)節(jié),重要的是實現(xiàn)VCDL的寬范圍。

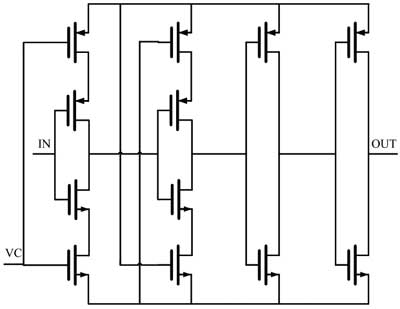

另外一種更為簡單的壓控脈寬調(diào)整器是脈寬伸縮電路,如圖4所示。該電路通過調(diào)整信號不同的上升/下降延時達到調(diào)整占空比的目的。圖中靠近電地的MOS管電流源的電流大小由控制電平VC決定。控制電壓較大時,NMOS電流鏡的電流大于PMOS電流源中的電流,信號上升比下降要慢,反之亦然。因此,改變控制電壓的大小,即實現(xiàn)了信號上升下降延時的不同,從而實現(xiàn)了脈寬的調(diào)節(jié)。

圖4 壓控脈寬調(diào)整器

設(shè)計該電路時,傳輸信號反相器中的MOS管采用最小特征尺寸,并保證較大的寬度,使MOS管開關(guān)迅速,提高電路的工作頻率;作為電流源使用的MOS管,為減少溝長調(diào)制效應(yīng),晶體管的長度應(yīng)該比較大,這樣對減少噪聲也有幫助。另外要注意的是,當控制電壓處于電源電壓一半時,調(diào)整P、N電流源電流基本一致,這一要求確定了它們的相對寬長比,對擴大電路工作范圍有重要的作用。由于電路調(diào)整了信號上升/下降的延時,有可能在高頻應(yīng)用時會對信號的完整性有所傷害,因此必須在該電路的輸出加上緩沖器,根據(jù)負載決定緩沖器的驅(qū)動能力。為了適應(yīng)后續(xù)模塊比較的要求,需要產(chǎn)生相位互補信號。該電路可由兩條反相器鏈組成。由于正相路徑比反相路徑少一級,為保證信號的相位互補,我們對正相路徑的負載增加MOS電容,通過增大正相路徑延時來達到互補的要求。

脈寬調(diào)整電路中的另一個模塊是脈寬電壓轉(zhuǎn)換器,它的功能是產(chǎn)生與脈寬成線性關(guān)系的電壓信號。本設(shè)計中采用兩個對稱的轉(zhuǎn)換器實現(xiàn)對壓控脈寬調(diào)整器輸出互補信號的脈寬比較。如果輸出時鐘是50%占空比,其互補信號脈寬基本一致,則兩轉(zhuǎn)換器的輸出電平也是基本相同的。由于考慮的是電壓相對值,因此脈寬電壓轉(zhuǎn)換過程中產(chǎn)生的一些非理想因素,比如充放電流不匹配、電荷共享等,可以忽略。該轉(zhuǎn)換器的基本原理是由脈寬控制電流源對電容充放電。在脈寬比較極端的情況時,該電路也能夠正常反映當前信號占空比的正確關(guān)系。

系統(tǒng)中另一個模塊是電壓比較器,它在整個負反饋系統(tǒng)中起著重要的作用。本設(shè)計中采用跨導(dǎo)運算放大器OTA對脈寬電壓轉(zhuǎn)換器輸出的電壓值進行比較,并產(chǎn)生壓控脈寬調(diào)整器所需的控制電壓VC,構(gòu)成整個系統(tǒng)的負反饋回路。該OTA需要較高的直流增益和較大的帶寬。為了更好地保證整個環(huán)路的穩(wěn)定性,放大器采用一級折疊共源共柵結(jié)構(gòu)。圖5為該放大器的電路圖。

圖5 折疊共源共柵跨導(dǎo)運算放大器

當壓控脈寬調(diào)整器輸出信號具有約50%占空比時,轉(zhuǎn)換器的輸出電壓維持在較小的值(考慮充放電荷大致相同),因此,采用PMOS管作為放大器的差分輸入符合輸入范圍的要求。為了擴大輸出范圍,放大器采用了寬范圍Cascode電流鏡作為有源負載。

經(jīng)過仿真可得,該放大器直流增益達65dB,完全滿足系統(tǒng)要求。為了保證反饋環(huán)路穩(wěn)定以及減少控制電壓上的紋波(ripple),放大器的負載電容應(yīng)取得較大一些,以降低主極點頻率。考慮面積方面的因素,該電容可以采用NMOS電容,這種電容的單位面積電容值比其他類型的集成電容都要大的多。該電容的缺點是電容值受工藝、電壓等因素變化較大,而且漏電隨柵氧化層厚度減小而增大,但在此處做相位補償和濾波之用,可以忽略這些缺點。

整個系統(tǒng)中最重要的是系統(tǒng)環(huán)路穩(wěn)定性的問題,該閉環(huán)系統(tǒng)的環(huán)路增益是:Loop gain="1/"(1+s/p1)×A0/(1+s/p2)只要放大器的負載電容足夠大(大約30pF),就可以使環(huán)路有足夠的相位裕度保證整個閉環(huán)系統(tǒng)的穩(wěn)定。典型的二階系統(tǒng)控制電壓穩(wěn)定曲線如圖6所示。在脈寬電壓轉(zhuǎn)換器中,我們可以采用類似于電賀泵的電容充放電結(jié)構(gòu),也可以采用本次設(shè)計中采用的簡單低通濾波器結(jié)構(gòu)。考慮到這兩種結(jié)構(gòu)所引入的極點p1的位置不同,因此后者更加容易穩(wěn)定。

圖6 典型的二階系統(tǒng)控制電壓穩(wěn)定曲線

該系統(tǒng)在SMIC 180nm數(shù)字工藝下,采用Cadence公司的Spectre仿真器通過仿真,工作頻率范圍100MHz~1.5GHz,穩(wěn)定時間約在1~3μs,有效輸入占空比為30%~70%,輸出占空比誤差在0.5%之內(nèi),基本滿足了寬范圍應(yīng)用中所需的50%占空比設(shè)計要求。

該系統(tǒng)的誤差主要來自環(huán)路有限的增益以及控制電壓上的紋波抖動。另外,保證壓控脈寬調(diào)整器足夠的范圍和線性度,都對提高系統(tǒng)的性能有重要的作用。因此在壓控脈寬調(diào)整器中采用VCDL結(jié)構(gòu)比直接采用脈寬伸縮電路有優(yōu)勢,但脈寬伸縮結(jié)構(gòu)實現(xiàn)更為簡單。