本文是第一篇詳細(xì)介紹HBM在FPGA上性能實(shí)測(cè)結(jié)果的頂會(huì)論文(FCCM2020,Shuhai: Benchmarking High Bandwidth Memory on FPGAs),作者是浙江大學(xué)王則可博士!感謝王則可博士允許本公眾號(hào)轉(zhuǎn)載該論文的中文譯文。論文給出了FPGA上HBM可提供高達(dá)425GB/s內(nèi)存帶寬的實(shí)測(cè)結(jié)果!結(jié)合前兩天,本公眾號(hào)轉(zhuǎn)發(fā)老石的文章,目前采用Chiplet技術(shù)的光口速率可以達(dá)到驚人的2Tbps。而本文介紹的同樣采用Chiplet技術(shù)的HBM,訪存帶寬高達(dá)425GB/s,那么采用這樣光口和緩存的網(wǎng)卡會(huì)是一種怎樣的高性能呢?對(duì)NIC或者Switch內(nèi)部的總線帶寬又有怎樣的要求呢?我們期待著能夠用2Tbps接口和HBM技術(shù)的NIC或者Switch的出現(xiàn)。

作者:浙江大學(xué)博士生導(dǎo)師王則可博士。

隨著高帶寬內(nèi)存(HBM)的發(fā)展,F(xiàn)PGA正變得越來(lái)越強(qiáng)大,HBM 給了FPGA 更多能力去緩解再一些應(yīng)用中遇到的內(nèi)存帶寬瓶頸和處理更多樣的應(yīng)用。然而,HBM 的性能表現(xiàn)我們了解地還不是特別精準(zhǔn),尤其是在 FPGA 平臺(tái)上。這篇文章我們將會(huì)在HBM 的說(shuō)明書(shū)和它的實(shí)際表現(xiàn)之間建立起橋梁。我們使用的是一款非常棒的 FPGA,Xilinx ALveo U280,有一個(gè)兩層的HBM 子系統(tǒng)。在最后,我們提出了豎亥,一款讓我們測(cè)試出所有HBM 基礎(chǔ)性能的基準(zhǔn)測(cè)試工具。基于FPGA 的測(cè)試平臺(tái)相較于CPU/GPU 平臺(tái)來(lái)說(shuō)會(huì)更位準(zhǔn)確,因?yàn)樵肼晻?huì)更少,后者有著復(fù)雜的控制邏輯和緩存層次。我們觀察到 1)HBM 提供高達(dá)425 GB/s 的內(nèi)存帶寬,2)如何使用HBM 會(huì)給性能表現(xiàn)帶來(lái)巨大的影響,這也印證了揭開(kāi) HBM 特性的重要性,這可以讓我們選擇最佳的使用方式。作為對(duì)照,我們同樣將豎亥應(yīng)用在DDR4上來(lái)展現(xiàn)DDR4 和HBM 的不同。豎亥可以被輕松部署在其他FPGA 板卡上,我們會(huì)將豎亥開(kāi)源,造福社會(huì)。

引言

現(xiàn)代計(jì)算機(jī)系統(tǒng)的計(jì)算能力隨著 CMOS技術(shù)的發(fā)展持續(xù)提升,典型的例子就是應(yīng)用更多的核心在同樣的區(qū)域中或者增加額外的功能到核里面去(SIMD、AVX、SGX等)。與此相反,DRAM內(nèi)存的帶寬發(fā)展地十分緩慢。因此處理器和內(nèi)存之間的差距越來(lái)越大,并且隨著多核設(shè)計(jì)而變得更嚴(yán)重。HBM被提出用于提供高得多的帶寬能力。HBM2 能提供高達(dá)900 GB/s 的內(nèi)存帶寬。 與同一代GPU相比,F(xiàn)PGA 帶寬能力要低幾個(gè)數(shù)量級(jí),傳統(tǒng)的FPGA有兩個(gè)DRAM內(nèi)存通道,每個(gè)提供19.2GB/s的內(nèi)存帶寬。因此FPGA不能完成很多對(duì)帶寬能力要求高的應(yīng)用。因此Xilinx將HBM引用到新一代FPGA中去。HBM有潛力成為改變目前局面的特性。 盡管有著潛力去解決處理器和內(nèi)存間的差距,應(yīng)用HBM到FPGA上還是有很多阻礙。HBM的特性不為人們所了解。

盡管和DRAM有著相同的die,HBM的特性和前者完全不同。Xilinx的HBM子系統(tǒng)也引入了很多新特性例如switch。Switch的特性同樣不為我們所了解。這些東西都會(huì)阻礙開(kāi)發(fā)者利用FPGA上的HBM。 在最后我們提出了豎亥,一個(gè)可以用來(lái)測(cè)試HBM特性的基準(zhǔn)測(cè)試工具。據(jù)我們所致,豎亥是第一個(gè)系統(tǒng)性測(cè)試FPGA上的HBM的測(cè)試平臺(tái)。我們通過(guò)以下四個(gè)方面來(lái)證明豎亥的用處。

F1:HBM提供巨大的內(nèi)存帶寬:在我們的測(cè)試平臺(tái)上,HBM提供高達(dá)425 GB/s的內(nèi)存帶寬,比傳統(tǒng)使用兩個(gè)DDR4來(lái)說(shuō)要高一個(gè)數(shù)量級(jí)。雖然只有GPU的一半,但是這對(duì)FPGA來(lái)說(shuō)也是一個(gè)巨大的進(jìn)步。

F2:地址映射策略很重要:不同的地址映射策略會(huì)帶來(lái)數(shù)量級(jí)的速度差異。這也意味著要根據(jù)應(yīng)用的不同選取不同的映射策略。

F3:HBM延時(shí)要比DDR4高很多:HBM和FPGA的聯(lián)系是通過(guò)transceiver,帶來(lái)了額外的糾錯(cuò)碼和串行并行轉(zhuǎn)換的開(kāi)銷。豎亥測(cè)試出在頁(yè)命中情況下,HBM的延時(shí)是122.2ns,而DDR4僅為73.3ns。

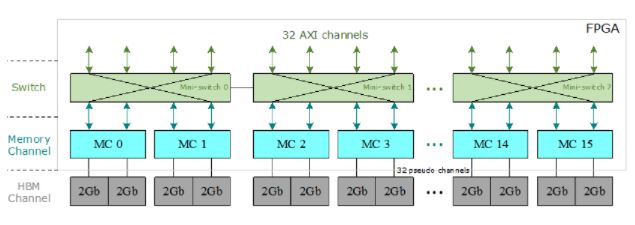

圖1:Xilinx HBM子系統(tǒng)架構(gòu)

F4:FPGA可以更精準(zhǔn)地測(cè)量:我們將豎亥直接連接HBM模塊,使得更容易解釋測(cè)量結(jié)果,而使用CPU/GPU會(huì)引出更多的噪聲,例如緩存的影響。因此我們主張豎亥是一個(gè)更好的選項(xiàng)來(lái)測(cè)量?jī)?nèi)存。

背景

HBM芯片采用了最新的IC封裝技術(shù),例如直通硅通孔(TSV),堆疊式DRAM和2.5D封裝[13],[18]。HBM的基本結(jié)構(gòu)由底部的基本邏輯芯片和頂部堆疊的4或8核心DRAM芯片組成。所有管芯均通過(guò)TSV互連。Xilinx在FPGA內(nèi)部集成了兩個(gè)HBM堆棧和一個(gè)HBM控制器。每個(gè)HBM堆棧都分為八個(gè)獨(dú)立的存儲(chǔ)通道,其中每個(gè)存儲(chǔ)通道又分為兩個(gè)64位偽通道。如圖1所示,只允許偽通道訪問(wèn)與其關(guān)聯(lián)的HBM通道,該通道具有自己的內(nèi)存地址區(qū)域。Xilinx的HBM子系統(tǒng)具有16個(gè)存儲(chǔ)通道,32個(gè)偽通道和32個(gè)HBM通道。 在16個(gè)存儲(chǔ)通道的頂部,有32個(gè)與用戶邏輯交互的AXI通道。每個(gè)AXI通道均遵循標(biāo)準(zhǔn)AXI3協(xié)議[44],以向FPGA程序員提供經(jīng)過(guò)驗(yàn)證的標(biāo)準(zhǔn)化接口。每個(gè)AXI通道都與一個(gè)HBM通道(或偽通道)相關(guān)聯(lián),因此每個(gè)AXI通道僅被允許訪問(wèn)其自己的內(nèi)存區(qū)域。為了使每個(gè)AXI通道都能訪問(wèn)整個(gè)HBM空間,Xilinx引入了在32個(gè)AXI通道和32個(gè)偽通道之間的switch[41],[44]。但是,由于其巨大的資源消耗,該switch尚未完全實(shí)現(xiàn)。相反,Xilinx提供了八個(gè)小型switch,其中每個(gè)小型switch為四個(gè)AXI通道及其相關(guān)的偽通道提供服務(wù),并且在每個(gè)AXI通道都可以訪問(wèn)同一小型switch中的任何偽通道,該小型switch被完全實(shí)現(xiàn)。具有相同的延遲和吞吐量。此外,兩個(gè)相鄰的微型switch之間有兩個(gè)雙向連接,用于全局尋址。

豎亥的基本架構(gòu)

在本節(jié)中,我們介紹設(shè)計(jì)方法,然后是豎亥的軟件和硬件組件。

A.設(shè)計(jì)方法論

在本小節(jié)中,我們總結(jié)了兩個(gè)具體挑戰(zhàn)C1和C2,然后介紹豎亥如何來(lái)應(yīng)對(duì)這兩個(gè)挑戰(zhàn)。

C1:高層洞察力。在某種意義上,使我們的基準(zhǔn)測(cè)試框架對(duì)FPGA程序員有意義是至關(guān)重要的,因?yàn)槲覀儜?yīng)該輕松地向FPGA程序員提供更詳盡的解釋,而不是僅僅令人費(fèi)解的內(nèi)存時(shí)序參數(shù)(例如行預(yù)充電時(shí)間TRP),這可用于改善FPGA上HBM存儲(chǔ)器的使用。

C2:易于使用。 在對(duì)FPGA進(jìn)行基準(zhǔn)測(cè)試時(shí),可能需要做一些小改動(dòng)才能重新配置FPGA,很難實(shí)現(xiàn)易用性。因此,我們打算最大程度地減少重新配置的工作,以使在基準(zhǔn)測(cè)試任務(wù)之間無(wú)需重新配置FPGA。換句話說(shuō),我們的基準(zhǔn)測(cè)試框架應(yīng)該允許我們將一個(gè)FPGA實(shí)例用于大量的基準(zhǔn)測(cè)試任務(wù),而不僅僅是一個(gè)任務(wù)。

我們的方法。我們使用豎亥應(yīng)對(duì)上述兩個(gè)挑戰(zhàn)。為了解決第一個(gè)挑戰(zhàn)C1,豎亥允許直接分析FPGA程序員使用的典型存儲(chǔ)器訪問(wèn)模式的性能特征,并提供整體性能的詳盡說(shuō)明。為了解決第二個(gè)挑戰(zhàn),即C2,豎亥使用基準(zhǔn)電路的運(yùn)行時(shí)參數(shù)化功能來(lái)覆蓋各種基準(zhǔn)測(cè)試任務(wù),而無(wú)需重新配置FPGA。通過(guò)基準(zhǔn)測(cè)試中實(shí)現(xiàn)的訪問(wèn)模式,我們可以揭示FPGA上HBM和DDR4的基本特性。 豎亥采用基于兩個(gè)組件的軟件-硬件協(xié)同設(shè)計(jì)方法:軟件組件(III-B小節(jié))和硬件組件(III-C小節(jié))。軟件組件的主要作用是在運(yùn)行時(shí)參數(shù)方面為FPGA程序員提供靈活性。利用這些運(yùn)行時(shí)參數(shù),在對(duì)HBM和DDR4進(jìn)行基準(zhǔn)測(cè)試時(shí),我們無(wú)需頻繁地重新配置FPGA。硬件組件的主要作用是保證性能。更準(zhǔn)確地說(shuō),豎亥應(yīng)該能夠在FPGA上展現(xiàn)HBM存儲(chǔ)器在最大可實(shí)現(xiàn)的存儲(chǔ)器帶寬和最小可實(shí)現(xiàn)的延遲方面的性能潛力。為此,基準(zhǔn)測(cè)試電路本身不能在任何時(shí)候成為瓶頸。

B.軟件組件 豎亥的軟件組件旨在提供用戶友好的接口,以便FPGA開(kāi)發(fā)人員可以輕松地使用豎亥來(lái)對(duì)HBM存儲(chǔ)器進(jìn)行基準(zhǔn)測(cè)試并獲得相關(guān)的性能特征。為此,我們介紹了一種廣泛用于FPGA編程的存儲(chǔ)器訪問(wèn)模式:重復(fù)順序遍歷(RST),如圖2所示。

圖2:在豎亥中使用的內(nèi)存訪問(wèn)模式

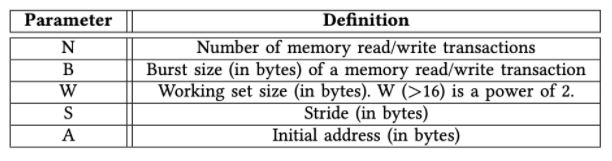

RST模式遍歷一個(gè)存儲(chǔ)區(qū)域,一個(gè)數(shù)據(jù)陣列按順序存儲(chǔ)數(shù)據(jù)元素。RST重復(fù)掃描起始地址為A的大小為W的存儲(chǔ)區(qū)域,并且每次讀取步長(zhǎng)為S字節(jié)的B個(gè)字節(jié),其中B和S為2的冪。在我們測(cè)試的FPGA上,訪問(wèn)大小B應(yīng)為由于HBM / DDR4存儲(chǔ)器應(yīng)用程序數(shù)據(jù)寬度的限制,對(duì)于HBM(或DDR4),其值不得小于32(或64)。步幅S不應(yīng)大于工作集大小W。參數(shù)匯總在表I中。我們計(jì)算出RST發(fā)出的第i個(gè)存儲(chǔ)器讀/寫(xiě)事務(wù)的地址T [i],如公式1所示。可以使用簡(jiǎn)單的算法來(lái)實(shí)現(xiàn)計(jì)算,從而減少了FPGA資源的數(shù)量,并可能實(shí)現(xiàn)更高的頻率。盡管這公式非常簡(jiǎn)單,但是它能幫助我們了解FPGA上的HBM和DDR。

表格1:運(yùn)行時(shí)參數(shù)總結(jié)

T[i] = A + (i × S)%W 公式(1)

C.硬件組件 豎亥的硬件組件由一個(gè)PCIe模塊,M個(gè)延遲模塊,一個(gè)參數(shù)模塊和M個(gè)引擎模塊組成,如圖3所示。在下面,我們討論每個(gè)模塊的實(shí)現(xiàn)細(xì)節(jié)。

1)引擎模塊:我們直接將實(shí)例化的引擎模塊連接到AXI通道,以便引擎模塊直接服務(wù)于AXI接口,例如AXI3和AXI4 [2],[42],它由基礎(chǔ)內(nèi)存IP核提供,HBM和DDR4。AXI接口包含五個(gè)不同的通道:讀取地址(RA),讀取數(shù)據(jù)(RD),寫(xiě)入地址(WA),寫(xiě)入數(shù)據(jù)(WD)和寫(xiě)入響應(yīng)(WR)[42]。此外,引擎模塊的輸入時(shí)鐘正是來(lái)自相關(guān)AXI通道的時(shí)鐘。例如,在對(duì)HBM進(jìn)行基準(zhǔn)測(cè)試時(shí),引擎模塊的時(shí)鐘頻率為450MHz,因?yàn)槠銩XI通道最多允許450MHz。使用同一時(shí)鐘有兩個(gè)好處。首先,跨不同時(shí)鐘區(qū)域所需的FIFO不會(huì)引入額外的噪聲,例如更長(zhǎng)的延遲。其次,引擎模塊能夠容納其關(guān)聯(lián)的AXI通道,不會(huì)導(dǎo)致內(nèi)存帶寬容量的低估。 用Verilog編寫(xiě)的引擎模塊由兩個(gè)獨(dú)立的模塊組成:寫(xiě)入模塊和讀取模塊。寫(xiě)模塊為三個(gè)與寫(xiě)相關(guān)的通道WA,WD和WR提供服務(wù),而讀模塊為兩個(gè)與讀相關(guān)的通道RA和RD提供服務(wù)。

寫(xiě)模塊。該模塊包含一個(gè)狀態(tài)機(jī),該狀態(tài)機(jī)可以從CPU執(zhí)行內(nèi)存寫(xiě)入任務(wù)。該任務(wù)具有初始地址A,寫(xiě)入數(shù)N,訪問(wèn)大小B,步幅S和工作集大小W。公式1中指定了每個(gè)存儲(chǔ)器寫(xiě)事務(wù)的地址。該模塊還探測(cè)WR通道,以驗(yàn)證動(dòng)態(tài)存儲(chǔ)器寫(xiě)的工作已成功完成。

讀取模塊。讀取模塊包含一個(gè)狀態(tài)機(jī),該狀態(tài)機(jī)可以從CPU中執(zhí)行內(nèi)存讀取任務(wù)。該任務(wù)具有初始地址A,讀取事務(wù)數(shù)N,訪問(wèn)大小B,幅度S和工作集大小W。與寫(xiě)入模塊不同,寫(xiě)入模塊僅測(cè)量可實(shí)現(xiàn)的吞吐量,讀取模塊還測(cè)量每個(gè)模塊的延遲。當(dāng)測(cè)試速度時(shí),該模塊會(huì)一直嘗試滿足RA和RD。

圖3:總硬件架構(gòu),支持M個(gè)硬件引擎同時(shí)運(yùn)行,在我們的實(shí)驗(yàn)中,M是32

2)PCIe模塊:我們直接在時(shí)鐘頻率為250MHz的PCIe模塊中部署了用于PCI Express(PCIe)IP內(nèi)核的Xilinx DMA/橋接子系統(tǒng)。我們的PCIe驅(qū)動(dòng)程序?qū)PGA上的運(yùn)行時(shí)參數(shù)映射給用戶,以便用戶能夠使用軟件代碼直接與FPGA交互。這些運(yùn)行時(shí)參數(shù)決定存儲(chǔ)在參數(shù)模塊中的控制和狀態(tài)寄存器。

3)參數(shù)模塊:參數(shù)模塊維護(hù)運(yùn)行時(shí)參數(shù)并通過(guò)PCIe模塊與主機(jī)CPU通信,從CPU接收運(yùn)行時(shí)參數(shù)(例如S),并將吞吐量數(shù)據(jù)返回給CPU。 收到運(yùn)行時(shí)參數(shù)后,我們將使用它們來(lái)配置M個(gè)引擎模塊,每個(gè)引擎模塊都需要兩個(gè)256位控制寄存器來(lái)存儲(chǔ)其運(yùn)行時(shí)參數(shù):每個(gè)引擎模塊中的一個(gè)寄存器用于讀取模塊,另一個(gè)寄存器用于寫(xiě)入模塊。在256位寄存器中,W占用32位,S占用32位,N占用64位,B占用32位,而A占用64位。剩余的32位保留供將來(lái)使用。設(shè)置完所有引擎之后,用戶可以觸發(fā)啟動(dòng)信號(hào)以開(kāi)始吞吐量/延遲測(cè)試。 參數(shù)模塊還負(fù)責(zé)將吞吐量編號(hào)(64位狀態(tài)寄存器)返回給CPU。每個(gè)引擎模塊專用一個(gè)狀態(tài)寄存器。

4)延遲模塊:我們?yōu)閷S糜贏XI通道的每個(gè)引擎模塊實(shí)例化一個(gè)延遲模塊。等待時(shí)間模塊存儲(chǔ)大小為1024的等待時(shí)間列表,其中等待時(shí)間列表由關(guān)聯(lián)的引擎模塊寫(xiě)入并由CPU讀取。它的大小是一個(gè)綜合參數(shù)。每個(gè)包含一個(gè)8位寄存器的等待時(shí)間,指從讀取操作的發(fā)出到數(shù)據(jù)從存儲(chǔ)控制器到達(dá)操作的延遲。

實(shí)驗(yàn)設(shè)置

在本節(jié)中,我們介紹經(jīng)過(guò)測(cè)試的硬件平臺(tái)(第IV-A小節(jié))和探討的地址映射策略(第IV-B小節(jié)),然后是硬件資源消耗(第IV-C小節(jié))和我們的基準(zhǔn)測(cè)試方法(IV-D小節(jié))。

A.硬件平臺(tái) 我們?cè)赬ilinx的Alevo U280 [43]上進(jìn)行實(shí)驗(yàn),該實(shí)驗(yàn)具有兩個(gè)總?cè)萘繛?GB的HBM堆棧和兩個(gè)總?cè)萘繛?2GB的DDR4內(nèi)存通道。理論HBM內(nèi)存帶寬可以達(dá)到450 GB / s(450M * 32 * 32B / s),而DDR4內(nèi)存理論帶寬可以達(dá)到38.4GB / s(300M * 2 * 64B / s)。

B.地址映射政策 可以使用多種策略將應(yīng)用程序地址映射到內(nèi)存地址,其中不同的地址位映射到存儲(chǔ)塊,行或列地址。選擇正確的映射策略對(duì)于最大化整體內(nèi)存吞吐量至關(guān)重要。表II中匯總了為HBM和DDR4啟用的策略,其中“ xR”表示x位用于行地址,“xBG”表示x位用于存儲(chǔ)體組地址,“ xB”表示x位用于存儲(chǔ)體地址,“ xC”表示x位用于列地址。HBM和DDR4的默認(rèn)策略分別為“RGBCG”和“ RCB”。“-”代表地址串聯(lián)。如果沒(méi)有特別指定,我們始終對(duì)HBM和DDR4使用默認(rèn)的內(nèi)存地址映射策略。例如,HBM的默認(rèn)策略是RGBCG。

表格2:地址映射策略,藍(lán)色的是默認(rèn)

C.資源消耗明細(xì)

在本小節(jié)中,我們將敘述7種資源的消耗。 對(duì)HBM進(jìn)行基準(zhǔn)測(cè)試時(shí),表III列出了每個(gè)實(shí)例化模塊的確切FPGA資源消耗。我們觀察到,豎亥只需要少量的資源來(lái)實(shí)例化32個(gè)引擎模塊以及PCIe模塊等其他組件,總資源利用率不到8%。

表格3:資源消耗量

D.測(cè)試方法

我們旨在揭示豎亥使用下Xilinx FPGA上的HBM堆棧的底層細(xì)節(jié)。作為衡量標(biāo)準(zhǔn),我們?cè)诒匾獣r(shí)還分析了同一FPGA板U280上DDR4的性能特征[43]。當(dāng)我們對(duì)HBM通道進(jìn)行基準(zhǔn)測(cè)試時(shí),我們將HBM和DDR4的性能特征進(jìn)行了比較(在第五節(jié)中)。我們認(rèn)為,針對(duì)HBM通道獲得的數(shù)字可以推廣到其他計(jì)算設(shè)備,例如具有HBM內(nèi)存的CPU或GPU。在HBM內(nèi)存控制器內(nèi)部對(duì)switch進(jìn)行基準(zhǔn)測(cè)試時(shí),由于DDR4內(nèi)存控制器不包含,因此我們不與DDR進(jìn)行比較(第六節(jié))。

圖4:刷新指令帶來(lái)更高的訪問(wèn)延時(shí)周期性地出現(xiàn)在HBM和DDR4中

對(duì)HBM通道進(jìn)行基準(zhǔn)測(cè)試

在本節(jié)中,我們旨在揭示Xilinx FPGA上使用Shuhai的HBM通道的詳細(xì)信息。

A.刷新間隔的影響 當(dāng)存儲(chǔ)通道正在運(yùn)行時(shí),應(yīng)重復(fù)刷新存儲(chǔ)單元,以使每個(gè)存儲(chǔ)單元中的信息都不會(huì)丟失。在刷新周期中,不允許正常的內(nèi)存讀取和寫(xiě)入事務(wù)訪問(wèn)內(nèi)存。我們觀察到,經(jīng)歷內(nèi)存刷新周期的內(nèi)存事務(wù)比允許直接訪問(wèn)內(nèi)存芯片的普通內(nèi)存讀/寫(xiě)事務(wù)的等待時(shí)間長(zhǎng)得多。因此,我們能夠通過(guò)利用正常和非刷新內(nèi)存事務(wù)之間的內(nèi)存延遲差異來(lái)大致確定刷新間隔。特別地,我們利用豎亥來(lái)測(cè)量串行存儲(chǔ)器讀取操作的延遲。圖4說(shuō)明了B = 32,S = 64,W = 0x1000000和N = 20000的情況。我們有兩個(gè)觀察結(jié)果。首先,對(duì)于HBM和DDR4,與刷新命令一致的存儲(chǔ)器讀取事務(wù)具有顯著更長(zhǎng)的延遲,這表明需要發(fā)出足夠多的動(dòng)態(tài)存儲(chǔ)器事務(wù)來(lái)分?jǐn)偹⑿旅畹呢?fù)面影響。其次,對(duì)于HBM和DDR4,都定期計(jì)劃刷新命令,任何兩個(gè)連續(xù)刷新命令之間的間隔大致相同。

B.內(nèi)存訪問(wèn)延遲 為了準(zhǔn)確地測(cè)量?jī)?nèi)存延遲,當(dāng)內(nèi)存控制器處于“空閑”狀態(tài)時(shí),即內(nèi)存控制器中不存在其他未決內(nèi)存事務(wù)的情況下,我們利用豎亥來(lái)測(cè)量連續(xù)內(nèi)存讀取事務(wù)的延遲。以最小的延遲將請(qǐng)求的數(shù)據(jù)返回到讀取的事務(wù)。我們旨在確定三種不同狀態(tài)下的延遲:page hit、page miss、page closed。

圖5.三種狀態(tài)(page hit、page closed、page miss)的延時(shí)

PageHit(頁(yè)面命中):當(dāng)內(nèi)存事務(wù)訪問(wèn)其存儲(chǔ)區(qū)中打開(kāi)的行時(shí),將發(fā)生“頁(yè)面命中”狀態(tài),因此在訪問(wèn)列之前不需要“預(yù)充電”和“激活”命令,從而將等待時(shí)間降至最低。 PageClosed(頁(yè)面關(guān)閉):當(dāng)內(nèi)存事務(wù)訪問(wèn)其對(duì)應(yīng)存儲(chǔ)體已關(guān)閉的行時(shí),將發(fā)生“頁(yè)面關(guān)閉”狀態(tài),因此在訪問(wèn)列之前需要行AcTIvate命令。

PageMiss(頁(yè)面丟失):當(dāng)內(nèi)存事務(wù)訪問(wèn)的行與存儲(chǔ)區(qū)中的活動(dòng)行不匹配時(shí),將發(fā)生“頁(yè)面丟失”狀態(tài),因此在訪問(wèn)列之前發(fā)出了一個(gè)Precharge命令和一個(gè)AcTIvate命令,這導(dǎo)致了最大的延遲。 我們準(zhǔn)確測(cè)量B = 32,W = 0x1000000,N = 2000且S發(fā)生變化的情況下的等待時(shí)間數(shù)。直觀地講,小S導(dǎo)致?lián)糁型豁?yè)面的可能性很高,而大S可能導(dǎo)致?lián)糁型豁?yè)面錯(cuò)過(guò)頁(yè)面。在本實(shí)驗(yàn)中,我們使用兩個(gè)S值:128和128K。 我們使用情況S = 128來(lái)確定頁(yè)面命中和頁(yè)面關(guān)閉事務(wù)的等待時(shí)間。S = 128小于頁(yè)面大小,因此大多數(shù)讀取事務(wù)將訪問(wèn)一個(gè)打開(kāi)的頁(yè)面,如圖5所示。其余點(diǎn)說(shuō)明頁(yè)面關(guān)閉事務(wù)的等待時(shí)間,因?yàn)樾導(dǎo)致大量讀取特定內(nèi)存區(qū)域中的事務(wù)。我們使用S = 128K的情況來(lái)確定頁(yè)面丟失事務(wù)的等待時(shí)間。S = 128K導(dǎo)致HBM和DDR4的每個(gè)內(nèi)存事務(wù)發(fā)生頁(yè)面丟失。 總結(jié):我們?cè)诒鞩V中總結(jié)了HBM和DDR的延遲。我們有兩個(gè)觀察結(jié)果。首先,在相同的類別(如頁(yè)面點(diǎn)擊)下,HBM上的內(nèi)存訪問(wèn)延遲比DDR4上高約50納秒。這意味著當(dāng)在FPGA上運(yùn)行對(duì)延遲敏感的應(yīng)用程序時(shí),HBM可能有劣勢(shì)。其次,延遲數(shù)是準(zhǔn)確的,證明了豎亥的效率。

表格4.HBM和DDR4的內(nèi)存訪問(wèn),HBM的延時(shí)要高于DDR4

C.地址映射策略的效果

在本小節(jié)中,我們研究了不同內(nèi)存地址映射策略對(duì)可實(shí)現(xiàn)吞吐量的影響。特別地,在不同的映射策略下,我們使用步幅S和訪問(wèn)大小B來(lái)測(cè)量?jī)?nèi)存吞吐量,同時(shí)將工作集大小W(= 0x10000000)保持足夠大。圖6說(shuō)明了HBM和DDR4的不同地址映射策略的吞吐量趨勢(shì)。我們有五個(gè)觀察到的現(xiàn)象。 首先,不同的地址映射策略會(huì)導(dǎo)致明顯的性能差異。例如,圖6a說(shuō)明,當(dāng)S為1024而B(niǎo)為32時(shí),HBM的默認(rèn)策略(RGBCG)幾乎比策略(BRC)快10倍,這說(shuō)明為內(nèi)存應(yīng)用程序選擇正確的地址映射策略的重要性。 其次,即使HBM和DDR4采用相同的地址映射策略,其吞吐量趨勢(shì)也大不相同,這證明了豎亥等基準(zhǔn)平臺(tái)對(duì)評(píng)估不同的FPGA板或不同的存儲(chǔ)器的重要性。 第三,對(duì)于HBM和DDR4上的S和B的任何組合,默認(rèn)策略始終會(huì)帶來(lái)最佳性能,這表明默認(rèn)設(shè)置是合理的。 第四,較小的訪問(wèn)大小導(dǎo)致較低的存儲(chǔ)器吞吐量,如圖6a,6e所示,這意味著FPGA程序員應(yīng)增加空間局部性,以從HBM和DDR4獲得更高的存儲(chǔ)器吞吐量。 第五,大的S(> 8K)總是導(dǎo)致內(nèi)存帶寬利用率極低,這表明保持空間局部性極為重要。換句話說(shuō),不保留空間局部性的隨機(jī)內(nèi)存訪問(wèn)將遇到低內(nèi)存吞吐量。 我們得出結(jié)論,選擇正確的地址映射策略對(duì)于優(yōu)化FPGA上的存儲(chǔ)器吞吐量至關(guān)重要。

D.儲(chǔ)存組的影響 在本小節(jié)中,我們研究了存儲(chǔ)組的影響,與DDR3相比,存儲(chǔ)組是DDR4的新功能。同時(shí)訪問(wèn)多個(gè)存儲(chǔ)組有助于我們減輕DRAM時(shí)序限制的負(fù)面影響,而這種限制在幾代DRAM上并未得到改善。通過(guò)訪問(wèn)多個(gè)存儲(chǔ)組可能會(huì)獲得更高的內(nèi)存吞吐量。因此,我們使用引擎模塊來(lái)驗(yàn)證儲(chǔ)存組的效果(圖6)。我們有兩個(gè)觀察到的結(jié)果。

圖6.在所有地址映射策略下,具有不同訪問(wèn)大小和跨度的HBM通道和DDR4通道之間的內(nèi)存吞吐量比較。在本實(shí)驗(yàn)中,我們使用AXI通道0訪問(wèn)其關(guān)聯(lián)的HBM通道0,以從單個(gè)HBM通道獲得最佳性能。我們使用DDR4通道0獲得DDR4吞吐量數(shù)字。我們觀察到,不同的地址映射策略會(huì)導(dǎo)致性能最高提高一個(gè)數(shù)量級(jí),并且就吞吐量趨勢(shì)而言,HBM的性能特征與DDR4的性能特征不同。

首先,如圖6a,6b,6c,6d所示,使用默認(rèn)地址映射策略,HBM允許使用較大步幅,同時(shí)仍保持高吞吐量。根本原因是,即使由于大的S而沒(méi)有充分利用每個(gè)行緩沖區(qū),存儲(chǔ)組級(jí)并行性也能夠使我們飽和利用內(nèi)存帶寬。 其次,在某些映射策略下,純順序讀取并不總是導(dǎo)致最高吞吐量。圖6b,6c說(shuō)明,當(dāng)S從128增加到2048時(shí),較大的S在策略“ RBC”下可以實(shí)現(xiàn)較高的內(nèi)存吞吐量,因?yàn)檩^大的S允許同時(shí)訪問(wèn)更多激活的存儲(chǔ)組,而較小的S可能導(dǎo)致僅一個(gè)活動(dòng)的儲(chǔ)存組響應(yīng)用戶的存儲(chǔ)請(qǐng)求。 我們得出結(jié)論,在HBM和DDR4下利用儲(chǔ)存組級(jí)并行性來(lái)實(shí)現(xiàn)高內(nèi)存吞吐量至關(guān)重要。

圖7.空間局部性的影響,局部性能緩解大的步幅S的影響

E.內(nèi)存訪問(wèn)局部性的影響

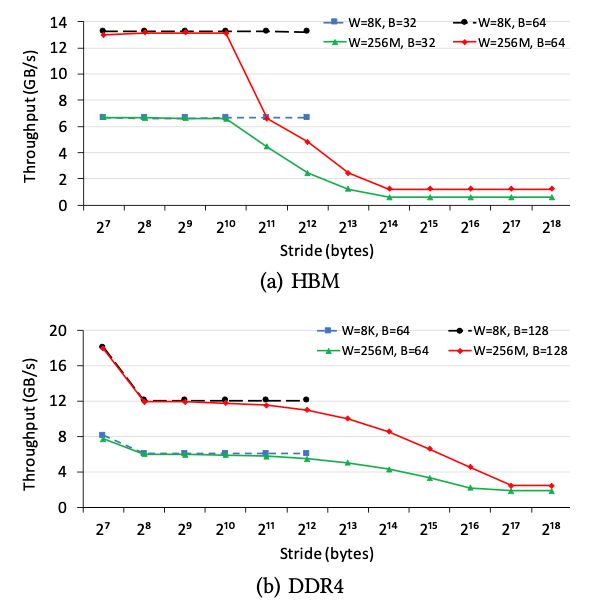

在本小節(jié)中,我們研究了內(nèi)存訪問(wèn)局部性對(duì)內(nèi)存吞吐量的影響。我們更改訪問(wèn)大小B和步幅S,并將工作集大小W設(shè)置為兩個(gè)值:256M和8K。W = 256M的情況是指無(wú)法從任何內(nèi)存訪問(wèn)局部性受益,而W = 8K的情況是指受益的情況。圖7說(shuō)明了HBM和DDR4上不同參數(shù)設(shè)置的吞吐量。我們有兩個(gè)觀察結(jié)果。

首先,內(nèi)存訪問(wèn)局部確實(shí)提高了大的S的情況下的內(nèi)存吞吐量。例如,在HBM上,(B = 32,W = 8K和S = 4K)情況下速度為6.7 GB / s,而(B = 32,W= 256M和S = 4K)僅為2.4 GB / s,這表明內(nèi)存訪問(wèn)位置能夠消除較大步幅S的負(fù)面影響。其次,當(dāng)S較小時(shí),內(nèi)存訪問(wèn)局部性不能增加內(nèi)存吞吐量。相比之下,由于片上緩存的帶寬比片外存儲(chǔ)器要高得多,因此內(nèi)存訪問(wèn)局部性可以顯著提高現(xiàn)代CPU / GPU的總吞吐量[19]。

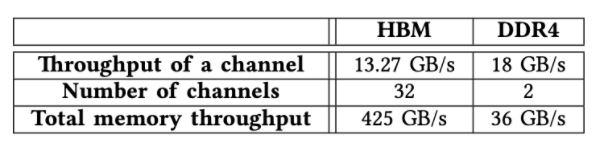

F.總內(nèi)存吞吐量 在本小節(jié)中,我們探討了HBM和DDR4的總可實(shí)現(xiàn)內(nèi)存吞吐量(表V)。當(dāng)我們使用所有32條AXI通道進(jìn)行測(cè)試時(shí),經(jīng)過(guò)測(cè)試的FPGA卡U280上的HBM系統(tǒng)能夠提供高達(dá)425GB / s(13.27 GB / s * 32)的內(nèi)存吞吐量。 當(dāng)我們同時(shí)訪問(wèn)經(jīng)過(guò)測(cè)試的FPGA卡上的兩個(gè)DDR4通道時(shí),內(nèi)存能夠提供高達(dá)36 GB / s(18 GB / s * 2)的內(nèi)存吞吐量。我們觀察到,HBM系統(tǒng)的內(nèi)存吞吐量是DDR4內(nèi)存的10倍,這表明增強(qiáng)了HBM的FPGA使我們能夠加速內(nèi)存密集型應(yīng)用程序,而這通常是在GPU上進(jìn)行加速的。 表格5.HBM和DDR4訪問(wèn)速度對(duì)比,HBM要快一個(gè)數(shù)量級(jí)

在HBM控制器中對(duì)switch進(jìn)行基準(zhǔn)測(cè)試

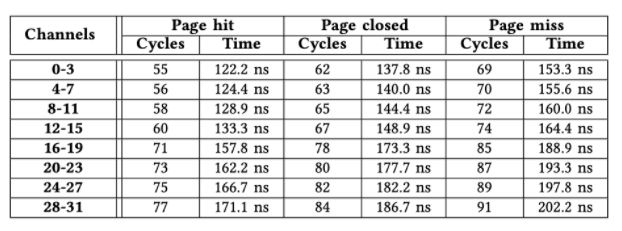

每個(gè)HBM堆棧將內(nèi)存地址空間劃分為16個(gè)獨(dú)立的偽通道,每個(gè)偽通道均與映射到特定地址范圍[41],[44]的AXI端口相關(guān)。因此,需要使用32×32開(kāi)關(guān)來(lái)確保每個(gè)AXI端口都可以訪問(wèn)整個(gè)地址。在HBM存儲(chǔ)器控制器中完全實(shí)現(xiàn)的32×32開(kāi)關(guān)需要大量邏輯資源。因此,該switch僅被部分實(shí)現(xiàn),從而顯著減少了資源消耗,但實(shí)現(xiàn)了特定訪問(wèn)模式的較低性能。我們?cè)诒竟?jié)中的目標(biāo)是揭示switch的性能特征。 A.AXI通道和HBM通道之間的性能 在本小節(jié)中,我們將在時(shí)延和吞吐量方面測(cè)試任何一個(gè)AXI通道和任何HBM通道之間的性能特征。在完全實(shí)現(xiàn)的switch中,從任何AXI通道訪問(wèn)任何HBM通道的性能特征都應(yīng)該大致相同。但是,在當(dāng)前的實(shí)現(xiàn)中,相對(duì)距離可能起著重要的作用。 1)內(nèi)存延遲:由于篇幅所限,我們僅使用所有AXI通道(從0到31)到HBM通道0發(fā)出的內(nèi)存讀取事務(wù)來(lái)演示內(nèi)存訪問(wèn)延遲。對(duì)其他HBM通道的訪問(wèn)具有相似的性能特征。與V-B小節(jié)中的實(shí)驗(yàn)設(shè)置相似,我們還使用引擎模塊來(lái)確定B = 32,W = 0x1000000,N = 2000以及S變化的情況下的準(zhǔn)確等待時(shí)間。表VI說(shuō)明了32個(gè)AXI通道之間的等待時(shí)間差異。我們有兩個(gè)觀察結(jié)果。 首先,延遲差異最多可以達(dá)到22個(gè)周期。例如,對(duì)于頁(yè)面命中事務(wù),來(lái)自AXI通道31的訪問(wèn)需要77個(gè)周期,而來(lái)自AXI通道0的訪問(wèn)僅需要55個(gè)周期。其次,來(lái)自同一微型switch中任何AXI通道的訪問(wèn)等待時(shí)間是相同的,這表明該微型switch已完全實(shí)現(xiàn)。例如,與AXI通道4-7關(guān)聯(lián)的微型switch對(duì)所有通道都顯示相同的內(nèi)存訪問(wèn)延遲。我們得出結(jié)論,AXI通道應(yīng)訪問(wèn)其關(guān)聯(lián)的HBM通道或靠近它的HBM通道,以最大程度地減少延遲。

表格6.從32個(gè)AXI通道訪問(wèn)HBM通道0的延時(shí),距離越遠(yuǎn)延時(shí)越高,可以達(dá)到22個(gè)周期

2)內(nèi)存吞吐量:我們使用引擎模塊來(lái)測(cè)量從任何AXI通道(從0到31)到HBM通道0的內(nèi)存吞吐量,設(shè)置為B =64,W = 0x1000000,N = 200000,并且改變S。圖8說(shuō)明了從每個(gè)小型switch中的AXI通道到HBM通道0的內(nèi)存吞吐量。我們觀察到AXI通道能夠?qū)崿F(xiàn)大致相同的內(nèi)存吞吐量,而不管它們的位置如何。

圖8,從八個(gè)AXI通道到HBM通道1的內(nèi)存吞吐量,其中每個(gè)AXI通道都來(lái)自小switch。每個(gè)AXI通道在訪問(wèn)HBM通道1時(shí)具有大致相同的吞吐量,即使它們的訪問(wèn)延遲可能明顯不同

B.AXI通道之間的干擾

在本小節(jié)中,我們通過(guò)使用不同數(shù)量(例如2、4和6)的AXI通道同時(shí)訪問(wèn)同一HBM通道1,來(lái)檢查AXI通道之間的干擾影響。我們還改變了B的大小。表VII顯示了具有不同的B值和不同的AXI通道的吞吐量。空值表示該AXI通道未參與吞吐量測(cè)試。我們有兩個(gè)觀察結(jié)果。首先,當(dāng)遠(yuǎn)程AXI通道數(shù)量增加時(shí),總吞吐量會(huì)略有下降,這表明交換機(jī)能夠以合理有效的方式為多個(gè)AXI通道提供內(nèi)存事務(wù)。其次,以循環(huán)方式安排微型switch中的兩個(gè)橫向連接和四個(gè)主機(jī)。以AXI通道4、5、8和9同時(shí)訪問(wèn)且B = 32的情況為例,遠(yuǎn)程AXI通道8和9的總吞吐量大致等于AXI通道4或5的總吞吐量。

相關(guān)工作

就我們所知,豎亥是第一個(gè)全面地在FPGA上對(duì)HBM進(jìn)行基準(zhǔn)測(cè)試的平臺(tái)。我們將與豎亥密切相關(guān)的工作進(jìn)行對(duì)比:1)在FPGA上對(duì)傳統(tǒng)存儲(chǔ)器進(jìn)行基準(zhǔn)測(cè)試;2)使用HBM進(jìn)行數(shù)據(jù)處理;3)加速FPGA的應(yīng)用。

表格7.遠(yuǎn)程AXI通道之間的沖突影響。我們使用不同數(shù)量(2、4或6)的遠(yuǎn)程AXI通道來(lái)訪問(wèn)HBM通道1,以測(cè)量吞吐量(GB / s)。當(dāng)遠(yuǎn)程AXI通道的數(shù)量為2時(shí),AXI通道4和5處于活動(dòng)狀態(tài) 。當(dāng)僅使用本地AXI通道1訪問(wèn)HBM通道1時(shí),對(duì)于B = 32,B = 64或B =128的情況,吞吐量為6.67、12.9或13.3 GB / s。空值表示相應(yīng)的AXI通道 不參與特定的基準(zhǔn)測(cè)試。

在FPGA上對(duì)傳統(tǒng)內(nèi)存進(jìn)行基準(zhǔn)測(cè)試。先前的工作[20],[22],[23],[47]試圖通過(guò)使用高級(jí)語(yǔ)言(例如OpenCL)在FPGA上對(duì)傳統(tǒng)存儲(chǔ)器(例如DDR3)進(jìn)行基準(zhǔn)測(cè)試。相反,我們?cè)谧钕冗M(jìn)的FPGA上對(duì)HBM進(jìn)行基準(zhǔn)測(cè)試。

使用HBM/ HMC進(jìn)行數(shù)據(jù)處理。先前的工作[4],[6],[15],[16],[21],[26],[27],[46]使用HBM來(lái)加速其應(yīng)用,例如哈希表深度學(xué)習(xí)和流式傳輸通過(guò)利用Intel KnightsLanding(KNL)的HBM [12]提供的高內(nèi)存帶寬。相比之下,我們?cè)赬ilinx FPGA板上測(cè)試了HBM的性能。 使用FPGA加速應(yīng)用程序。先前的作品[1],[3],[5],[7],[8],[9],[10],[11],[14],[17],[24],[25], [28],[29],[30],[31],[32],[33],[34],[35],[36],[37],[38],[39],[40] ] [45]使用FPGA加速了廣泛的應(yīng)用,例如數(shù)據(jù)庫(kù)和深度學(xué)習(xí)推理。相反,無(wú)論應(yīng)用如何,我們都在最新的FPGA上系統(tǒng)地對(duì)HBM進(jìn)行基準(zhǔn)測(cè)試。

結(jié)論

高帶寬存儲(chǔ)器(HBM)增強(qiáng)了FPGA,以解決IO密集應(yīng)用程序的存儲(chǔ)器帶寬瓶頸。但是,HBM的性能特征仍未在FPGA上進(jìn)行定量和系統(tǒng)的分析。我們通過(guò)在具有兩層HBM2子系統(tǒng)的最新FPGA上對(duì)HBM堆棧進(jìn)行基準(zhǔn)測(cè)試來(lái)揭秘。相應(yīng)的,我們建議使用豎亥來(lái)對(duì)HBM的基本細(xì)節(jié)進(jìn)行測(cè)試。從獲得的基準(zhǔn)測(cè)試數(shù)據(jù)中,我們觀察到:1)HBM提供高達(dá)425 GB / s的內(nèi)存帶寬,大約是最新GPU的內(nèi)存帶寬的一半,2)如何使用HBM對(duì)性能有著顯著影響,這反過(guò)來(lái)證明了揭露HBM特征的重要性。豎亥可以很容易地推廣到其他FPGA板或其他的存儲(chǔ)器模塊。我們將使相關(guān)的基準(zhǔn)測(cè)試代碼開(kāi)源,以便可以探索新的FPGA板并比較各個(gè)板的結(jié)果。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<