幾周前,我們參加了IEDM,臺(tái)積電在會(huì)上展示了有關(guān)其 N3B 和 N3E、3nm 級(jí)工藝節(jié)點(diǎn)的許多細(xì)節(jié)。此外,臺(tái)積電宣布將增加其在亞利桑那州菲尼克斯的資本支出,總計(jì)向 Fab 21 第一階段和第二階段投資 400 億美元。該工廠將分別生產(chǎn) N5 和 N3 系列芯片。

本文章將涵蓋工藝節(jié)點(diǎn)過(guò)渡、臺(tái)積電最先進(jìn)技術(shù)的過(guò)高成本,以及它將如何顯著加速行業(yè)向先進(jìn)封裝和小芯片的轉(zhuǎn)變。此外,我們將詳細(xì)介紹 N5、N4、N3B 和 N3E 的各種間距、特性和 SRAM 單元尺寸。

2018年初,臺(tái)積電宣布投資新晶圓廠。這個(gè)新站點(diǎn)將擁有其最先進(jìn)的技術(shù) N5。隨著蘋(píng)果和華為承諾在 2020 年生產(chǎn) N5 晶圓,這是進(jìn)行大規(guī)模擴(kuò)建的絕佳機(jī)會(huì)。臺(tái)積電表示,他們對(duì) Fab 18 第一至第三階段的投資將超過(guò)新臺(tái)幣 5000 億元,約合 170 億美元。該站點(diǎn)計(jì)劃每月生產(chǎn)超過(guò) 80,000 個(gè)晶圓。在 2020 年第一季度的財(cái)報(bào)電話會(huì)議上,臺(tái)積電確認(rèn) N5 正在大批量生產(chǎn),可能處于第一階段。

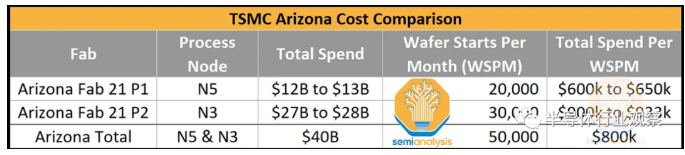

盡管臺(tái)南科學(xué)園區(qū)的 Fab 18 仍將是 N5 生產(chǎn)的主要地點(diǎn),但臺(tái)積電還宣布將其業(yè)務(wù)擴(kuò)展到美國(guó)亞利桑那州鳳凰城。2018年年中,臺(tái)積電宣布該廠總投資120億美元,月產(chǎn)2萬(wàn)片晶圓。這座工廠建成后,將成為臺(tái)積電在臺(tái)灣以外制造的最先進(jìn)的技術(shù)節(jié)點(diǎn)。到 2022 年,臺(tái)積電的 N5 產(chǎn)能將遠(yuǎn)超每月 12 萬(wàn)片晶圓,這僅占臺(tái)積電 N5 產(chǎn)能的 15% 左右。

乍一看,臺(tái)灣臺(tái)南 N5 的第 1 至 3 期設(shè)施規(guī)模擴(kuò)大了 4 倍,但成本僅高出 40%,這證明了在沒(méi)有大量補(bǔ)貼的情況下在美國(guó)建造晶圓廠在經(jīng)濟(jì)上沒(méi)有意義的論點(diǎn). 實(shí)際上,這些數(shù)字沒(méi)有可比性。臺(tái)積電為美國(guó)晶圓廠提供的數(shù)字包括 2021 年至 2029 年的所有總支出。這遠(yuǎn)遠(yuǎn)超過(guò)了最初的資本支出成本。臺(tái)積電給臺(tái)灣晶圓廠的數(shù)字只是最初的擴(kuò)建,沒(méi)有其他成本。

應(yīng)該注意的是,在初始擴(kuò)建期間,晶圓廠總成本的約 80% 來(lái)自設(shè)備。此外,超過(guò) 60% 的運(yùn)營(yíng)成本來(lái)自材料、化學(xué)品、工具維護(hù)和能源投入。無(wú)論晶圓廠位于何處,這些成本大多相同(能源確實(shí)不同)。

臺(tái)積電 3nm 晶圓廠成本

位于臺(tái)南科學(xué)園區(qū)的 Fab 18 也是生產(chǎn) N3 系列節(jié)點(diǎn)的主要地點(diǎn)。第 4 至第 6 期專(zhuān)供3nm家族使用。位于新竹科學(xué)園區(qū)的 Fab 12 第 8 期和第 9 期也將生產(chǎn)該節(jié)點(diǎn)。近日,臺(tái)積電又宣布投資Fab 21 Phase 2。?這擴(kuò)大了其在亞利桑那州的現(xiàn)有工廠,以生產(chǎn) N3 晶圓。亞利桑那州的新計(jì)劃將使臺(tái)積電的總支出增加到 400 億美元,并將產(chǎn)能增加到每月 50,000 片晶圓。其中 20,000 個(gè)仍將是 N5,30,000 個(gè)將是 N3。完成后,N3 產(chǎn)能將占臺(tái)積電全球 N3 產(chǎn)能的 25%。

這將是臺(tái)積電首次分享同一地點(diǎn)不同代工廠之間的完整成本比較。由于成本超支的傳言,臺(tái)積電的 N5 晶圓廠成本可能已從最初的120億美元增加到130億美元。最有可能的是,這些成本處于該范圍的中間。

每個(gè)晶圓開(kāi)始的每月總支出從 38% 增加到 55%。這與我們聽(tīng)到的 N3 定價(jià)比 N5 高出約 40% 的其他謠言非常吻合。與DigiTimes 的謠言相反,晶圓價(jià)格不是 20,000 美元。

N3 的故事很復(fù)雜。最初,考慮到不溫不火的性能、功率和密度改進(jìn),N3 的良率和價(jià)格都具有挑戰(zhàn)性,超出了大多數(shù)客戶愿意支付的價(jià)格。它有大約 25 個(gè) EUV 層,幾乎是 N5 的兩倍。N3 出現(xiàn)了許多問(wèn)題,最終導(dǎo)致臺(tái)積電錯(cuò)過(guò)了典型的 2 年主要工藝節(jié)點(diǎn)發(fā)布周期。對(duì)公眾來(lái)說(shuō)最值得注意的變化是,隨著摩爾定律的放緩,蘋(píng)果公司被迫徹底改變其產(chǎn)品的芯片計(jì)劃。

除了將 N3 從 2022 款 iPhone 推出到 2023 款 Pro iPhone 之外,許多其他客戶也放棄了他們最初的 N3 計(jì)劃。關(guān)于 Zen 5、英特爾 GPU 和一些 Broadcom 定制 ASIC 存在許多謠言。據(jù)傳,這些公司選擇堅(jiān)持使用 N5 級(jí)工藝節(jié)點(diǎn)或轉(zhuǎn)向?qū)捤傻?N3E 工藝。最初的 N3 被大多數(shù)人稱(chēng)為 N3B,但 N3E 與 N5 類(lèi)工藝節(jié)點(diǎn)共享相同的 SRAM 位單元大小,并減少了 EUV 曝光的次數(shù)。

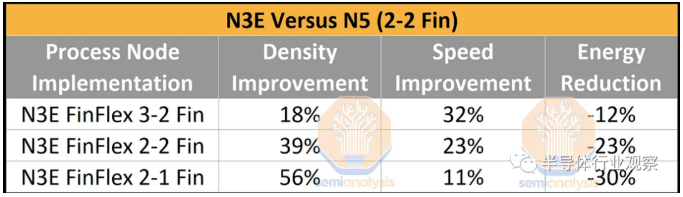

密度的提高充其量只是略高于晶圓成本的增加。通過(guò) FinFlex 2-1 實(shí)施,密度提高了 56%,成本增加了 40%。這導(dǎo)致每個(gè)晶體管的成本降低了 11%,這是 50 多年來(lái)主要工藝技術(shù)的最弱擴(kuò)展。

其他實(shí)現(xiàn)要么在每個(gè)晶體管的成本上持平,要么甚至為負(fù),但每個(gè)晶體管的速度都有更大的改進(jìn)。請(qǐng)注意,上述一代又一代的改進(jìn)是使用 Arm Cortex A72 測(cè)量的。密度改進(jìn)將根據(jù)正在實(shí)施的 IP 而有所不同。

大多數(shù)芯片設(shè)計(jì)不會(huì)實(shí)現(xiàn) 56% 的密度提升,而是低得多,約為 30%。這意味著每個(gè)晶體管的成本增加,但公司正在調(diào)整設(shè)計(jì)以確保不會(huì)發(fā)生這種情況。這將在工藝技術(shù)部分進(jìn)行解釋。

3nm 實(shí)施成本

當(dāng)采用最先進(jìn)的工藝技術(shù)實(shí)現(xiàn)芯片的成本變得更高時(shí),轉(zhuǎn)向 3nm 或留在 N5 系列的決定變得更加棘手。

我們?cè)谏厦嬖敿?xì)解釋了這個(gè)問(wèn)題,但在最新的工藝技術(shù)中實(shí)施產(chǎn)品的固定成本變得如此之大,以至于對(duì)公司來(lái)說(shuō)意味著巨大的風(fēng)險(xiǎn)。延遲變得越來(lái)越棘手,重新設(shè)計(jì)的成本越來(lái)越高,最糟糕的是,實(shí)現(xiàn)每晶體管成本改進(jìn)所需的體積越來(lái)越大。

出于這個(gè)原因,許多公司將在未來(lái)很長(zhǎng)一段時(shí)間內(nèi)堅(jiān)持使用 N5 級(jí)工藝節(jié)點(diǎn)。許多其他公司只會(huì)將計(jì)算小芯片轉(zhuǎn)移到 N3 類(lèi),同時(shí)保留所有其他 IP,例如 SRAM 和模擬的舊工藝技術(shù)。臺(tái)積電 N3 將導(dǎo)致小芯片和先進(jìn)封裝的爆炸式增長(zhǎng)。

在我們進(jìn)入 N3 工藝細(xì)節(jié)之前,我們想詳細(xì)介紹一下 N5 系列,因?yàn)樗鎸?shí)地證明了 TSMC 的驚人之處。迭代的不是一個(gè)制程節(jié)點(diǎn),而是最適合每種不同類(lèi)型客戶需求的許多并發(fā)風(fēng)格和修改。

5nm工藝族技術(shù)詳解

臺(tái)積電 N5 系列的一部分包括:N5、N5P、N5A、N4、N4P 和 N4X。除了那些已宣布的變體之外,我們預(yù)計(jì)臺(tái)積電將在未來(lái)幾年內(nèi)發(fā)布 RF 優(yōu)化和泄漏優(yōu)化版本。通過(guò)所有這些變體,臺(tái)積電希望延長(zhǎng)工藝技術(shù)的壽命,并將更多客戶推向 N4 節(jié)點(diǎn),部分原因是它們的生產(chǎn)成本較低,客戶的固定成本也較低。N4 是量產(chǎn)的最新節(jié)點(diǎn),已在聯(lián)發(fā)科天璣 9200、高通驍龍 8 Gen 2 和 Apple A16 中實(shí)現(xiàn)。

N5 是一個(gè)工程奇跡,在其發(fā)布時(shí)無(wú)疑是最先進(jìn)的節(jié)點(diǎn)。臺(tái)積電宣布其邏輯密度將提高 1.84 倍,在相同功耗下性能提升 15%,在相同性能下功耗降低 30%。雖然無(wú)數(shù)芯片在性能和功率方面確實(shí)得到了改進(jìn),但似乎從未實(shí)現(xiàn)過(guò)規(guī)定的密度增益。

正如 Angstronomics 最近報(bào)道的那樣,這是因?yàn)榕_(tái)積電撒謊了。邏輯密度的增益接近 52%。雖然臺(tái)積電可能在密度上撒了謊,但臺(tái)積電N5仍然是量產(chǎn)中最好的節(jié)點(diǎn)。

N5 的鰭間距為 28nm,僅略低于三星 5LPE,接觸柵極間距為 51nm,僅略低于 Intel 4。通過(guò)連續(xù)擴(kuò)散的新方法,他們?cè)O(shè)法減小了單元寬度。

N5 在 M0 上的最小金屬間距為 28nm,比 N7 減少了 30%。這將有助于減少可能由信號(hào)和電源路由引起的瓶頸。臺(tái)積電的 M2 金屬間距為 35 納米,擁有一個(gè) 6 軌標(biāo)準(zhǔn)單元,盡可能密集,使用帶有 2 個(gè) PMOS 鰭片和 2 個(gè) NMOS 鰭片的 FinFET。N5 還擁有最小的 6T 高密度 SRAM 位單元,尺寸為 0.021 μm2,低于 Intel 4 的 0.0240 μm2 和三星 4LPE 的 0.0262 μm2 位單元。TSMC 的 6T 高電流 SRAM 位單元也非常小,只有 0.025 μm2,是迄今為止密度第三高的。

N5P是N5的流程優(yōu)化。通過(guò)增強(qiáng)工藝的 FEOL 和 MOL,臺(tái)積電的性能提高了 7%,功耗降低了 15%。雖然這看起來(lái)可能不多,但好處是這種流程優(yōu)化與 N5 是 IP 兼容的。任何 N5 設(shè)計(jì)都可以輕松移植到 N5P 并看到這些收益。隨著半導(dǎo)體設(shè)計(jì)固定成本的飆升,其影響不可低估。

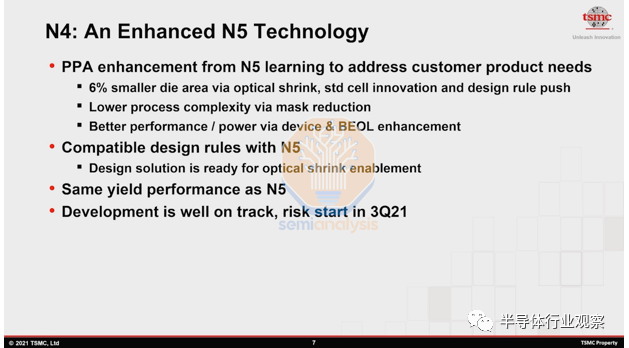

N4是N5的另一項(xiàng)工藝優(yōu)化,但它有一個(gè)小的設(shè)計(jì)收縮。這也稱(chēng)為“nodelet”。通過(guò)標(biāo)準(zhǔn)單元庫(kù)的優(yōu)化、較小的光學(xué)收縮和設(shè)計(jì)規(guī)則的改變,N4 實(shí)現(xiàn)了更好的面積效率。N4 還減少了掩模數(shù)量和工藝復(fù)雜性。這使得臺(tái)積電能夠以低于每片晶圓 N5 的成本生產(chǎn) N4。

Nikkei Asia曾有傳言稱(chēng) Apple A16 的制造成本是其制造商的 2 倍,但這完全是錯(cuò)誤的。與 N5P 非常相似,通過(guò)改進(jìn) FEOL 和 MOL 改進(jìn)了功率和性能特征。

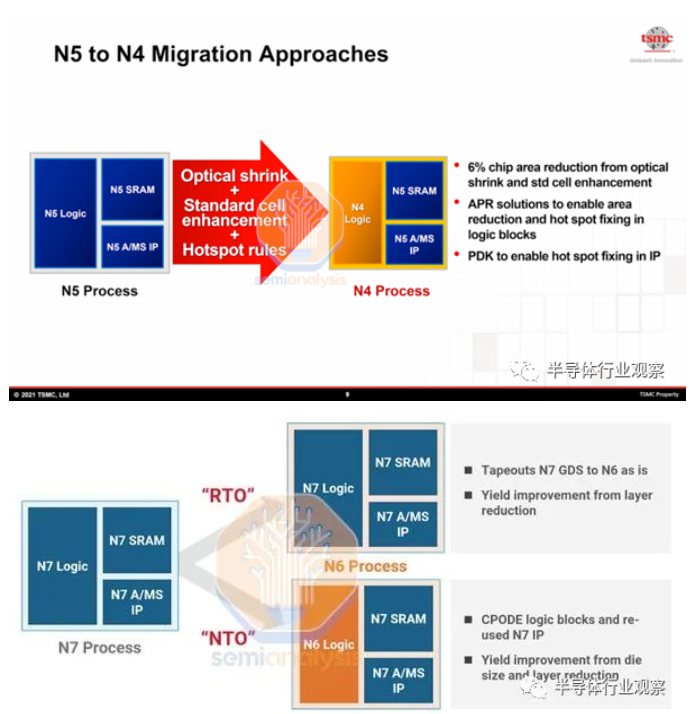

與 TSMC 的其他 nodelet N6 一樣,N4 提供了兩種從現(xiàn)有 N5 設(shè)計(jì)遷移的方法。兩者都有其權(quán)衡取舍。

首先是 RTO 或重新流片,涉及使用與 N5 相同的設(shè)計(jì)規(guī)則。這更便宜,需要更少的工程,并且提供更少的 N4 的好處。這就是聯(lián)發(fā)科能夠在風(fēng)險(xiǎn)生產(chǎn)后這么快就在“N4”上發(fā)布天璣 9000 的原因。

接下來(lái)是 NTO 或新流片,這需要使用 N4 提供的最新庫(kù)和更多優(yōu)化來(lái)重新實(shí)現(xiàn)邏輯塊。這需要更多的工程,但提供了更多的好處,包括較小的面積縮小。

2021 年底,臺(tái)積電宣布 N4P?,這是 N4 的工藝優(yōu)化。通過(guò)進(jìn)一步改進(jìn) FEOL 和 MOL,TSMC 的性能比 N4 又提高了 6%,功耗比 N5 降低了 22%。

現(xiàn)在進(jìn)入專(zhuān)業(yè)技術(shù);N5A基于臺(tái)積電的N5工藝。這個(gè)節(jié)點(diǎn)在技術(shù)上并不是特別獨(dú)特。但是,它已通過(guò)汽車(chē)公司在使用工藝節(jié)點(diǎn)時(shí)尋求的所有標(biāo)準(zhǔn)的認(rèn)證。它經(jīng)過(guò)優(yōu)化,可以在車(chē)輛中長(zhǎng)時(shí)間(10 年或 20 年)存活而不會(huì)降解。

N4X 是臺(tái)積電首款 HPC 優(yōu)化制程技術(shù)。N4X 針對(duì)超過(guò) 1.2V 的高壓設(shè)備進(jìn)行了優(yōu)化,性能比 N4P 提高了 4%。FEOL 對(duì)鰭片進(jìn)行了改進(jìn),以允許更高的電流、電壓和更高的頻率。金屬堆棧經(jīng)過(guò)精心設(shè)計(jì),可通過(guò)降低電阻和寄生電容來(lái)改善這些高性能設(shè)備的功率傳輸和信號(hào)完整性。金屬堆棧還具有改進(jìn)的金屬金屬電容器,可通過(guò)減少電壓降并將性能進(jìn)一步提高 2-3% 來(lái)提供更強(qiáng)大的電力傳輸。

為了達(dá)到如此高的頻率,可能放寬了一些設(shè)計(jì)規(guī)則,但這可能不是問(wèn)題,因?yàn)楦咝阅茉O(shè)備更受金屬堆疊的限制,無(wú)論如何都無(wú)法利用密度。在泄漏方面也有一些讓步,必須做出這些讓步才能實(shí)現(xiàn)更高的性能。大多數(shù)半導(dǎo)體公司不會(huì)使用此節(jié)點(diǎn),因?yàn)樗麄兏矚g較低的功耗/泄漏,但 N4X 是一些最高性能應(yīng)用的有力競(jìng)爭(zhēng)者。

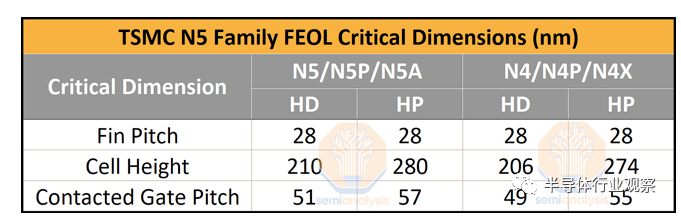

現(xiàn)在,我們將討論 N5 系列節(jié)點(diǎn)的關(guān)鍵間距,并專(zhuān)門(mén)詳細(xì)介紹 TSMC 的 N4 節(jié)點(diǎn)的間距。N5 的高密度 (HD) 庫(kù)的鰭間距為 28nm,具有 8 條擴(kuò)散線,單元高度為 210nm。接觸柵極間距 (CGP) 為 51nm。N5 的高性能 (HP) 庫(kù)具有相同的間距,但為 280nm 的單元高度添加了 2 條擴(kuò)散線。高性能庫(kù)還將 CGP 略微放寬至 57nm,從而實(shí)現(xiàn)更高的性能。正如臺(tái)積電所說(shuō),N4 通過(guò)光學(xué)縮小提供了 6% 的面積減少。為實(shí)現(xiàn)這一目標(biāo),HD 和 HP 庫(kù)的單元高度分別縮小到 206 納米和 274 納米。此外,CGP已經(jīng)縮小到49nm和55nm。

N5 為其最低金屬層提供 28nm 的間距,這是生產(chǎn)中最小的。這也是節(jié)點(diǎn)的最小金屬間距。它還提供 35nm 的金屬 2 間距,這是生產(chǎn)中最小的間距。

正如我們所提到的,N5 在每個(gè) 6T HD 和 HP 位單元類(lèi)別中都具有生產(chǎn)中最密集的位單元。借助 30% 的輔助電路開(kāi)銷(xiāo),HD SRAM 密度達(dá)到 31.8 Mib/mm2,HP SRAM 密度達(dá)到 26.7 Mib/mm2。盡管 N4 并未帶來(lái) SRAM 位單元尺寸的進(jìn)一步縮小,但臺(tái)積電仍處于領(lǐng)先地位。

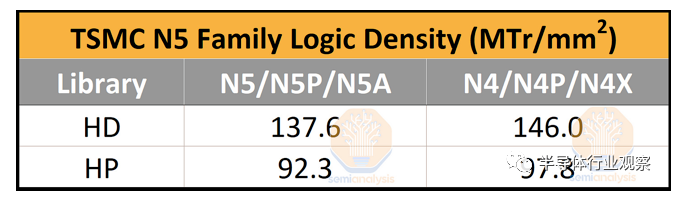

現(xiàn)在,進(jìn)入主要吸引力,邏輯密度。雖然這可能是最引人注目的數(shù)字,但它并不能單獨(dú)描述一個(gè)節(jié)點(diǎn)。必須考慮所有其他特性,從其 SRAM 位單元到功率和性能。這些指標(biāo)是使用 Bohr 公式計(jì)算的,該公式將 60% 的權(quán)重分配給小而稀疏的 NAND2 單元,將 40% 的權(quán)重分配給大但密集的 Scan Flip-Flop 單元。臺(tái)積電在這一指標(biāo)上處于領(lǐng)先地位,但在其他因素上略遜一籌。

雖然其HD庫(kù)的密度是生產(chǎn)中最高的,但其HP庫(kù)的密度落后于Intel 4的HP。需要明確的是,根據(jù)英特爾的說(shuō)法,Intel 4 已經(jīng)“準(zhǔn)備好制造”,但真正的大批量生產(chǎn)還需要幾個(gè)季度。然而,密度是使用 TSMC 的 N5 系列節(jié)點(diǎn)的最誘人的原因之一。

臺(tái)積電的 N5 系列是一組出色的節(jié)點(diǎn),單靠這些指標(biāo)并不能說(shuō)明問(wèn)題。它在功率、性能、面積、易用性、IP 生態(tài)系統(tǒng)和成本方面的組合是無(wú)與倫比的。

N3技術(shù)節(jié)點(diǎn)

N3 系列節(jié)點(diǎn)包括 N3B、N3E、N3P、N3X 和 N3S。其中許多是針對(duì)特定目的優(yōu)化的小節(jié)點(diǎn),但有所不同。N3B,即初代的 N3,與 N3E 無(wú)關(guān)。與其將其視為 nodelet,不如將其視為一個(gè)完全不同的節(jié)點(diǎn)。

在 IEDM 2022 上,臺(tái)積電透露了 N3B 的一些方面。N3B 具有 45nm 的 CGP,與 N5 相比縮小了 0.88 倍。臺(tái)積電還實(shí)施了自對(duì)準(zhǔn)接觸,從而可以更大程度地?cái)U(kuò)展 CGP。臺(tái)積電還展示了 0.0199 μm2 的 6 晶體管高密度 SRAM 位單元。這僅縮小了 5%,這對(duì)于 SRAM 未來(lái)的擴(kuò)展來(lái)說(shuō)是個(gè)壞兆頭。

近年來(lái),芯片設(shè)計(jì)人員嚴(yán)重依賴(lài) SRAM 來(lái)提高性能。SRAM 縮放的消亡帶走了提高性能的一個(gè)重要杠桿,并將增加架構(gòu)在提高功率和性能特征方面的重要性。

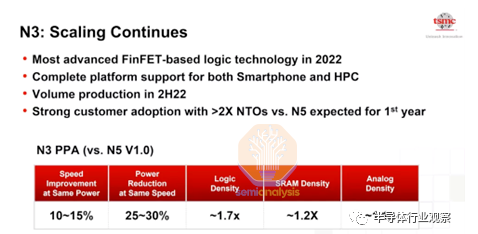

與N5相比,臺(tái)積電最初表示,N3在同等功率下性能提升約12%,同等性能下功耗降低27%。這將具有 1.2× SRAM 密度和 1.1× 模擬密度。

IEDM 上公開(kāi)的高密度位單元僅將 SRAM 密度提高了約 5%,與最初聲稱(chēng)的 20% 相去甚遠(yuǎn)。

誰(shuí)能解釋一下為什么臺(tái)積電又不誠(chéng)實(shí)了…………

在 IEDM 期間,臺(tái)積電透露 N3B 的 CGP 為 45nm,是迄今為止透露的最密集的。這領(lǐng)先于Intel 4的50nm CGP、三星4LPP的54nm CGP和TSMC N5的51nm CGP。

雖然邏輯密度的增加無(wú)疑是有希望的,但低 SRAM 密度增益意味著 SRAM-heavy 設(shè)計(jì)可能會(huì)經(jīng)歷顯著的成本增加。N3B 的良率和金屬堆疊性能也很差。基于這些原因,N3B 不會(huì)成為臺(tái)積電的主要節(jié)點(diǎn)。

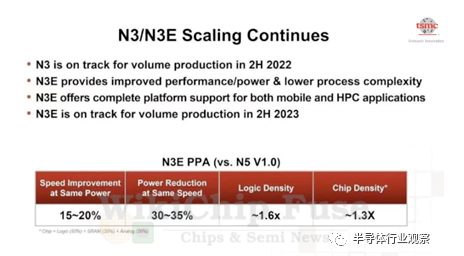

由于 N3B 未能達(dá)到 TSMC 的性能、功率和產(chǎn)量目標(biāo),因此開(kāi)發(fā)了 N3E。其目的是修復(fù)N3B的缺點(diǎn)。第一個(gè)重大變化是金屬間距略有放松。臺(tái)積電沒(méi)有在 M0、M1 和 M2 金屬層上使用多重圖案化 EUV,而是退縮并切換到單一圖案化。

此外,上一代需要 EUV 雙圖案化的三個(gè)關(guān)鍵層被單 EUV 圖案化所取代,這降低了工藝復(fù)雜性、固有成本和周期時(shí)間。

這是在保持功率和性能數(shù)據(jù)相似的同時(shí)實(shí)現(xiàn)的。邏輯密度也略有下降。此外,使用標(biāo)準(zhǔn)單片芯片(50% 邏輯 + 30% SRAM + 20% 模擬),密度僅增加 1.3 倍。

在 IEDM 期間,臺(tái)積電透露 N3E 的位單元尺寸為 0.021 μm2,與 N5 完全相同。這對(duì)SRAM來(lái)說(shuō)是毀滅性的打擊。由于良率,臺(tái)積電放棄了 SRAM 單元尺寸而不是 N3B。

臺(tái)積電表示,256Mb HC/HD SRAM 宏和類(lèi)似產(chǎn)品的邏輯測(cè)試芯片始終表現(xiàn)出比我們上一代更健康的缺陷密度。

N3E 比 N3B 做得好得多,明年年中將量產(chǎn)。對(duì)于那些保持跟蹤的人來(lái)說(shuō),N5 推出已經(jīng) 3 年多了。這是 AMD、Nvidia、Broadcom、Qualcomm、MediaTek、Marvell和許多其他公司最終將使用 N3E 作為其領(lǐng)先優(yōu)勢(shì)的節(jié)點(diǎn)。

與臺(tái)積電為其 N7 和 N5 系列節(jié)點(diǎn)推出的先前 nodelet 不同,N3E 與 N3B IP 不兼容。這意味著必須重新實(shí)現(xiàn) IP 塊。因此,許多公司,例如 GUC,選擇只在更持久的 N3E 節(jié)點(diǎn)上實(shí)現(xiàn)他們的 IP。

N3P 將是 N3E 的后續(xù)節(jié)點(diǎn)。它與 N5P 非常相似,通過(guò)優(yōu)化提供較小的性能和功率增益,同時(shí)保持 IP 兼容性。N3X 與 N4X 類(lèi)似,并針對(duì)非常高的性能進(jìn)行了優(yōu)化。到目前為止,功率、性能目標(biāo)和時(shí)間表尚未公布。

N3S 是最終公開(kāi)的變體,據(jù)說(shuō)是密度優(yōu)化的節(jié)點(diǎn)。目前知道的不多,但有一些謠言。Angstronomics 認(rèn)為這可能是一個(gè)單鰭庫(kù),可以讓臺(tái)積電進(jìn)一步縮小單元高度。由于金屬堆疊的限制因素,這可能會(huì)受到限制,但設(shè)計(jì)會(huì)盡可能使用它。N3S 甚至可能實(shí)施背面供電網(wǎng)絡(luò)來(lái)緩解許多金屬堆疊問(wèn)題,盡管這尚未得到證實(shí)。

作為臺(tái)積電的最后一個(gè) FinFET 節(jié)點(diǎn),N3E 及其后續(xù)節(jié)點(diǎn)有機(jī)會(huì)獲得與臺(tái)積電最成功的節(jié)點(diǎn)之一 N28 類(lèi)似的地位。鑒于其動(dòng)蕩的歷史,這將是一項(xiàng)艱巨的任務(wù),但臺(tái)積電已經(jīng)多次證明了自己的能力,尤其是在其生態(tài)系統(tǒng)方面。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<