過去3年來,,盡管客戶十分認(rèn)可萊迪思 (Lattice) Nexus FPGA平臺在低功耗領(lǐng)域做出的種種創(chuàng)新,,但在與他們的交流過程中,我們發(fā)現(xiàn)除功耗外,,性能和尺寸也日益成為客戶關(guān)注的關(guān)鍵要素,。幸運的是,這些與萊迪思最擅長的領(lǐng)域完全吻合,。于是,,基于Nexus平臺取得的一系列創(chuàng)新成果,萊迪思推出了全新低功耗中端Avant FPGA平臺,。

Avant產(chǎn)品主要面向通信,、計算、工業(yè)和汽車等領(lǐng)域,。與此前的產(chǎn)品相比,,Avant平臺在性能和硬件資源方面得到了進(jìn)一步的強化,例如邏輯單元容量達(dá)到了500K,,相比以往100K-150K的配置,,提升了5倍;帶寬提升了10倍,,計算性能提升30倍,。它的面世不但意味著萊迪思邁入了中端FPGA供應(yīng)商的行列,還打開了一扇通往30億美元增量市場的新大門。

打造史上最強產(chǎn)品組合

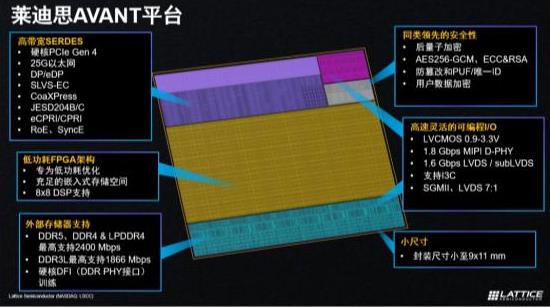

“低功耗”,、“先進(jìn)的互聯(lián)”和“優(yōu)化的計算”是Avant平臺的三大核心特點,,其關(guān)鍵的架構(gòu)亮點包括25G SERDES和并行I/O標(biāo)準(zhǔn),可滿足各種接口的需求,,支持各類外部存儲器接口,,包括DDR4、DDR5和LPDDR4以及傳統(tǒng)標(biāo)準(zhǔn),。同時,,與同類競品器件相比,封裝尺寸減小多達(dá)6倍,,可實現(xiàn)高效的小尺寸系統(tǒng)設(shè)計,。

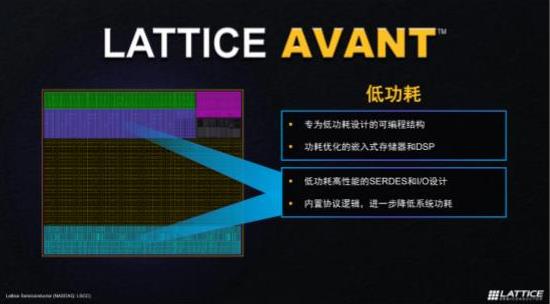

與現(xiàn)有的中端FPGA相比,得益于專為低功耗設(shè)計的可編程結(jié)構(gòu),、功耗優(yōu)化的嵌入式存儲器和DSP、低功耗高性能SERDES與I/O設(shè)計,、內(nèi)置協(xié)議邏輯等全方位優(yōu)化措施,,Avant系列產(chǎn)品的功耗比同類競品器件低2.5倍,可幫助系統(tǒng)和應(yīng)用工程師大幅提高功耗和散熱設(shè)計的效率,、降低運營成本,、增強可靠性。

與Nexus FPGA平臺選用FD-SOI制造工藝不同的是,,此番Avant選擇了臺積電16nm FinFET工藝,。主要基于以下兩方面的考量:一是盡管28nm FD-SOI工藝在功耗方面的確有優(yōu)勢,但FinFET的IP更豐富,,更容易提升產(chǎn)量,。從實際效果來看,16nm FinFET在低功耗上的表現(xiàn)也相當(dāng)不錯,;二是Avant還需要考慮計算能力,,經(jīng)過慎重選擇,16nm FinFET工藝對于Avant而言是非常好的選擇,。

SERDES互聯(lián)方面,,與同類競品器件相比,性能最高提升2倍,,可提供更高的帶寬并減少SERDES鏈路,,降低系統(tǒng)成本及尺寸。目前,,Avant最大能夠支持25G SERDES,,而以往萊迪思產(chǎn)品所能達(dá)到的SERDES最高速率是16G,此外,PCIe接口支持也升級到了Gen 4 x8,,內(nèi)存支持則從LPDDR4擴展到DDR5,。

“優(yōu)化的計算”包含兩個部分:一是瞄準(zhǔn)AI推理應(yīng)用,對片上計算單元中的DSP和嵌入式存儲分布分別進(jìn)行了強化和優(yōu)化,,更有利于邊緣計算,;二是增加了安全引擎,并優(yōu)化,、加強了加密算法,。

上市時間始終是客戶最為關(guān)注的一個問題。為了便于客戶更快地把Avant應(yīng)用到實際產(chǎn)品中去,,Avant可以利用萊迪思現(xiàn)有的所有軟件解決方案,,包括sensAI、mVision,、Automate,、ORAN解決方案集合;PROPEL,、RANDIANT設(shè)計工具,;各類IP、SDK套件和參考設(shè)計,,用以縮短設(shè)計周期,,加速開發(fā)。

與任何新的嵌入式設(shè)計一樣,,安全性必須放在首位,。為此,萊迪思的工程師們在Avant平臺中采用了廣泛的安全功能,,如AES256-GCM,、ECC、RSA,、防篡改和物理不可檢測功能(PUF),。這些功能使配置和用戶數(shù)據(jù)都要加密和驗證,為確保FPGA免受惡意攻擊提供高級別的防護(hù),。此外,,軟錯誤檢測和糾正確保能夠快速檢測到導(dǎo)致軟錯誤的環(huán)境影響,以便采取適當(dāng)?shù)男袆訂印?/p>

作為新的產(chǎn)品系列,,Avant今后也會和Nexus平臺一樣針對不同應(yīng)用場景和需求,,陸續(xù)推出容量、接口,、控制,、視頻規(guī)格不同的產(chǎn)品,,與Nexus FPGA平臺一起組成萊迪思“史上最強產(chǎn)品組合”。

Avant-E,,專為網(wǎng)絡(luò)邊緣處理而生

萊迪思Avant-E FPGA是首款基于這一新平臺的器件,,擁有嵌入式存儲器和18 x 18位DSP引擎,每個可配置為4個8 x 8位DSP,,用以提高整體處理速度,。架構(gòu)中的分布式資源與AI ASIC芯片的架構(gòu)類似,能夠以較低的工作頻率并行處理數(shù)據(jù),。與同類競品器件相比,,Avant-E FPGA的功耗降低了2.5倍之多。因此,,可用作網(wǎng)絡(luò)邊緣設(shè)備的AI引擎,,可以在現(xiàn)場重新編程,幫助系統(tǒng)架構(gòu)師更好地跟上AI創(chuàng)新的步伐,,這些優(yōu)勢是其他處理方案(如ASIC)難以實現(xiàn)的,。

有著明確時序要求的應(yīng)用,包括工業(yè)環(huán)境中的機器視覺,、機器人,、機器人導(dǎo)航和安全攝像頭是最能夠發(fā)揮Avant-E FPGA優(yōu)勢的代表性場景。例如,,自動化工廠的傳送帶高速移動,機器視覺攝像頭在監(jiān)控傳送帶上的產(chǎn)品時必須能夠快速感知,、思考并處理它接收的數(shù)據(jù),,在發(fā)現(xiàn)有瑕疵的產(chǎn)品時,快速將其挑出,,進(jìn)行人工檢查,。

在這一過程中,需要經(jīng)過感知,、思考和行動三個階段,,Avant-E FPGA則可以支持這三個關(guān)鍵功能硬件優(yōu)化的端到端實現(xiàn)。

在“感知”層的預(yù)處理模塊中,,Avant-E FPGA擁有靈活的接口,,可輕松集成不同類型的傳感器,從而允許更多數(shù)據(jù)更快地進(jìn)入流水線,。數(shù)據(jù)或圖像可以根據(jù)需要在接口中進(jìn)行調(diào)整和改進(jìn),,然后進(jìn)入到流水線的后續(xù)操作。

進(jìn)入使用AI從數(shù)據(jù)中獲取智能的“思考”階段,,Avant-E中的硬件可編程性和超低功耗能夠最小化密集計算的功耗,。之后,憑借硬件加速后處理能力,Avant-E FPGA可以有效減少整個流水線的延遲,,當(dāng)需要在特定時間范圍內(nèi)執(zhí)行操作時,,這一特性非常有利于實現(xiàn)任務(wù)關(guān)鍵型應(yīng)用。

結(jié)語

隨著行業(yè)市場的要求越來越高,、越來越細(xì)致化,,這就要求FPGA能夠根據(jù)客戶需求做定制,或是提供更好的解決行業(yè)痛點的方案,。因此,,如何走出傳統(tǒng)通用型應(yīng)用市場,針對行業(yè)差異性,、區(qū)分度,,提供更適合每個行業(yè)的應(yīng)用,這是FPGA新的發(fā)展機會,,也是新的挑戰(zhàn),。