眾所周知,隨著企業(yè)轉(zhuǎn)向比集中式云數(shù)據(jù)中心更低的延遲、更安全和私密的處理,網(wǎng)絡(luò)邊緣計(jì)算持續(xù)快速增長(zhǎng)。市場(chǎng)上正部署數(shù)十億的網(wǎng)絡(luò)邊緣計(jì)算設(shè)備,而且隨著時(shí)間的推移,它們會(huì)變得越來(lái)越先進(jìn)。機(jī)器學(xué)習(xí)和深度神經(jīng)網(wǎng)絡(luò)的發(fā)展為這一趨勢(shì)鋪平了道路,使其能夠以比以往更快的速度處理更多的數(shù)據(jù)。然而,網(wǎng)絡(luò)邊緣處理要求能夠持續(xù)運(yùn)行密集的硬件計(jì)算任務(wù),因此系統(tǒng)處理器的性能需要維持在較高水平,保持?jǐn)?shù)據(jù)流平穩(wěn)運(yùn)行。

雖然SoC可以連續(xù)處理任務(wù),但它的代價(jià)是高功耗以及操作系統(tǒng)和其他軟件層高昂的運(yùn)營(yíng)成本。為了滿足硬件密集型任務(wù)的需求,系統(tǒng)架構(gòu)正向異構(gòu)計(jì)算轉(zhuǎn)變,即讓系統(tǒng)中緊鄰傳感器的器件分擔(dān)主處理器的負(fù)載。除了物聯(lián)網(wǎng)和PC之外,這種類型的架構(gòu)在汽車、機(jī)器人和工業(yè)系統(tǒng)中已經(jīng)十分常見。FPGA充當(dāng)并行計(jì)算引擎,能夠優(yōu)化硬件模塊以加速任務(wù)處理。

隨著Avant平臺(tái)的推出,萊迪思為市場(chǎng)注入了新的可能性。萊迪思Avant旨在將行業(yè)領(lǐng)先的低功耗、小尺寸和高性能優(yōu)勢(shì)引入中端FPGA。Avant提供同類產(chǎn)品中領(lǐng)先的低功耗、先進(jìn)的互連和優(yōu)化的計(jì)算能力,滿足通信、計(jì)算、工業(yè)和汽車市場(chǎng)更廣泛的客戶應(yīng)用需求。

2022年12月5日,萊迪思推出了首款基于這一新平臺(tái)的萊迪思Avant-E FPGA器件,旨在解決客戶在網(wǎng)絡(luò)邊緣面臨的一些關(guān)鍵挑戰(zhàn)。該器件擁有低功耗、小尺寸和高性能以及針對(duì)數(shù)據(jù)處理和AI等網(wǎng)絡(luò)邊緣應(yīng)用需求量身定制的優(yōu)化功能集。

Avant-E專為網(wǎng)絡(luò)邊緣處理而生

Avant-E FPGA可用作網(wǎng)絡(luò)邊緣設(shè)備的AI引擎,可以在現(xiàn)場(chǎng)重新編程,幫助系統(tǒng)架構(gòu)師更好地跟上AI創(chuàng)新的步伐,這些優(yōu)勢(shì)是其他處理方案(如ASIC)難以實(shí)現(xiàn)的。Avant-E FPGA架構(gòu)中的分布式資源與現(xiàn)代AI ASIC的架構(gòu)類似,因此能夠以較低的工作頻率并行處理數(shù)據(jù)。與同類競(jìng)品器件相比,Avant-E FPGA的功耗降低2.5倍之多。

Avant-E FPGA還擁有嵌入式存儲(chǔ)器和18 x 18位DSP引擎,每個(gè)可配置為4個(gè)8 x 8位DSP,提高整體處理速度。

優(yōu)化計(jì)算機(jī)視覺流水線

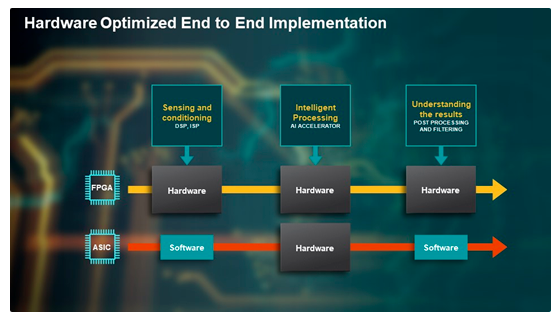

視覺處理是一種需要密集計(jì)算并在網(wǎng)絡(luò)邊緣設(shè)備上進(jìn)行加速的一種應(yīng)用示例。在計(jì)算機(jī)視覺流水線中智能的實(shí)現(xiàn)需要經(jīng)過(guò)三個(gè)階段:感知、思考和行動(dòng)。Avant-E FPGA 支持這三個(gè)關(guān)鍵功能硬件優(yōu)化的端到端實(shí)現(xiàn)。

感知:從一個(gè)或多個(gè)傳感器中采集數(shù)據(jù),進(jìn)行調(diào)整或“清洗”,然后用于智能處理

在預(yù)處理模塊中,Avant-E FPGA擁有靈活的接口,可輕松集成不同類型的傳感器,從而允許更多數(shù)據(jù)更快地進(jìn)入流水線。數(shù)據(jù)或圖像可以根據(jù)需要在接口中進(jìn)行調(diào)整和改進(jìn),然后進(jìn)入到流水線的后續(xù)操作。

思考:使用AI從數(shù)據(jù)中獲取智能

Avant-E的硬件可編程性和超低功耗能夠最小化密集計(jì)算的功耗

行動(dòng):根據(jù)處理后的數(shù)據(jù)做出行動(dòng)

Avant-E FPGA支持硬件加速后處理,減少整個(gè)流水線的延遲。當(dāng)需要在特定時(shí)間范圍內(nèi)執(zhí)行操作時(shí),這一特性非常有利于實(shí)現(xiàn)任務(wù)關(guān)鍵型應(yīng)用。

Avant-E FPGA旨在實(shí)現(xiàn)低延遲的網(wǎng)絡(luò)邊緣設(shè)備,非常適合有著明確時(shí)序要求的應(yīng)用,包括工業(yè)環(huán)境中的機(jī)器視覺、機(jī)器人、機(jī)器人導(dǎo)航和安全攝像頭。例如,自動(dòng)化工廠的傳送帶高速移動(dòng),機(jī)器視覺攝像頭在監(jiān)控傳送帶上的產(chǎn)品時(shí)必須能夠快速感知、思考并處理它接收的數(shù)據(jù),在發(fā)現(xiàn)有瑕疵的產(chǎn)品時(shí),快速將其挑出,進(jìn)行人工檢查。

以超低功耗和超小尺寸實(shí)現(xiàn)性能新高

萊迪思Avant-E FPGA鞏固了萊迪思在低功耗可編程器件領(lǐng)域的領(lǐng)先地位,幫助客戶在現(xiàn)有應(yīng)用中實(shí)現(xiàn)更高水平的網(wǎng)路邊緣處理性能,并通過(guò)擴(kuò)展市場(chǎng)上的計(jì)算機(jī)視覺應(yīng)用類型來(lái)推動(dòng)網(wǎng)絡(luò)邊緣的技術(shù)創(chuàng)新。

正如線上發(fā)布會(huì)所宣布的那樣,萊迪思未來(lái)將推出更多Avant系列產(chǎn)品,為我們的客戶提供更多渠道,充分利用Avant平臺(tái)釋放創(chuàng)新活力。關(guān)注我們的新聞,隨時(shí)了解萊迪思的最新消息,包括新器件上市時(shí)間。

編輯:黃飛

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<