前言:

隨著數(shù)據(jù)的爆炸勢(shì)增長(zhǎng),內(nèi)存墻對(duì)于計(jì)算速度的影響愈發(fā)顯現(xiàn)。

為了減小內(nèi)存墻的影響,提升內(nèi)存帶寬一直是存儲(chǔ)芯片聚焦的關(guān)鍵問(wèn)題。

長(zhǎng)期以來(lái),內(nèi)存行業(yè)的價(jià)值主張?jiān)诤艽蟪潭壬鲜冀K以系統(tǒng)級(jí)需求為導(dǎo)向,已經(jīng)突破了系統(tǒng)性能的當(dāng)前極限。

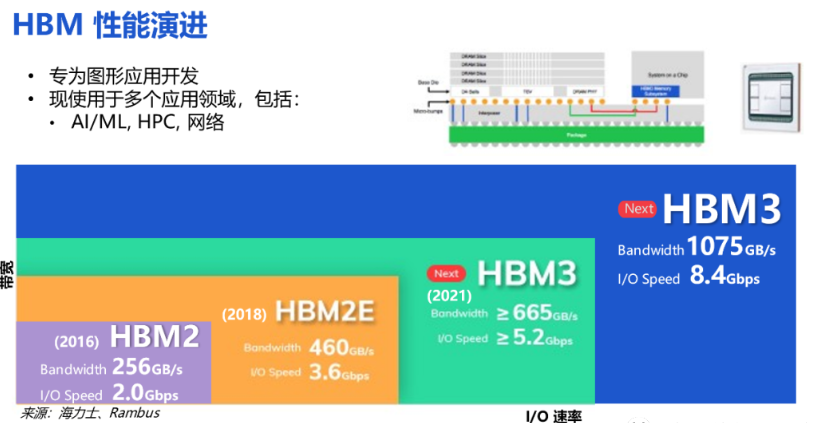

HBM契合半導(dǎo)體發(fā)展趨勢(shì)

作為存儲(chǔ)器市場(chǎng)的重要組成部分,DRAM技術(shù)不斷地升級(jí)衍生。

DRAM從2D向3D技術(shù)發(fā)展,其中HBM是主要代表產(chǎn)品。

HBM(High Bandwidth Memory,高帶寬內(nèi)存)是一款新型的CPU/GPU 內(nèi)存芯片。

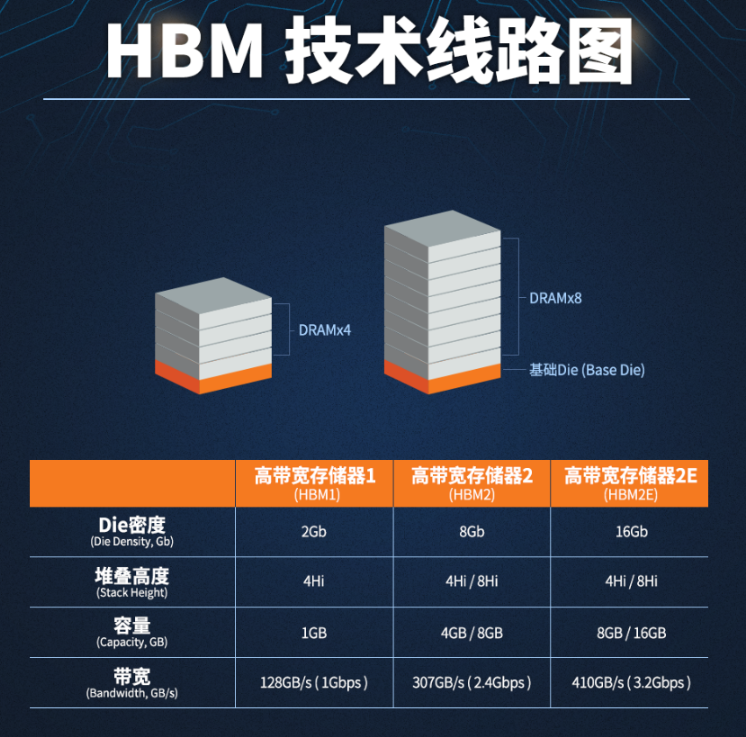

其實(shí)就是將很多個(gè)DDR芯片堆疊在一起后和GPU封裝在一起,實(shí)現(xiàn)大容量,高位寬的DDR組合陣列。

通過(guò)增加帶寬,擴(kuò)展內(nèi)存容量,讓更大的模型,更多的參數(shù)留在離核心計(jì)算更近的地方,從而減少內(nèi)存和存儲(chǔ)解決方案帶來(lái)的延遲。

從技術(shù)角度看,HBM使DRAM從傳統(tǒng)2D轉(zhuǎn)變?yōu)榱Ⅲw3D,充分利用空間、縮小面積,契合半導(dǎo)體行業(yè)小型化、集成化的發(fā)展趨勢(shì)。

JEDEC發(fā)布HBM3標(biāo)準(zhǔn),帶寬翻倍覆蓋更多領(lǐng)域

在堆疊層數(shù)方面,新標(biāo)準(zhǔn)不僅支持4-Hi、8-Hi、12-Hi的硅通孔(TSV)堆棧,同時(shí)還為16-Hi方案實(shí)現(xiàn)做好準(zhǔn)備。

每層8—32Gb的容量密度,可輕松支持4GB(8Gb?4-Hi)到64GB(32Gb?16-Hi)容量密度,預(yù)計(jì)初代產(chǎn)品將基于16Gb存儲(chǔ)層。

為滿足對(duì)高平臺(tái)層級(jí)的可靠性、可用性與可維護(hù)性(簡(jiǎn)稱RAS)需求,HBM3還支持基于符號(hào)的片上ECC、以及實(shí)時(shí)錯(cuò)誤報(bào)告和透明度。

通過(guò)在主機(jī)接口端使用低擺幅(0.4V)信號(hào)和較低的工作電壓(1.1V),進(jìn)一步提升能效表現(xiàn)。

人工智能/機(jī)器學(xué)習(xí)、高性能計(jì)算、數(shù)據(jù)中心等應(yīng)用市場(chǎng)興起,催生高帶寬內(nèi)存HBM并推動(dòng)著其向前走更新迭代。

市場(chǎng)調(diào)研機(jī)構(gòu)Omdia預(yù)測(cè),2025年HBM市場(chǎng)的總收入將達(dá)到25億美元。

巨頭率先抵達(dá)HBM3“戰(zhàn)場(chǎng)”

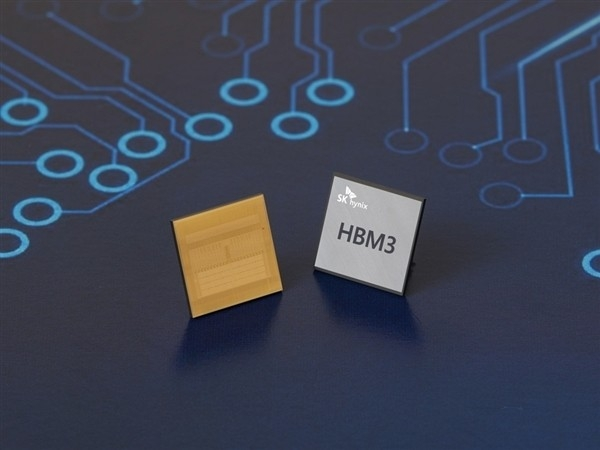

去年10月,SK海力士宣布業(yè)界首次成功開(kāi)發(fā)現(xiàn)有最佳規(guī)格的HBM3 DRAM。

這是SK海力士去年7月開(kāi)始批量生產(chǎn)HBM2E DRAM后,時(shí)隔僅1年零3個(gè)月開(kāi)發(fā)了HBM3。

SK海力士研發(fā)的HBM3可每秒處理819GB的數(shù)據(jù),相當(dāng)于可在一秒內(nèi)傳輸163部全高清電影,與上一代HBM2E相比,速度提高了約78%;

內(nèi)置ECC校檢,可自身修復(fù)DRAM單元的數(shù)據(jù)的錯(cuò)誤,產(chǎn)品可靠性大幅提高。

隨著SK海力士成功開(kāi)發(fā)HBM3,HBM開(kāi)始挺進(jìn)3.0時(shí)代,IP廠商亦已先行布局HBM3。

去年2月,三星電子發(fā)布其集成AI處理器新一代芯片HBM-PIM(processing-in-memory)。

可提供最高達(dá)1.2TFLOPS的嵌入式計(jì)算能力,從而使內(nèi)存芯片本身能夠執(zhí)行通常由CPU、GPU、ASIC或FPGA處理的工作。

HBM-PIM芯片將AI引擎引入每個(gè)存儲(chǔ)庫(kù),從而將處理操作轉(zhuǎn)移到HBM本身。

去年7月,AMD正在研發(fā)代號(hào)為Genoa的下一代EPYC霄龍服務(wù)器處理器,采用Zen4架構(gòu)。

這一處理器將首次配備HBM內(nèi)存,目的是與英特爾下一代服務(wù)器CPU Sapphire Rapids競(jìng)爭(zhēng)。

英特爾和AMD均將在CPU上采用HBM,這也意味著HBM的應(yīng)用不再局限于顯卡,其在服務(wù)器領(lǐng)域的應(yīng)用將有望更加廣泛。

去年10月,Synopsys宣布推出業(yè)界首個(gè)完整的HBM3IP解決方案,包括用于2.5D多芯片封裝系統(tǒng)的控制器、PHY和驗(yàn)證IP。

Design Ware HBM3控制器與PHYIP基于經(jīng)芯片驗(yàn)證過(guò)的HBM2EIP打造,而HBM3 PHYIP基于5nm制程打造,每個(gè)引腳的速率可達(dá)7200Mbps,內(nèi)存帶寬最高可提升至921GB/s。

去年8月,美國(guó)內(nèi)存IP核供應(yīng)商Rambus宣布推出其支持HBM3的內(nèi)存接口子系統(tǒng),內(nèi)含完全集成的PHY和數(shù)字控制器。

數(shù)據(jù)傳輸速率達(dá)8.4Gbps,可提供超過(guò)1TB/s的帶寬,是HBM2E內(nèi)存子系統(tǒng)的兩倍以上。

去年8月,英特爾在其架構(gòu)日上介紹基于XeHPC微架構(gòu)的全新數(shù)據(jù)中心GPU架構(gòu)Ponte Vecchio。

Ponte Vecchio芯片由幾個(gè)以單元顯示的復(fù)雜設(shè)計(jì)構(gòu)成,包括計(jì)算單元、Rambo單元、Xe鏈路單元以及包含高速HBM內(nèi)存的基礎(chǔ)單元。

英特爾也將HBM用在其下一代服務(wù)器CPU Sapphire Rapids上。

在內(nèi)存方面,除了支持DDR5和英特爾@傲騰內(nèi)存技術(shù),還提供了一個(gè)產(chǎn)品版本,該版本在封裝中集成了HBM技術(shù)。

可在HPC、AI、機(jī)器學(xué)習(xí)和內(nèi)存數(shù)據(jù)分析工作負(fù)載中普遍存在的密集并行計(jì)算中實(shí)現(xiàn)高性能。

在 CES 2023 展會(huì)上,AMD披露了面向下一代數(shù)據(jù)中心的 APU 加速卡產(chǎn)品 Instinct MI300,是AMD投產(chǎn)的最大芯片。

這 9 顆小芯片采用有源設(shè)計(jì),不僅可以在I/O瓦片之間實(shí)現(xiàn)通信,還可以實(shí)現(xiàn)與HBM3堆棧接口的內(nèi)存控制器之間的通信,從而帶來(lái)令人難以置信的數(shù)據(jù)吞吐量。

結(jié)尾:

隨著技術(shù)標(biāo)準(zhǔn)化發(fā)展,該技術(shù)應(yīng)用將會(huì)進(jìn)一步擴(kuò)大,擴(kuò)展至用于下一代超級(jí)計(jì)算機(jī)和AI應(yīng)用的HBM3,甚至用于設(shè)備上AI的移動(dòng)存儲(chǔ)器,以及用于數(shù)據(jù)中心的存儲(chǔ)器模塊。

HBM 存儲(chǔ)器對(duì)于面向企業(yè)市場(chǎng)和最終消費(fèi)者的產(chǎn)品來(lái)說(shuō)是一個(gè)非常昂貴的選擇。

隨著人工智能和深度學(xué)習(xí)的不斷發(fā)展,系統(tǒng)已經(jīng)變得對(duì)帶寬需求很大。

HBM處于系統(tǒng)和內(nèi)存性能層級(jí)的頂端,是包括超級(jí)計(jì)算機(jī)、高性能計(jì)算、自動(dòng)駕駛和機(jī)器學(xué)習(xí)等下一代應(yīng)用無(wú)可爭(zhēng)議的技術(shù)推動(dòng)因素。

部分資料參考:IT之家:《AMD 造出最大芯片 Instinct MI300 加速卡》,半導(dǎo)體行業(yè)觀察:《存儲(chǔ)巨頭競(jìng)逐HBM》,天極網(wǎng):《JEDEC發(fā)布HBM3標(biāo)準(zhǔn)》,中國(guó)IDC圈:《HBM3內(nèi)存:向更高的帶寬突破》

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<