雖然摩爾定律已經(jīng)逐漸走到盡頭,但我們卻來到了一個(gè)更加看點(diǎn)十足的時(shí)代,不同于以往每隔18個(gè)月靠工藝迭代帶來的常規(guī)演變,以英特爾、英偉達(dá)和AMD為首的芯片巨頭之間的競(jìng)爭(zhēng)變得異常激烈。

從英特爾、英偉達(dá)、AMD三家的產(chǎn)品布局來看,三家?guī)缀醵技R了CPU、GPU甚至是DPU產(chǎn)品線。如今,他們正在醞釀更大的規(guī)劃!

隨著近日AMD推出CPU和GPU組合的下一代數(shù)據(jù)中心APU——Instinct MI300,自此,三家的“多PU組合”爭(zhēng)斗戰(zhàn)已然打響。

在此之前,英特爾的Falcon Shores XPU混合搭配CPU + GPU,英偉達(dá)的Grace Hopper Superchip是Grace CPU + H100 GPU的組合,都是如出一轍。

他們都在做一件偉大的事情:在一個(gè)芯片中集成CPU、GPU和AI加速器,最終成為一個(gè)類似APU的產(chǎn)品,目標(biāo)是更廣闊的超級(jí)計(jì)算市場(chǎng)。

但是在實(shí)現(xiàn)方式上,英偉達(dá)落后了?

英特爾的XPU計(jì)劃之一:Falcon Shores

首先來說下英特爾的XPU計(jì)劃?XPU是指使用多種計(jì)算架構(gòu)以最好地滿足單個(gè)工作負(fù)載的執(zhí)行需求的想法,這是英特爾過去幾年來最感興趣的一個(gè)方向。

英特爾希望將X86和Xe結(jié)合起來用于超級(jí)計(jì)算/HPC市場(chǎng)。這也導(dǎo)致了英特爾開始研發(fā)從CPU、GPU個(gè)一些ASIC產(chǎn)品(如IPU、VPU、FPGA)等等各種產(chǎn)品。

在英特爾2022年年度投資者會(huì)議上,英特爾披露了一個(gè)代號(hào)為Falcon Shores的處理器新架構(gòu),它將x86 CPU和Xe GPU硬件組合到單個(gè)Xeon插槽芯片中,利用下一代封裝、內(nèi)存和 I/O 技術(shù),為計(jì)算大型數(shù)據(jù)集和訓(xùn)練巨大 AI 模型的系統(tǒng)提供巨大的性能和效率改進(jìn)。

不過英特爾的目標(biāo)似乎不僅僅是將CPU和GPU集成在一起,英特爾正在尋求為擁有絕對(duì)海量數(shù)據(jù)集HPC用戶開辟市場(chǎng)——這種數(shù)據(jù)集無法輕松適應(yīng)獨(dú)立GPU相對(duì)有限的內(nèi)存容量。

Falcon Shores的目標(biāo)是在2024年推出,采用埃米級(jí)制程,這意味著它可能會(huì)使用Intel 20A或Intel 18A制造工藝制造。

英特爾預(yù)計(jì)Falcon Shores在多個(gè)指標(biāo)上比當(dāng)前一代產(chǎn)品增長5倍,包括每瓦性能提高5倍,單個(gè) (Xeon) 插槽的計(jì)算密度提高5倍,內(nèi)存容量增加5倍,內(nèi)存帶寬增加5倍。

圖源:pcper

英特爾表示,F(xiàn)alcon Shores的混合設(shè)計(jì)是通過使用tile(也稱為小芯片)實(shí)現(xiàn)的,通過提供x86和Xe內(nèi)核之間的靈活比例,這將使芯片制造商在設(shè)計(jì)過程的后期配置芯片方面具有更大的靈活性。

AMD發(fā)布Instinct MI300 APU

近日,AMD在CES 2023上披露了其下一代數(shù)據(jù)中心處理器Instinct MI300,被AMD稱之為下一代數(shù)據(jù)中心APU。它采用了13個(gè)Chiplet,共有1460億個(gè)晶體管,MI300可以說是AMD迄今為止最大的芯片。

該芯片的計(jì)算部分由九個(gè)5nm小芯片組成,它們包含CPU或GPU內(nèi)核,但AMD沒有詳細(xì)說明每個(gè)小芯片的使用數(shù)量。

這九個(gè)裸片被3D堆疊在四個(gè)6nm基礎(chǔ)裸片之上,而且這些裸片是有源的中介層,可以處理 I/O和各種其他功能。從下圖中可以清晰的看到,Instinct MI300中心芯片側(cè)面的八個(gè)HBM3堆棧。

圖源:Future

MI300的關(guān)鍵優(yōu)勢(shì)除了將CPU內(nèi)核和GPU內(nèi)核放在同一設(shè)計(jì)中的操作簡(jiǎn)單性之外,還在于它可以讓兩種處理器類型共享一個(gè)高速、低延遲的統(tǒng)一內(nèi)存空間。

這將使在CPU和GPU兩個(gè)核之間快速且輕松的傳遞數(shù)據(jù),能讓每個(gè)核處理他們最擅長的計(jì)算方面。此外,它還可以通過讓兩種處理器類型直接訪問同一內(nèi)存池,簡(jiǎn)化插槽級(jí)別的HPC編程。

但是MI300芯片并不是批量產(chǎn)品,因?yàn)槠鋬r(jià)格昂貴且相對(duì)稀缺,所以它們不會(huì)像EPYC Genoa數(shù)據(jù)中心CPU那樣得到廣泛部署。AMD預(yù)計(jì)將在2023年下半年交付Instinct MI300。

但是,這一Chiplet的設(shè)計(jì)技術(shù)將會(huì)衍生出更多的變體。

英偉達(dá)Grace Hopper Superchip

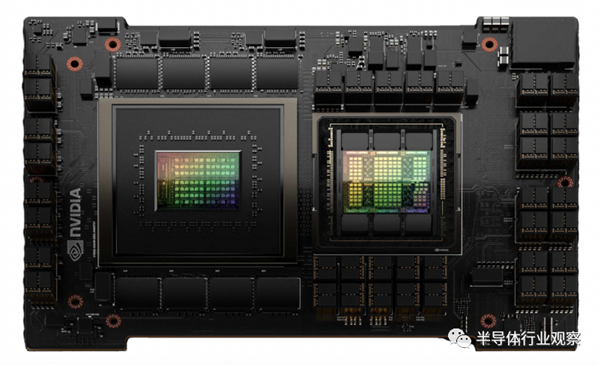

不同于英特爾和英偉達(dá)采用Chiplet架構(gòu)的做法,英偉達(dá)首款GPU+CPU組合——Grace Hopper Superchip還是單芯片的方式,下圖是渲染圖。

Nvidia對(duì)其Grace Superchip的渲染圖:兩個(gè)帶有RAM的處理器合二為一

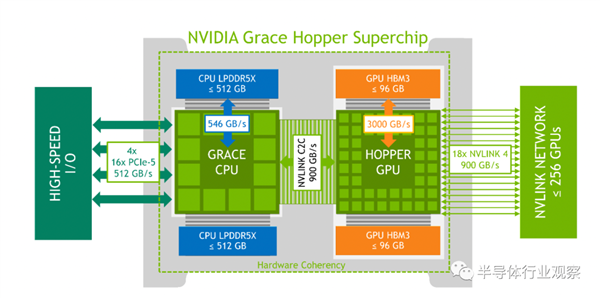

NVIDIA?Grace Hopper架構(gòu)將NVIDIA Hopper GPU與NVIDIA Grace? CPU結(jié)合在一起,在單個(gè)超級(jí)芯片中連接高帶寬和內(nèi)存一致的NVIDIA NVLink Chip-2-Chip(C2C)?互連,并支持新的NVIDIA NVLink開關(guān)系統(tǒng)。

NVLink C2C是NVIDIA為超級(jí)芯片開發(fā)的內(nèi)存相干、高帶寬和低延遲互連。它是Grace Hopper超級(jí)芯片的核心,提供高達(dá)900 GB/s的總帶寬。這比加速系統(tǒng)中常用的x16 PCIe Gen5通道的帶寬高7倍。

結(jié)合NVIDIA NVLink切換系統(tǒng),所有運(yùn)行在最多256個(gè)NVLink連接的GPU上的GPU線程現(xiàn)在都可以以高帶寬訪問高達(dá)150TB的內(nèi)存。

NVIDIA Grace Hopper超級(jí)芯片邏輯一覽(圖源:英偉達(dá))

英偉達(dá)表示,該超級(jí)芯片將為運(yùn)行TB級(jí)數(shù)據(jù)的應(yīng)用程序提供高達(dá)10倍的性能提升,英偉達(dá)已承諾在2023年上半年推出其超級(jí)芯片。

可以看出,英特爾、英偉達(dá)和AMD都開始在CPU+GPU組合上發(fā)力,他們所采用的方式:要么芯片繼續(xù)平鋪?zhàn)龃螅雌?D堆疊、Chiplet、拼架構(gòu)。

目前從各家的CPU+GPU組合型產(chǎn)品推出的時(shí)間上來看,AMD和英偉達(dá)都在2023年,而英特爾將在2024年。軟件支持方面,英特爾有oneAPI,英偉達(dá)有CUDA,AMD似乎還稍遜一些。

而在架構(gòu)方面,英特爾、AMD均已奔向3D Chiplet,但英偉達(dá)似乎仍在單芯片上努力。

英偉達(dá)何時(shí)擁抱Chiplet?

Chiplet用于CPU已經(jīng)不是新聞了,AMD多年來一直在其Ryzen和Epic等CPU處理器中使用Chiplet設(shè)計(jì)并取得了巨大成功。

英特爾也于2023年1月11日正式發(fā)布了基于Chiplet設(shè)計(jì)的第四代至強(qiáng)CPU-Sapphire Rapids,它通過內(nèi)置加速器將目標(biāo)工作負(fù)載的平均每瓦性能提升了2.9倍,在優(yōu)化電源模式下每個(gè)CPU節(jié)能可高達(dá)70瓦,將總體成本降低52%-66%。

但是就目前的情況來看,GPU也已邁入了Chiplet時(shí)代。

如今英特爾和AMD已經(jīng)均已發(fā)布了3D Chiplet CPU和GPU中的產(chǎn)品。

而英偉達(dá)無論是GPU還是CPU似乎還在單芯片上努力,英偉達(dá)要落后了嗎?

2023年1月11日,英特爾發(fā)布了其首款Chiplet小芯片封裝的GPU,代號(hào)Ponte Vecchio,GPU Max系列單個(gè)產(chǎn)品整合47個(gè)小芯片,集成超過1000億個(gè)晶體管。

這是英特爾性能最高、密度最高的通用獨(dú)立GPU。英特爾的這一芯片的具體性能對(duì)比情況暫未可知,但是我們暫且可以看看AMD與英偉達(dá)的GPU性能對(duì)比。

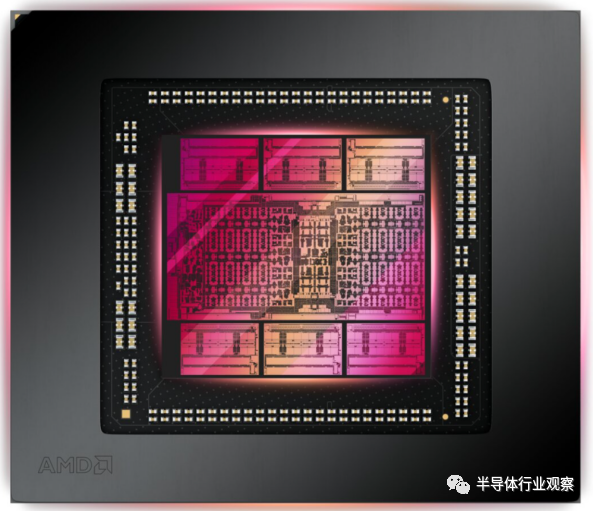

AMD最新一代的GPU Navi 31,是AMD第一款、也可以說是歷史上第一個(gè)基于Chiplet設(shè)計(jì)的GPU,AMD的兩款最新顯卡Radeon RX 7900 XTX和Radeon RX 7900 XT均是基于Navi 31。

其中,XTX是旗艦機(jī)型,擁有更多的shader處理器,更高的內(nèi)存帶寬,更多的顯存,而XT則是有些弱化的版本。

如果我們將AMD的顯卡和英偉達(dá)的RTX 4080作對(duì)比,AMD的GPU的性能非常接近英偉達(dá)的RTX 4080。

據(jù)chipsandcheese的評(píng)測(cè)對(duì)比數(shù)據(jù),如下圖所示,英偉達(dá)的4080采用4nm制程,晶體管密度比AMD的低一些,面積也更大一些,但英偉達(dá)4080具有更高的SM數(shù)量,這意味著寄存器文件和FMA單元相比AMD要有更多的邏輯控制。

英偉達(dá)還具有更簡(jiǎn)單的緩存層次結(jié)構(gòu)的優(yōu)勢(shì),它仍然提供相當(dāng)大的緩存容量。

AMD 7900/6900與英偉達(dá)4080的比較(圖源:chipsandcheese)

英偉達(dá)的GPU目前做法還是將所有的晶體管,都放在一個(gè)更大的單芯片上,采用尖端工藝4納米節(jié)點(diǎn)。

而AMD的Navi 31基于Chiplet設(shè)計(jì)和先進(jìn)的RDNA3架構(gòu)。其裸片由GCD核(圖形計(jì)算芯片)和 MCD內(nèi)存小芯片(內(nèi)存緩存芯片)組成。

從下圖可以清晰的看到,中間部分是5nm制程的GCD核,周圍分別是6顆6nm制程的MCD,包含內(nèi)存控制器和Infinity緩存。

這說明,著色器處理器和其他單元比較獲益于先進(jìn)工藝,而對(duì)于內(nèi)存控制器和緩存來說則不必需要使用最先進(jìn)的工藝。

AMD Navi 31裸片(圖源:AMD)

兩種不同工藝的芯片組裝在一起,所使用的尺寸更小,與此同時(shí),Chiplet的設(shè)計(jì)方式使得晶圓的缺陷芯片數(shù)量也少的多,從這個(gè)意義上來說,Chiplet架構(gòu)的使用降低了成本。

Chiplet的設(shè)計(jì)還助于通過在圖形芯片上使用更少的區(qū)域來實(shí)現(xiàn)VRAM連接,從而實(shí)現(xiàn)更高帶寬的 VRAM 設(shè)置。但是也不是萬利的,代價(jià)就是AMD必須支付更昂貴的封裝解決方案,因?yàn)楹?jiǎn)單的封裝走線在處理GPU的高帶寬要求方面表現(xiàn)不佳。

此外,AMD Navi 31 GPU很重要的一項(xiàng)創(chuàng)新是Infinity Link總線,為何要說到這個(gè)呢?

因?yàn)镃hiplet的設(shè)計(jì)方式肯定會(huì)產(chǎn)生更多的延遲,而GPU是對(duì)延遲極其敏感的,所以AMD特意為此開發(fā)了全新的Infinity Link總線(即 Infinity Fanout Links 系統(tǒng))來連接GDC和MCD部件,從而在GCD和MCD小芯片部件之間實(shí)現(xiàn)5.3 TB/s的帶寬,這種超級(jí)先進(jìn)的互連系統(tǒng)無疑是小芯片GPU設(shè)計(jì)的關(guān)鍵決定因素。

可以說,AMD的Navi 31為圖形處理器世界帶來了真正革命性的小芯片GPU設(shè)計(jì),如果這一設(shè)計(jì)取得成功,那么未來GPU就可以不用依賴先進(jìn)工藝來提升性能,而是通過堆疊更多的GCD來實(shí)現(xiàn)。GPU市場(chǎng)迎來新的戰(zhàn)爭(zhēng)。

寫在最后

3D IC設(shè)計(jì)逐漸成為了主流,Chiples也進(jìn)一步崛起,在芯片大廠的推動(dòng)下,基于Chiplet的3D IC設(shè)計(jì)進(jìn)一步展示了其說服力。Chiplet將徹底改變這個(gè)行業(yè)。

英偉達(dá)何時(shí)采用Chiplet,備受業(yè)界關(guān)注,不過估計(jì)也快了,畢竟黃仁勛已指出,"Moore's Law is dead" 。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<