邏輯縮放

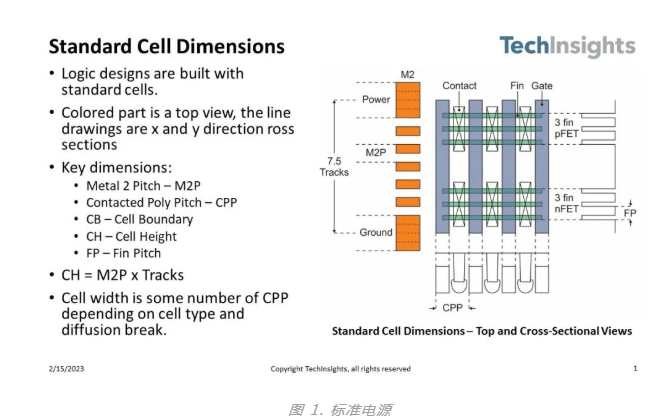

邏輯設計由標準單元(standard cells)組成,如果您要擴展邏輯以增加密度,則標準單元必須縮小。

標準單元的高度通常表征為M2P (Metal-2 Pitch) 乘以軌道(tracks)數(shù)。雖然這是一個有用的指標,但它掩蓋了單元高度還必須包含構成單元的設備這一事實。圖說明了一個 7.5 軌道標準單元,并在單元左側顯示了 M2P 和軌道,并且在單元右側是相應器件結構的橫截面圖。

標準單元的寬度由一定數(shù)量的CPP(Contacted Poly Pitches ) 組成,其數(shù)量取決于單元類型以及如何處理單元邊緣的擴散中斷(diffusion breaks )。再一次說明,CPP 是由一個器件結構組成的,當 CPP 微縮時,它必須微縮。圖 1 說明了 CPP,底部是器件結構的橫截面圖。

圖 1. 標準電源

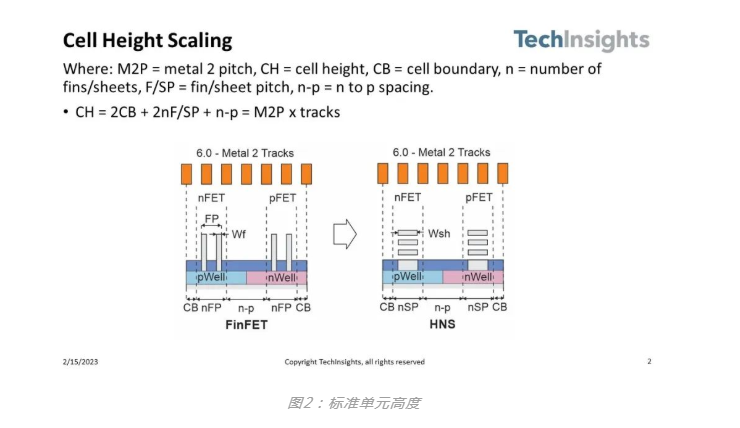

英特爾、三星和臺積電都已從平面器件轉向 FinFET,目前正處于向水平納米片 (HNS) 過渡的初期階段。目前三星正在量產HNS,英特爾和臺積電分別公布了2024年和2025年的HNS量產目標。

圖 2 說明了構成單元高度的器件結構和尺寸。

向 HNS 的轉變提供了多種縮小單元高度的機會。HNS 可以用單個納米片堆疊替代多鰭(multiple fin) nFET 和 pFET 器件,從而縮小器件的高度影響。Forksheet 和 CFET 對 HNS 的增強可以減少甚至消除 np 間距。

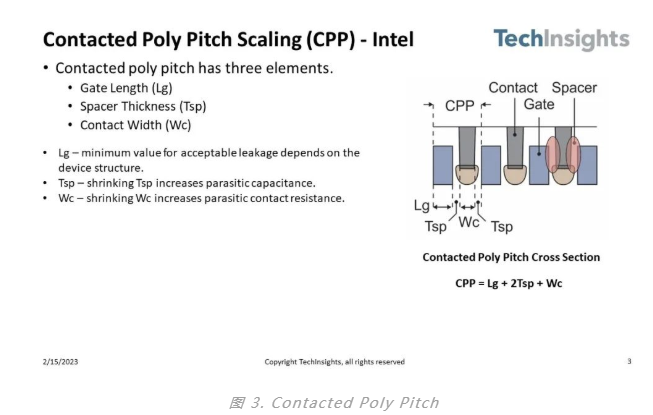

CPP 由柵極長度 (Lg:Gate Length)、間隔層厚度 (Tsp:Spacer Thickness ) 和接觸寬度 (Wc:Contact Width) 組成,見圖 3。

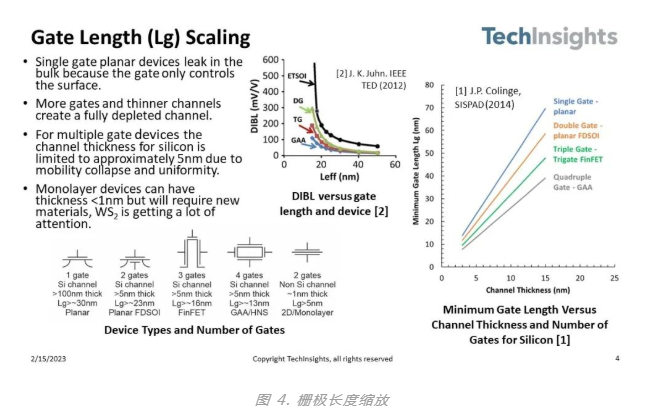

可以通過降低 Lg、Tsp 或 Wc 或三者的任意組合來縮小 CPP。Lg 受設備提供可接受泄漏能力的限制。圖 4 說明了各種器件的 Lg 長度。

從圖 4 可以看出,限制溝道厚度和/或增加柵極數(shù)量可以縮短 Lg。

所謂的 2D 材料由厚度小于 1nm 的單層材料組成,改善了對溝道的柵極控制并使 Lg 降至約 5nm。在這些尺寸下,硅的遷移率很低,使用具有更高遷移率和更高帶隙的其他材料可以進一步減少泄漏。將 Lg 縮小到 ~5nm 的能力可以顯著縮小 CPP,從而縮小標準單元。

二維材料挑戰(zhàn)

過渡金屬二硫族化物 (TMD:Transition Metal Dichalcogenides),例如 MoS2、WS2或 WSe2,已被確定為在單層厚度下具有高遷移率的感興趣材料(硅在這些維度上具有較差的遷移率)。要實際使用這些材料,需要解決幾個挑戰(zhàn)/問題,這也是文章談到的7篇論文中探討的挑戰(zhàn)/問題:

器件性能——用這些材料制造的器件是否真的能在短 Lg 下提供良好的驅動電流和低泄漏。

觸點——2D TMD films是原子級別的光滑且難以形成良好的低電阻接觸。

成膜——目前在藍寶石襯底上使用高溫 MOCVD 形成 2D films,然后將生成的薄膜轉移到 300mm 硅晶圓上進行進一步處理。這不是一個實際的生產過程。

呈現(xiàn)的結果

在由英特爾CJ Dorow 等人撰寫的論文 7.5 “Gate length scaling beyond Si: Mono-layer 2D Channel FETs Robust to Short Channel Effects”中,他們基于AI對材料性能進行了探索。

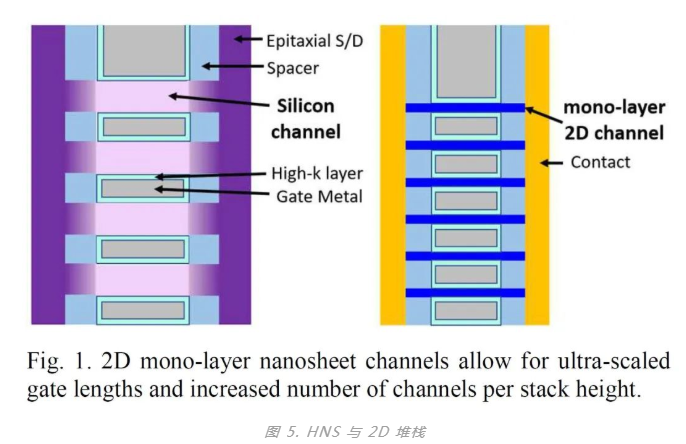

根據(jù)該文章介紹,基于 2D 材料的設備的最終目標是堆疊類似于 HNS 堆疊的 2D 層,但每個溝道更薄,從而實現(xiàn)更短的 Lg 和堆疊中的更多層。圖 5 說明了差異。

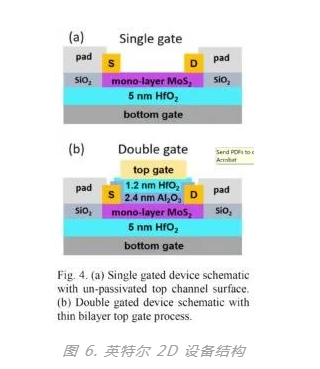

英特爾在背柵(back gate)上濕法轉移了 MBE 生長的 MoS2薄膜,然后評估了帶有背柵和附加前柵(front gate)的器件,并得出了源極-漏極距離為 25nm。圖 6 說明了器件結構。

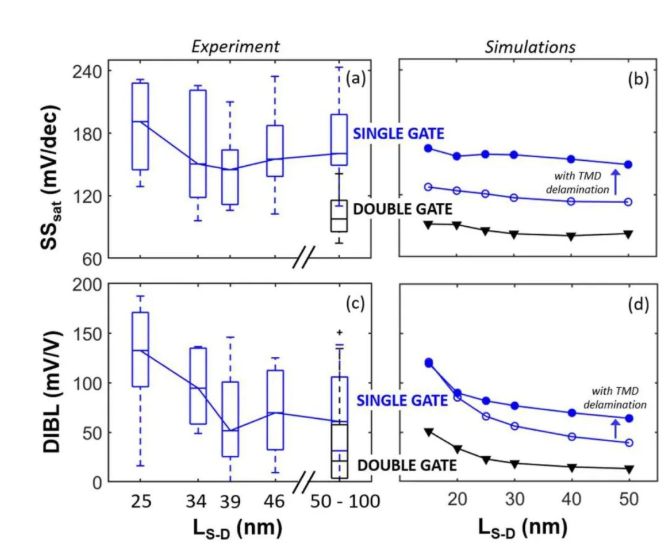

英特爾在他們的實驗中遇到了一些分層問題,但能夠通過實驗確認他們的建模結果,并得出結論,雙柵極設備應該能夠縮小到至少 10 納米,并具有低泄漏,見圖 7。

圖 7. 實驗結果(左側)和仿真結果(右側)

在臺積電Mahaveer Sathaiya等人撰寫的論文 28.4 “Comprehensive Physics Based TCAD Model for 2D MX2 Channel Transistors”中, 他們討論了 2D 設備的綜合仿真模型,并針對 3 個數(shù)據(jù)集校準了該模型。能夠準確地對 2D 設備建模將是該技術進一步發(fā)展的關鍵。

在臺積電Ning Yang 等人撰寫的論文 28.1 “Computational Screening and Multiscale Simulation of Barrier-Free Contacts for 2D Semiconductor pFETs”中, 。他們使用從頭計算的方法來篩選 2D 設備的接觸材料。

按照他們的計算,WSe2接觸電阻的最佳報告實驗結果為950 Ω·μm,在這項工作中,Co3Sn2S2預計能夠達到接近量子極限的20 Ω·μm。此外,模擬設備預計會產生約 2 mA/μm 的狀態(tài)電流。在藍寶石襯底上進行濺射,然后進行高溫退火工藝 (800 °C),結果表明可以生成具有預期化學成分和晶體結構的Co3Sn2S2。

在臺積電的Ang-Sheng Chou等人撰寫的論文 7.2,“High-Performance Monolayer WSe2 p/n FETs via Antimony-Platinum Modulated Contact Technology towards 2D CMOS Electronics”中,他們介紹了 Sb-Pt 調制觸點(modulated contacts)的實驗結果,該觸點在 WSe2上實現(xiàn)了創(chuàng)紀錄的接觸電阻——pFET 為 750 Ω·μm,nFET 為 1,800 Ω· μm,并實現(xiàn)了約 150 μA/μm 的導通電流。這些結果不如論文 28.1 中的預測好,但代表了實驗結果與模擬結果。

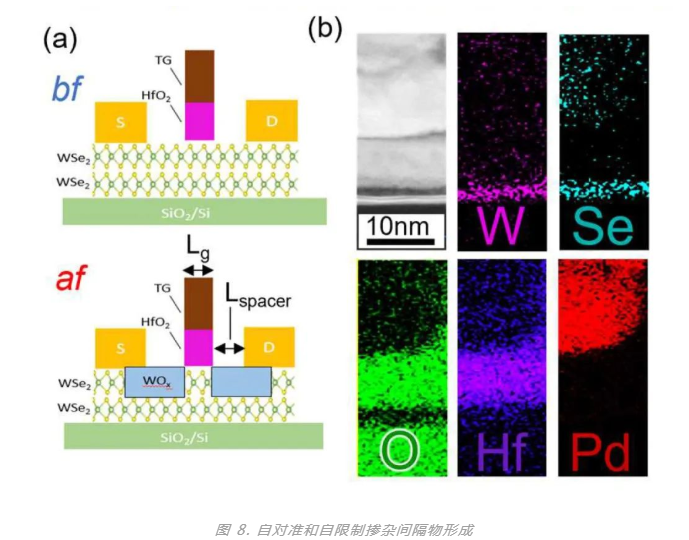

在臺積電公司Terry YT Hung 等人的論文 7.3 “pMOSFET with CVD-grown 2D semiconductor channel enabled by ultra-thin and fab-compatible spacer doping”中,他們介紹了致力于生產類型的 pFET。許多 2D 材料工作是在肖特基二極管上完成的,但 MOSFET 具有較低的接入電阻。為了創(chuàng)建實用的 MOSFET,需要一個帶有摻雜間隔物的 CVD 生長溝道。在本文中,通過用O2等離子體處理WSe2以產生 WOx作為摻雜劑來產生斷帶隙摻雜間隔物。該過程是自對準和自限制的,如圖 8 所示。

CVD 生長的 2D 層仍然單獨生長然后轉移,但該過程的其他部分與生產兼容。該器件實現(xiàn)了最低的 Rc——約為1,000 Ω·μm 。

具有WSe2溝道和相對較高的 Ion > 10-5 A/μm 的晶體管,以獲得良好的 SS < 80mV/dec。

在臺積電Tsung-En Lee 等人撰寫的論文 7.4 “Nearly Ideal Subthreshold Swing in Monolayer MoS2 Top-Gate nFETs with Scaled EOT of 1 nm”中,他們展示了在具有頂柵(top gate)的CVD 生長的MoS2上的 ALD 生長的~1nm EOT 的基于 Hf 的柵極氧化物,并實現(xiàn)了低泄漏和 68 MV/dec 的近乎理想的亞閾值擺幅。TMD 材料上的無針孔氧化物很難實現(xiàn),這項工作顯示出優(yōu)異的結果。

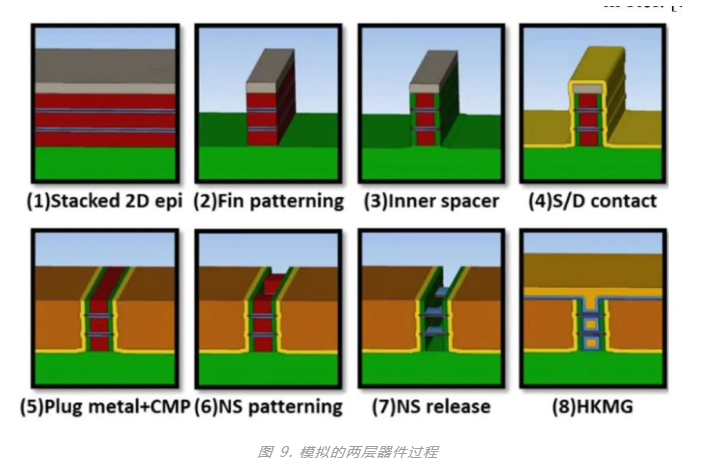

最后一篇論文34.5是臺積電Yun-Yan Chung 等撰寫的“First Demonstration of GAA Monolayer-MoS2 Nanosheet nFET with 410 μA/μm ID at 1V VD at 40nm gate length”,在文中,臺積電公司的人展示了采用集成工藝流程制造的具有良好性能的MoS2器件。

圖 9. 說明了兩層設備堆棧的工藝流程模擬。

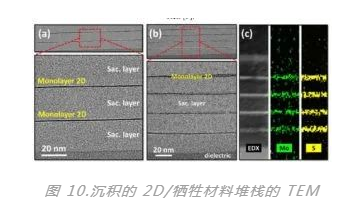

盡管本文仍需要進一步研究,但順序沉積(equentially deposited)了2和 4 堆 TMD 和犧牲材料(sacrificial material )。

圖 10. 顯示了所得疊層的 TEM 圖像。

二維材料和犧牲層的順序沉積與薄膜轉移相比是一種生產類型更多的工藝,而且成本也可能更低。

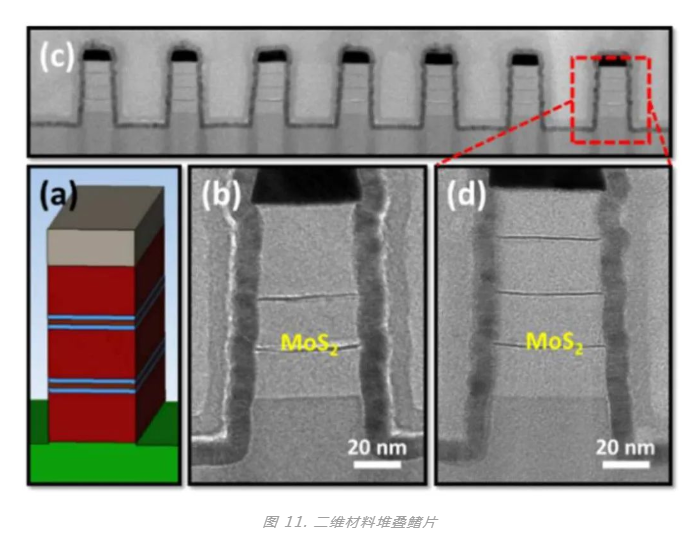

然后使用金屬硬掩模將所得堆疊蝕刻成鰭狀物。圖 11. 說明了“fin”形成的結果。

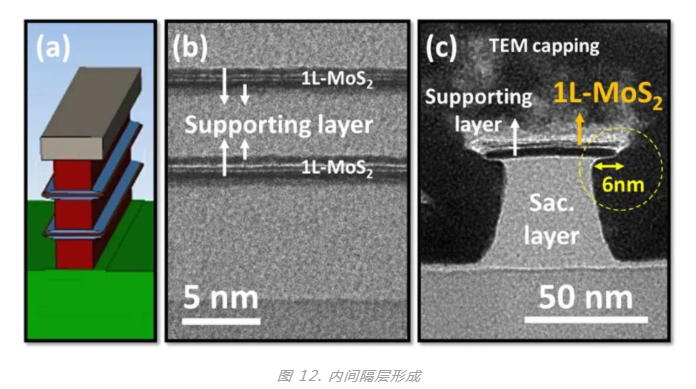

與水平納米片堆疊的情況一樣,需要內部間隔物來減少電容。為了形成內部間隔,需要額外的犧牲材料來防止 2D 層坍塌。圖 12. 說明了內部間隔過程。

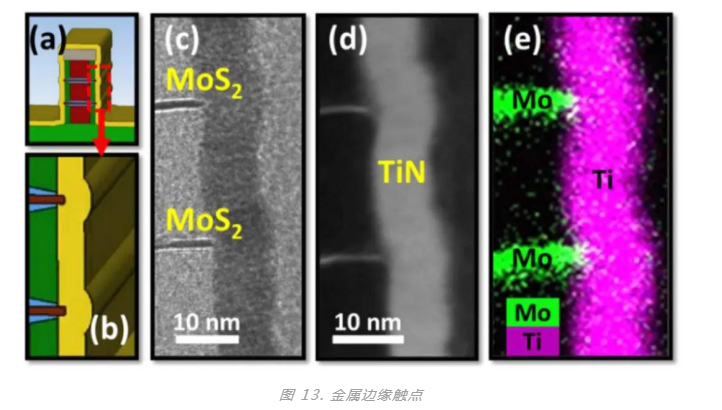

最后,形成金屬邊緣觸點,并釋放溝道。圖 13. 說明了金屬邊緣觸點。

由于在接觸區(qū)和延伸區(qū)中沒有摻雜,所得器件具有高接觸電阻。如圖演示了具有 40nm Lg 的 1 層器件,Vth 約為 0.8 伏,SS 約為 250 mV/dec,驅動電流為 410 μA/μm。

通過這 7 篇論文,說明了在 2D 設備方面取得的巨大進步以及兩家領先設備生產商的興趣水平。我最近完成的一些預測表明,二維 CFET 的邏輯密度可以達到目前最密集的生產標準單元的 5 倍。二維 CFET 可能是 2030 年代的技術,而不是 2020 年代的技術,這表明邏輯擴展遠未結束。

參考資料

https://semiwiki.com/semiconductor-services/ic-knowledge/324910-iedm-2023-2d-materials-intel-and-tsmc/

https://semiwiki.com/semiconductor-services/ic-knowledge/324910-iedm-2023-2d-materials-intel-and-tsmc/