摘要

本文介紹用于在低功耗信號(hào)鏈應(yīng)用中實(shí)現(xiàn)優(yōu)化能效比的精密低功耗信號(hào)鏈解決方案和技術(shù)。本文將介紹功耗調(diào)節(jié)、功率循環(huán)和占空比等用于進(jìn)一步降低系統(tǒng)功耗的技術(shù)(不僅限于選擇低功耗產(chǎn)品,這有時(shí)并不夠)。還將探討如何使用通道時(shí)序控制器、FIFO和電壓監(jiān)控模塊等片內(nèi)特性來簡(jiǎn)化系統(tǒng)設(shè)計(jì),并在主機(jī)控制器側(cè)和整個(gè)系統(tǒng)層面實(shí)現(xiàn)節(jié)能。

簡(jiǎn)介

對(duì)于在幾十年之前的廣告中演奏兔子舞曲的小鼓來說,最執(zhí)著的事情就是能夠持續(xù)不斷地進(jìn)行演奏。在為現(xiàn)場(chǎng)儀器儀表(檢測(cè)溫度、壓力或流量)或遠(yuǎn)程生命體征監(jiān)測(cè)設(shè)備等應(yīng)用設(shè)計(jì)電池供電的測(cè)量系統(tǒng)時(shí),低功耗信號(hào)鏈至關(guān)重要。甚至對(duì)于主電源供電的系統(tǒng),也需要最大限度降低環(huán)境影響或能源成本,這促使硬件設(shè)計(jì)人員不斷改善系統(tǒng)的能效比。低功耗設(shè)計(jì)能夠帶來一些間接性的優(yōu)勢(shì),比如,如果能夠減少并聯(lián)的電池的數(shù)量,解決方案的尺寸會(huì)隨之減小。低功耗設(shè)計(jì)還具有更深層次的優(yōu)勢(shì),因?yàn)橄到y(tǒng)耗費(fèi)的能量更少,使得IC芯片的溫度也更低。這有助于延長(zhǎng)產(chǎn)品的使用壽命。

要在短時(shí)間內(nèi)完成低功耗硬件設(shè)計(jì),從精密低功耗信號(hào)鏈著手會(huì)是一個(gè)非常不錯(cuò)的起點(diǎn)。除了選擇低功耗元件之外,還可以采用多種功率優(yōu)化技術(shù)來進(jìn)一步降低系統(tǒng)功耗,例如功耗調(diào)節(jié)、功率循環(huán)和占空比。此外,很多設(shè)計(jì)選項(xiàng),例如選擇合適的電阻值或使用存儲(chǔ)器也是非常重要的因素,關(guān)乎著能夠?qū)崿F(xiàn)嚴(yán)格的低功耗目標(biāo)和優(yōu)化的電池壽命。

例如,找出信號(hào)鏈中可以取消的構(gòu)建模塊,或者在達(dá)到某些條件時(shí)會(huì)暫時(shí)斷電的模塊,會(huì)有助于我們采用低功耗技術(shù)。這需要精準(zhǔn)的時(shí)序分析1, 2,并對(duì)電路操作分級(jí)或調(diào)節(jié)占空比。如果多個(gè)構(gòu)建模塊多數(shù)時(shí)間都處于閑置狀態(tài),即可讓這些模塊進(jìn)入關(guān)斷模式或者直接將它們關(guān)閉。注意,與使用關(guān)斷模式相比,設(shè)備進(jìn)行全功率循環(huán)會(huì)對(duì)功率和時(shí)序產(chǎn)生一些影響。

在正確采用這種時(shí)序之后,可以通過盡可能減少微控制器互動(dòng)來進(jìn)一步改善主系統(tǒng)層級(jí)的功耗。這就需要使用外部或內(nèi)部存儲(chǔ)器,以便在主機(jī)控制器被關(guān)斷之后存儲(chǔ)數(shù)據(jù)。

在系統(tǒng)層面應(yīng)用節(jié)能技術(shù)會(huì)有一些差異,具體取決于使用哪種類型的ADC來數(shù)字化傳感器信息,包括SAR ADC和∑-? DAC,關(guān)于這一點(diǎn)將在后續(xù)章節(jié)中詳細(xì)介紹。此外,硬件設(shè)計(jì)選擇,例如數(shù)字通信上拉/下拉電阻、電阻分壓器和增益設(shè)置電阻等也會(huì)影響整體的信號(hào)鏈功耗。

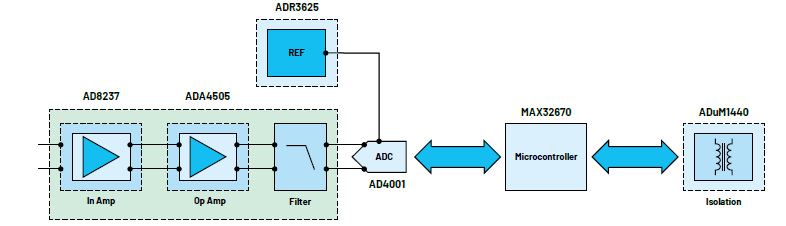

圖1.SAR ADC信號(hào)鏈中的單通道電壓、電流測(cè)量。

引腳命名會(huì)因設(shè)備而異。為了保持一致性,我們用AVDD表示模擬電源,用VIO表示數(shù)字電源,用VREF表示基準(zhǔn)電壓。

基于SAR ADC的信號(hào)鏈的功率優(yōu)化

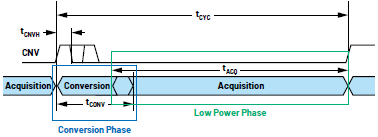

SAR ADC按要求執(zhí)行轉(zhuǎn)換,也就是說,在確認(rèn)轉(zhuǎn)換開始(CONVERSION START)命令之后,從采樣模式切換到保持模式3。轉(zhuǎn)換流程開始,然后,待該流程完成后,SAR ADC會(huì)回到采樣模式,以獲取信號(hào)。SAR ADC(例如圖1所示的信號(hào)鏈中使用的AD4001轉(zhuǎn)換器)在轉(zhuǎn)換階段會(huì)消耗大部分功率,而在圖2所示的采集階段則消耗最少功率。所以,盡管吞吐量能高達(dá)幾個(gè)MSPS,但還是可以按照應(yīng)用要求的最低速度來運(yùn)行這些轉(zhuǎn)換器,以大幅優(yōu)化功率。

SAR ADC:隨吞吐量調(diào)節(jié)功率

在許多低功耗應(yīng)用中,無(wú)需持續(xù)提供傳感器信息,而是以更低的速度提供,可能是按幾kSPS或幾十kSPS。在這些情況下,可以隨吞吐量降低SAR ADC的功耗,包括模擬電源軌和數(shù)字電源軌。

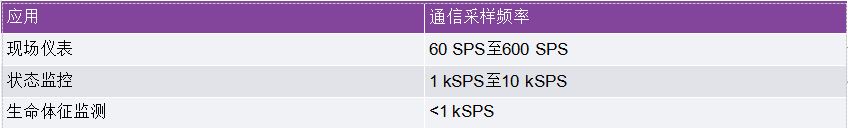

表1.不同終端應(yīng)用中的通信采樣頻率

應(yīng)用通信采樣頻率

現(xiàn)場(chǎng)儀表60 SPS至600 SPS

狀態(tài)監(jiān)控1 kSPS至10 kSPS

生命體征監(jiān)測(cè)<1 kSPS

大部分精密SAR ADC都內(nèi)置時(shí)鐘,用于管理轉(zhuǎn)換流程,因此其轉(zhuǎn)換時(shí)間(tCONV)是固定的。在tCONV固定的情況下,吞吐量越低,循環(huán)時(shí)間(tCYC)越長(zhǎng),采集時(shí)間(tACQ)也就越長(zhǎng),后者就是ADC保持最小功耗的時(shí)長(zhǎng)。換句話說,吞吐率越低,采集每個(gè)樣本所用的功耗也越低。

圖2.SAR ADC時(shí)序圖。

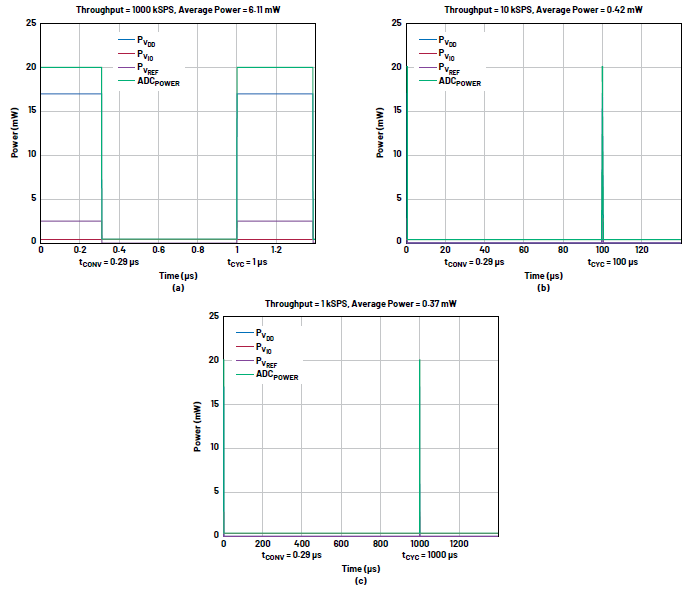

圖3.AD4001 SAR ADC時(shí)序圖和在一個(gè)循環(huán)內(nèi)的功耗。循環(huán)時(shí)間越長(zhǎng),平均功耗越低:(a) 1 μs平均功率 = 6.1113 mW,(b) 10 μs平均功率 = 0.93756 mW,(c) 1 ms平均功率 = 0.36845 mW。

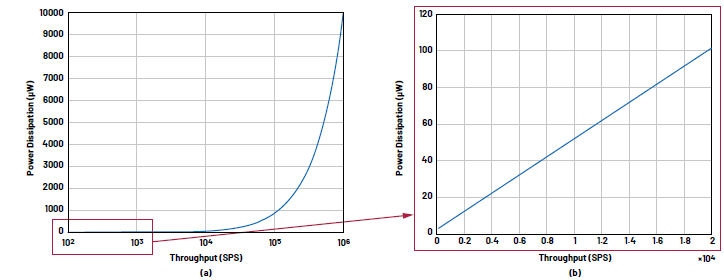

圖4.(a) AD4001的功耗調(diào)節(jié)和吞吐量,(b) 相關(guān)頻率范圍(即低于10 kSPS)放大圖的圖示。

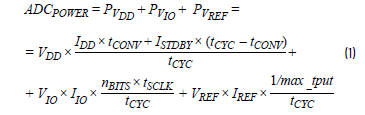

數(shù)字信號(hào)從外部觸發(fā)轉(zhuǎn)換,轉(zhuǎn)換速度受到嚴(yán)格控制。采樣速率越低,導(dǎo)致采樣階段時(shí)間變長(zhǎng),因此平均功耗越低。這一點(diǎn)可參見方程1:

其中:

tCONV為轉(zhuǎn)換時(shí)間

tCYC為采樣速率的倒數(shù)

VDD為模擬電源

VIO為數(shù)字電源

nBITS為ADC的分辨率

tSCLK為串行時(shí)鐘周期時(shí)間(1/fSCLK)

VREF為基準(zhǔn)電壓,IREF為最大吞吐量(max_tput)時(shí)的電流

所以,根據(jù)公式1且如圖4所示,如果tCYC延長(zhǎng)且tCONV保持不變,ADC平均模擬功耗與采樣速率成反比。

圖1所示的ADC在轉(zhuǎn)換階段的功耗主要來自模擬電源,如圖2所示。例如,在應(yīng)變片檢測(cè)電路中,數(shù)據(jù)采集速率可以低至1 kSPS,與按最大采樣速率運(yùn)行AD4001相比,其功耗可以降低20倍。

表2.AD4001功耗調(diào)節(jié)與吞吐量

AD4001 吞吐速率總功耗

1 kSPS300 μW

10 kSPS400 μW

1 MSPS6 mW

公式1(圖示)顯示功率如何隨吞吐量成比例增加,如圖4所示。

降低ADC采樣速率會(huì)導(dǎo)致采集時(shí)間延長(zhǎng),這會(huì)降低ADC驅(qū)動(dòng)器放大器的帶寬要求,從而擴(kuò)大可選設(shè)備的群集。帶寬更低的放大器一般具有相對(duì)更低的靜態(tài)電流。所以,降低ADC采樣速率不僅會(huì)降低ADC功耗,還會(huì)降低配套使用的放大器的功率要求。

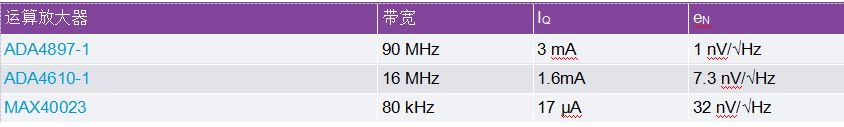

表3.運(yùn)算放大器帶寬與電流消耗和噪聲性能的關(guān)系;帶寬和功率成正比

但是,選擇帶寬更低的運(yùn)算放大器也需要作出取舍。更低的帶寬意味著更低的靜態(tài)電流(IQ),但缺點(diǎn)在于噪聲電壓密度(eN)會(huì)增大,如表3所示。根據(jù)經(jīng)驗(yàn),降低靜態(tài)電流意味著噪聲密度會(huì)按照1/√IQ的比例增大。但是,需要注意的是,調(diào)節(jié)帶寬會(huì)過濾均方根噪聲。換句話說,硬件設(shè)計(jì)人員可能根據(jù)給定的采樣速率、放大器和RC凈帶寬在功耗(或電池壽命)和均方根噪聲性能之間取舍。

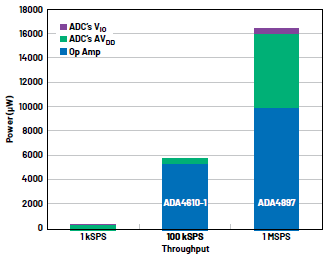

圖5.在多種吞吐量下,每個(gè)電源軌(運(yùn)算放大器、模擬電源軌和數(shù)字電源軌)的電源分布;如表3所示,根據(jù)帶寬需求,使用不同的放大器。

此外,用于設(shè)置運(yùn)算放大器增益的反饋電阻也會(huì)影響功耗:這些電阻越大,它們消耗的功率就越少。但這期間也伴隨著對(duì)噪聲的取舍,因?yàn)殡娮柙酱螅a(chǎn)生的噪聲也越多。正確的設(shè)計(jì)做法是,使電阻盡可能大,只要其噪聲貢獻(xiàn)值在總噪聲中可以忽略不計(jì)。因?yàn)榭傇肼暤扔诟鱾€(gè)噪聲的和方根,所以,根據(jù)一般經(jīng)驗(yàn),可以設(shè)置電阻均方根噪聲的上限為該運(yùn)算放大器的1/3,使其噪聲貢獻(xiàn)值在總噪聲中的占比低于5%。如此,運(yùn)算放大器噪聲仍是主要噪聲。

在有些應(yīng)用中,會(huì)以低吞吐率(幾kSPS)對(duì)低頻率輸入信號(hào)采樣,例如表1所示的信號(hào),在這種情況下,如果無(wú)需信號(hào)調(diào)理(例如增益級(jí)或低輸出阻抗),即可移除驅(qū)動(dòng)器放大器。在更高速度的應(yīng)用中,更新的ADC(例如AD4000或AD4696系列)會(huì)提供高輸入阻抗(高阻)模式,支持使用更低帶寬(和更低功率)放大器來驅(qū)動(dòng)模擬輸入,有時(shí)甚至能完全取消使用驅(qū)動(dòng)器。取消這種運(yùn)算放大器也有助于降低總功耗(其功耗隨之取消),如圖5的藍(lán)色條柱所示。與始終需要使用驅(qū)動(dòng)器放大器的傳統(tǒng)型SAR ADC相比,這有助于大幅節(jié)省功率。在使用AD4696 16通道器件時(shí),這種功率節(jié)省的比例達(dá)到16倍。基準(zhǔn)電壓源高阻模式功能也會(huì)降低基準(zhǔn)電壓源輸入電流,使得總系統(tǒng)功耗隨之降低。

SAR ADC信號(hào)鏈:AFE動(dòng)態(tài)功耗調(diào)節(jié)

如前文所述,SAR ADC功耗會(huì)隨采樣速率變化,但其他信號(hào)鏈元件并不是如此。放大器和基準(zhǔn)電壓在通電之后,消耗恒定的靜態(tài)電流。在采樣ADC樣本期間對(duì)這些元件進(jìn)行功率循環(huán)會(huì)降低信號(hào)鏈的平均功耗。每個(gè)電源周期必須等待信號(hào)確定,這會(huì)限制留給系統(tǒng)開啟和關(guān)閉的時(shí)間。有關(guān)詳情,請(qǐng)參閱“低功耗精密信號(hào)鏈應(yīng)用最重要的時(shí)序因素有哪些?第一部分”和“低功耗精密信號(hào)鏈應(yīng)用最重要的時(shí)序因素有哪些?第二部分”(但建議對(duì)每種具體的信號(hào)鏈設(shè)計(jì)執(zhí)行精準(zhǔn)分析)。

使用高度集成的ADC,在片內(nèi)集成更多模擬前端(AFE)模塊,可以加快上電和斷電轉(zhuǎn)換的速度,但無(wú)損其性能。但是,在許多場(chǎng)景下,為了實(shí)現(xiàn)最佳性能,設(shè)計(jì)最終可能會(huì)使用分立式元件。示例如圖6所示。

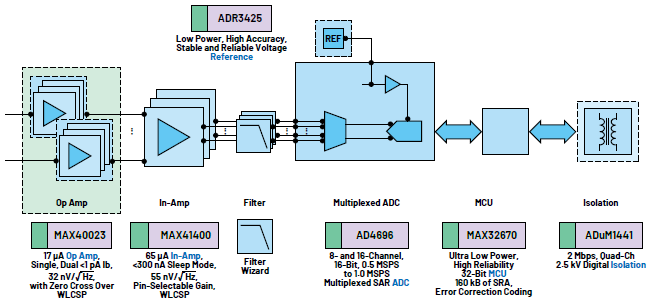

此信號(hào)鏈為多通道,由一個(gè)MAX41400和每通道一個(gè)抗混疊濾波器組成,采用ADR3625精密基準(zhǔn)電壓源,將信息饋送給16通道SAR ADC(即AD4696)。

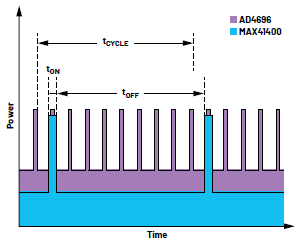

如前文所述,按照可接受的最低吞吐量運(yùn)行ADC會(huì)降低其功耗。此外,如果空閑時(shí)間足夠長(zhǎng),可在部分采樣時(shí)間期間將MAX41400置于關(guān)斷模式,對(duì)于這樣的多路復(fù)用系統(tǒng),可以一次只開啟(上電)一個(gè)放大器。放大器MAX41400開啟(上電)的頻率為tCYC/LSEQ,其中LSEQ為時(shí)序長(zhǎng)度,在圖7所示的示例中,其數(shù)值為10。例如,如果按照每通道1 kSPS的速度進(jìn)行轉(zhuǎn)換,而轉(zhuǎn)換時(shí)間最長(zhǎng)為415 ns,這表示在每個(gè)通道上,MAX41400可在約占循環(huán)時(shí)間10%的時(shí)間里處于關(guān)斷模式。

圖6.多通道測(cè)量信號(hào)鏈。

圖7.基于AD4696 ADC,在多通道多路復(fù)用應(yīng)用中對(duì)MAX41400進(jìn)行功率循環(huán)(為了便于查看,假設(shè)只有10個(gè)通道投入使用)。

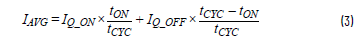

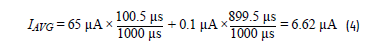

在完全上電時(shí),MAX41400的靜態(tài)電流(IQ_ON)為65 μA,在進(jìn)入關(guān)斷模式(IQ_OFF)之后,該電流可以降低至0.1 μA。在采樣之間將其關(guān)斷,放大器消耗的平均電流(IAVG)會(huì)隨吞吐量改變。

重申一下,吞吐量越低,tCYC越高,IAVG越低。tON表示放大器保持開啟的時(shí)長(zhǎng)。當(dāng)ADC從采集階段切換至轉(zhuǎn)換階段,放大器可以進(jìn)入關(guān)斷狀態(tài),因?yàn)檠娱L(zhǎng)tON時(shí)間,使其超過最短時(shí)間并不會(huì)帶來任何好處。應(yīng)使關(guān)斷時(shí)間(tOFF = tCYC – tON)達(dá)到最長(zhǎng),以最大限度降低功耗,但不到需要犧牲SNR或THD的程度。要找到正確的時(shí)序,具體取決于應(yīng)用、使用的設(shè)備和吞吐率。事實(shí)上,tON和吞吐量可能成反比:吞吐量更低時(shí),導(dǎo)致閑置時(shí)間變長(zhǎng),閑置時(shí)間更長(zhǎng)時(shí),則需要更長(zhǎng)的tON時(shí)間來喚醒放大器。根據(jù)數(shù)據(jù)手冊(cè),AD4696的典型轉(zhuǎn)換時(shí)間為415 ns。這個(gè)轉(zhuǎn)換時(shí)間,加上在關(guān)斷之后重新給MAX41400上電所需的100 μs,即為最短的tON時(shí)間。所以,平均電流消耗為:

與始終使能的放大器相比,MAX41400在關(guān)斷模式下的功耗和快速上電期間的功耗總和要低10倍。

一般來說,除了所示示例在給定吞吐率下計(jì)算得出的節(jié)省功率外,所有這些公式都可以如圖9所示,以圖形的方式展示,其規(guī)格則依照數(shù)據(jù)手冊(cè)(假設(shè)已使能基準(zhǔn)電壓源和模擬輸入高阻模式)。

圖8.信號(hào)鏈功耗與吞吐量的關(guān)系(前端提供和不提供功耗調(diào)節(jié)功能)。

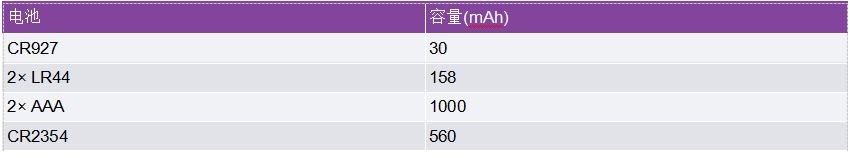

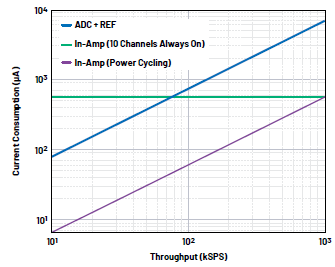

可以采用相同的分析方法來分析電池壽命,與功耗分析相反,需要使用電池容量除以平均電流。

表4.電池容量

在這種情況下,兩者成反比,也就是說,吞吐量越低,電池壽命越長(zhǎng)。

圖9.利用功率循環(huán)/調(diào)節(jié)功能延長(zhǎng)電池壽命。

任何放大器,即使不像MAX41400一樣支持關(guān)斷模式,都可以如之前所示進(jìn)行功率循環(huán)。也就是說,不是進(jìn)入關(guān)斷模式,而是徹底上電和徹底關(guān)閉。但是,在操作時(shí)必須小心。一方面,放大器的喚醒時(shí)間將會(huì)更長(zhǎng),所以最短tON時(shí)間也會(huì)更長(zhǎng)。另一方面,重復(fù)對(duì)解耦電容充電和放電會(huì)影響在每個(gè)電源周期給它們充電的電流,與關(guān)斷模式相比,會(huì)增大整體的功耗。此外,如果傳感器在電源軌未上電的情況下仍然驅(qū)動(dòng)放大器輸入,在沒有保護(hù)措施的情況下,可能會(huì)導(dǎo)致?lián)p壞。

基于SAR ADC的信號(hào)鏈:數(shù)字電源功耗調(diào)節(jié)

前文著重介紹降低模擬電源功耗(如果是總功耗的最主要來源時(shí))該如何降低。降低吞吐量也會(huì)影響數(shù)字功耗,因?yàn)檫@使得串行時(shí)鐘能以更低頻率運(yùn)行:

公式5指出,我們還可以采用兩個(gè)額外的步驟來最大限度降低數(shù)字功耗:

使用更低的數(shù)字電源電壓(VIO)

最大限度降低串行數(shù)據(jù)輸出線路的走線電容

需要注意的另一點(diǎn)是數(shù)字通信線路中使用的上拉/下拉電阻的值。這些電阻用于確保在數(shù)字輸入/輸出端提供正確的邏輯電平,它們的數(shù)值會(huì)影響到系統(tǒng)的總功耗。使用的電阻值過低(也稱為強(qiáng)上拉)可能會(huì)導(dǎo)致線路中有大電流通過。因此,應(yīng)避免使用非必要的低電阻值。另一方面,如果電阻過高,泄漏電流導(dǎo)致的壓降會(huì)導(dǎo)致錯(cuò)誤的邏輯電平解譯。此外,壓降會(huì)影響傳輸。所以,設(shè)計(jì)人員必須在無(wú)損電壓電平(取決于數(shù)字電源電壓和泄漏電流)或信號(hào)完整性的情況下,使用最高的電阻值。

基于Σ-Δ ADC的信號(hào)鏈

在基于Σ-Δ ADC的信號(hào)鏈中,之前所述的功耗調(diào)節(jié)概念并不直接適用。這是因?yàn)檗D(zhuǎn)換不是從外部觸發(fā)的,而是由自由運(yùn)行的時(shí)鐘觸發(fā)的4。所以它們不能作為外部轉(zhuǎn)換開始信號(hào)的函數(shù),以閑置狀態(tài)持續(xù)一定時(shí)間。

但是,許多Σ-Δ ADC支持待機(jī)模式,如果ADC無(wú)需持續(xù)轉(zhuǎn)換,即可使用這種模式。如前文所述,我們還需要考慮時(shí)序問題5,因?yàn)樵趩拘哑骷狡骷顺龃龣C(jī)模式的這段時(shí)間里,是不能進(jìn)行采樣的。

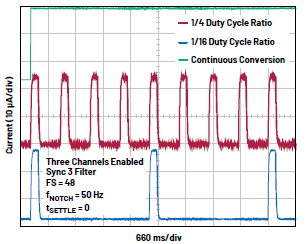

除了待機(jī)模式外,高度集成的Σ-Δ ADC(例如AD4130)還提供占空比模式。如此,ADC會(huì)自動(dòng)上電和關(guān)閉,無(wú)需在每次循環(huán)時(shí)與主機(jī)交互。AD4130提供兩種模式,分別為1/4和1/16,這表示該器件在1/4和1/16的時(shí)間里保持激活。與連續(xù)轉(zhuǎn)換模式相比,這會(huì)大幅節(jié)省功率,如圖10所示。

表5.AD4130在每種功率模式下的電流消耗

AD4130功率模式典型功耗

連續(xù)轉(zhuǎn)換32 μA

占空比控制5 μA

關(guān)斷模式0.5 μA

根據(jù)所需的吞吐率,在選擇優(yōu)化功耗的技術(shù)時(shí),可以使用其中一種占空比模式,或者讓器件在一定時(shí)間里處于待機(jī)模式。實(shí)際上,AD4130的多種工作模式都可能影響ADC的功耗。ACE6中可用的主動(dòng)功能模型顯示了所選ADC配置的功耗和預(yù)期的電池壽命。

圖10.Ad4130在不同工作模式下的電流消耗:連續(xù)轉(zhuǎn)換模式、1/4占空比和1/16占空比。

基于Σ-Δ ADC的信號(hào)鏈:AFE動(dòng)態(tài)功耗調(diào)節(jié),支持占空比

和基于SAR ADC的信號(hào)鏈一樣,基于∑-? DAC的信號(hào)鏈可以利用占空比,在ADC處于低功耗狀態(tài)(圖10)時(shí)將某些模塊置于關(guān)斷狀態(tài)。如此,可以實(shí)現(xiàn)與圖9所示類似的AFE功率節(jié)省。

傳感器激勵(lì)

完整的解決方案器件(例如AD4130)不止提供核心轉(zhuǎn)換器,還提供內(nèi)部可編程增益放大器,以及傳感器偏置和激勵(lì)(可選的電流源和精密基準(zhǔn)電壓)。這種集成意味著易用性、尺寸,以及在不同構(gòu)建模塊之間使用偏置、時(shí)序或功率循環(huán)等的優(yōu)化。所以,AD4130本身通過在片內(nèi)集成這些模塊來降低系統(tǒng)的整體功耗。此外,它能夠靈活用在多種不同的平臺(tái)中,例如RTD、熱敏電阻或橋接傳感器等等,能夠幫助簡(jiǎn)化設(shè)計(jì)周期。它還減少了BOM數(shù)量,以及需要使用的電源軌的數(shù)量。

其他功率優(yōu)化技術(shù)

本文介紹了多種最大限度降低信號(hào)鏈功耗的方法。但是,信號(hào)鏈還有一個(gè)部分需要考慮,即主機(jī)控制器。如果控制器因?yàn)樾枰x取和后處理來自ADC的數(shù)據(jù)而始終保持上電,那么它會(huì)消耗很多功率。在控制器未使用時(shí),將其置于睡眠模式將有助于額外節(jié)省功率。

帶片內(nèi)FIFO的ADC

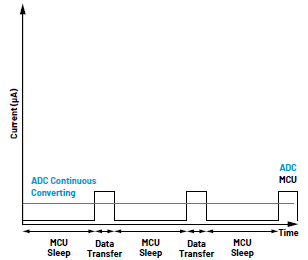

如果應(yīng)用無(wú)需實(shí)時(shí)數(shù)據(jù),但必須以更低的速率讀取數(shù)據(jù)點(diǎn),那么帶片內(nèi)FIFO的ADC應(yīng)能派上用場(chǎng)。AD4130集成了這種模塊,該FIFO能夠存儲(chǔ)多達(dá)256次轉(zhuǎn)換,所以,如果輸出數(shù)據(jù)速率(ODR)(例如)為2.4 kSPS,該微控制器無(wú)需每隔416 μs讀取一次,而是可以進(jìn)入睡眠模式,每隔100 ms喚醒,一次性讀取整個(gè)存儲(chǔ)器的數(shù)據(jù)(參見圖11的數(shù)據(jù)傳輸部分)。換言之,如果ADC的存儲(chǔ)器能存儲(chǔ)最新的256個(gè)樣本,也能使微控制器進(jìn)行功率循環(huán),從而大幅降低系統(tǒng)的總功耗。

圖11.利用ADC的片內(nèi)FIFO降低微控制器的功耗。

通過直接存儲(chǔ)訪問(DMA)將ADC數(shù)據(jù)流傳輸至存儲(chǔ)器

對(duì)于不包含片內(nèi)FIFO的ADC,可以轉(zhuǎn)而使用大部分微控制器都包含的直接存儲(chǔ)訪問(DMA)。DMA能將數(shù)據(jù)直接從外設(shè)(在本例中為SPI)傳輸至存儲(chǔ)器(SRAM),不存在因?yàn)槊看谓邮誂DC樣本而造成CPU干預(yù)或中斷。選擇的微控制器會(huì)直接影響到可以實(shí)現(xiàn)的功率節(jié)省。在許多情況下,微控制器在大部分時(shí)間里都能保持處于睡眠模式,只有在接收到ADC樣本時(shí)才觸發(fā)事件。此事件會(huì)簡(jiǎn)單提醒DMA開始執(zhí)行SPI事務(wù),之后再回到睡眠狀態(tài),相比CPU在整個(gè)SPI事務(wù)執(zhí)行期間保持完全喚醒,這會(huì)使微控制器的功耗達(dá)到最低。注意,只有在ADC數(shù)據(jù)的格式與目標(biāo)存儲(chǔ)器一致時(shí),才能使用DMA。也就是說,對(duì)于大部分微控制器,只有當(dāng)ADC數(shù)據(jù)為16位或32位時(shí),才能輕松使用DMA。

中斷驅(qū)動(dòng)編程

許多低功耗應(yīng)用不要求記錄和處理每個(gè)數(shù)據(jù)點(diǎn),但需要監(jiān)控檢測(cè)的幅度是否位于特定的閾值之內(nèi)。以前,為了進(jìn)行監(jiān)測(cè),主機(jī)控制器需要始終保持喚醒,以讀取每個(gè)ADC樣本,確定其值是否正常,并且據(jù)此觸發(fā)中斷例程。

AD4696 (SAR ADC)和AD4130 (Σ-Δ ADC)都集成了這些閾值檢測(cè)功能。閾值可以編入程序,使得GPIO引腳只在ADC輸出代碼超出用戶定義的范圍時(shí)進(jìn)行認(rèn)定。如此,主機(jī)控制器大部分時(shí)間都可以處于睡眠模式,只在GPIO認(rèn)定時(shí)喚醒,這意味著,它只在需要執(zhí)行操作時(shí)才保持活躍,因此能夠最大限度降低功耗。

結(jié)論

在為便攜式現(xiàn)場(chǎng)儀器儀表、狀態(tài)監(jiān)控或生命體征測(cè)量(VSM)等應(yīng)用設(shè)計(jì)電池供電的測(cè)量系統(tǒng)時(shí),可以使用analog.com/precisionlowpower所示的低功耗信號(hào)鏈來實(shí)現(xiàn)功率優(yōu)化型解決方案。ADI的精密低功耗信號(hào)鏈幫助設(shè)計(jì)人員簡(jiǎn)化了構(gòu)建低功耗測(cè)量解決方案的過程,該解決方案將精密放大器、基準(zhǔn)電壓、ADC和隔離產(chǎn)品優(yōu)化組合在一起。在這些信號(hào)鏈中,功耗得到優(yōu)化,同時(shí)兼顧噪聲性能、尺寸、易用性這些重要指標(biāo)。這些信號(hào)鏈提供不同配置:?jiǎn)瓮ǖ馈⒎至⑹蕉嗤ǖ溃ǘ嗦窂?fù)用)、完全集成的多通道解決方案和隨時(shí)可用的功率優(yōu)化設(shè)計(jì),對(duì)于低功耗設(shè)計(jì)來說是非常不錯(cuò)的起點(diǎn)。

除了展示ADI的精密低功耗信號(hào)鏈之外,本文還展示多種提高信號(hào)鏈的能效比的系統(tǒng)級(jí)技術(shù)。這些技術(shù)包括功耗調(diào)節(jié)、功率循環(huán)、占空比,或使用FIFO這類片內(nèi)功能,或者閾值檢測(cè)這類中斷驅(qū)動(dòng)功能。

參考

1 Padraic O'Reilly。低功耗精密信號(hào)鏈應(yīng)用最重要的時(shí)序因素有哪些?第一部分“。模擬對(duì)話,第56卷第3期,2022年8月。

2 Padraic O'Reilly。低功耗精密信號(hào)鏈應(yīng)用最重要的時(shí)序因素有哪些?第二部分”。模擬對(duì)話,第56卷第3期,2022年8月。

3 數(shù)據(jù)轉(zhuǎn)換手冊(cè)。(ADI公司,2005年)

4 Michael Clifford。“Σ-Δ型ADC拓?fù)浣Y(jié)構(gòu)基本原理:

第一部分”。ADI公司,2016年1月。

5 Bruce Pepitas。“動(dòng)態(tài)功耗調(diào)節(jié)簡(jiǎn)介”。ADI公司,2016年1月。

6 分析 | 控制 | 評(píng)估(ACE)軟件。ADI公司

Brandon Hurst。“如何使用DMA在低功耗可穿戴設(shè)備中加快外設(shè)監(jiān)測(cè)”。模擬對(duì)話,第56卷第1期,2022年1月。

Maithil Pachchigar和Alan Walsh。“新一代SAR ADC解決精密數(shù)據(jù)采集信號(hào)鏈設(shè)計(jì)的難點(diǎn)”。模擬對(duì)話,第50卷第4期,2016年12月。

Sanjay Rajasekhar和Arvind Shankar。“如何利用輸入高阻技術(shù)來降低解決方案的功耗并減小尺寸”。ADI公司,2022年7月。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<