學(xué)子專區(qū)—ADALM2000實(shí)驗(yàn):鎖相環(huán)

2023-04-23

作者:Antoniu Miclaus,系統(tǒng)應(yīng)用工程師和Doug Mercer,顧問研究員

來源:ADI

目標(biāo)

本實(shí)驗(yàn)活動介紹鎖相環(huán)(PLL)。PLL電路有一些重要的應(yīng)用,例如信號調(diào)制/解調(diào)(主要是頻率和相位調(diào)制)、同步、時(shí)鐘和數(shù)據(jù)恢復(fù),以及倍頻和頻率合成。在這項(xiàng)實(shí)驗(yàn)中,您將建立一個(gè)簡單的PLL電路,讓您對PLL操作有基本的了解。

背景知識

PLL是一種反饋系統(tǒng),用于調(diào)節(jié)或鎖定壓控振蕩器(VCO)輸出與輸入基準(zhǔn)信號之間的相位差,如圖1所示。VCO是一種振蕩器,其輸出頻率是某個(gè)輸入控制電壓的函數(shù)。通常,當(dāng)VCO用于PLL等反饋環(huán)路時(shí),電壓頻率轉(zhuǎn)換函數(shù)必須至少是單調(diào)的。VCO的一個(gè)特例是電壓頻率轉(zhuǎn)換器(VFC),其電壓/頻率特性是線性的。反饋環(huán)路中的分頻器的分頻系數(shù)N一般是整數(shù),包括1,若為1則與沒有分頻器或從VCO輸出直連鑒相器輸入的情況相同。

圖1.PLL基本框圖

PLL是許多深?yuàn)W書籍和討論的主題,非常復(fù)雜,無法在這幾頁中詳盡說明。本實(shí)驗(yàn)的末尾有額外閱讀材料的鏈接。

材料

▲ADALM2000主動學(xué)習(xí)模塊

▲無焊試驗(yàn)板

▲跳線

▲一個(gè)2.2 kΩ電阻

▲一個(gè)47 kΩ電阻

▲一個(gè)10 kΩ電阻

▲一個(gè)4.7 nF電容(標(biāo)記為472)

▲一個(gè)100 pF電容(標(biāo)記為101)

▲一個(gè)CD4007 CMOS陣列

▲2個(gè)ZVN2110A NMOS晶體管

▲2個(gè)ZVP2110A PMOS晶體管

▲一個(gè)AD654 VFC

▲一節(jié)9 V電池(帶連接器)

第1步指導(dǎo)

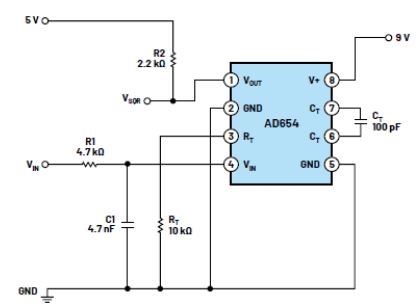

在無焊試驗(yàn)板上,首先基于AD654搭建VFC電路,如圖2所示。將電路搭建到試驗(yàn)板的一側(cè),以便為PLL的其他部件留出空間,我們將在本實(shí)驗(yàn)活動的后續(xù)步驟中添加這些部件。控制電壓通過由R1和C1組成的單極點(diǎn)低通濾波器施加。這相當(dāng)于圖1中饋送至VCO模塊的低通濾波器模塊。

圖2.VFC電路

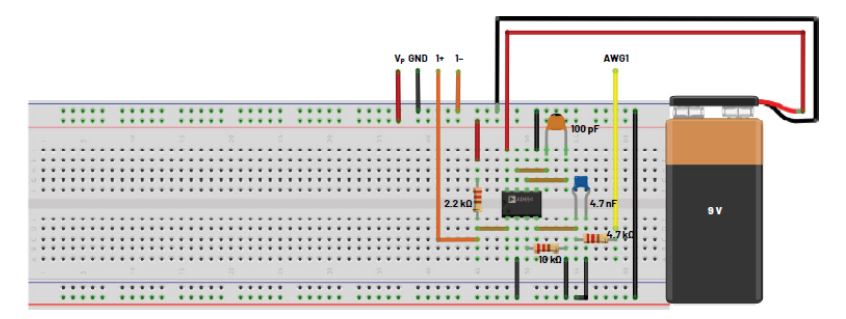

硬件設(shè)置

開啟固定5 V電源,并將9 V電池連接到電路。將AWG1輸出連接到VIN,如圖2所示。將AWG1配置為DC源,初始設(shè)置為2.5 V。將示波器通道輸入CH1+連接到VSQR輸出,如圖2所示。還應(yīng)將CH1-輸入接地。

圖3.VFC試驗(yàn)板電路

程序步驟

使用AWG 1直流偏置控制,將VIN電壓從1 V調(diào)整到4 V,同時(shí)在VSQR觀察VFC輸出的頻率。使用示波器控制屏幕上的頻率測量功能來完成此操作。根據(jù)公式1,圖2中的Rt和Ct設(shè)置VFC的標(biāo)稱輸出頻率。

例如,VIN為設(shè)置范圍的中間值2.5V,并給定Rt Ct值(2.5/(10 × 10 kΩ × 100 pF)),輸出頻率應(yīng)接近250 kHz。驗(yàn)證您的測量結(jié)果是否與該值一致。如果不一致,請重新檢查電路連接和元件值。

圖4.VFC輸出

第2步指導(dǎo)

接下來,在試驗(yàn)板上添加來自上一個(gè)實(shí)驗(yàn)的異或門鑒相器電路,如圖5所示。構(gòu)建異或門后,將其連接到V轉(zhuǎn)F電路,如圖6所示,以構(gòu)成完整的PLL。在給電路添加任何東西之前,務(wù)必關(guān)閉5 V電源并斷開9 V電池。

圖5.添加XOR鑒相器

圖6.完整PLL電路

硬件設(shè)置

開啟固定5 V電源,并將9 V電池連接到電路。將AWG1輸出連接到FREF,如圖4所示。將AWG1配置為方波,其幅度為5 V峰峰值,偏置為2.5 V(0 V至5 V擺幅);將初始頻率設(shè)置為第1步中測得的值(即VIN設(shè)置為2.5 V時(shí),應(yīng)在250 kHz左右)。將示波器通道輸入CH1+連接到FREF輸入,并將示波器通道CH2+連接到VSQR輸出,如圖6所示。還應(yīng)該將CH1-和CH2-輸入接地。將示波器設(shè)置為在通道1(FREF信號)的上升沿觸發(fā)。

圖7.完整的PLL試驗(yàn)板電路

程序步驟

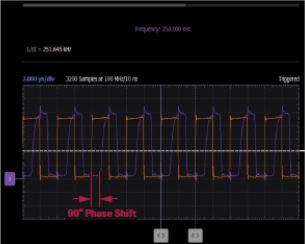

在FREF的頻率設(shè)為對應(yīng)于AD654引腳4上2.5 V控制電壓的情況下,VSQR處看到的輸出頻率應(yīng)鎖定輸入基準(zhǔn)頻率FREF。在示波器屏幕上,您應(yīng)該看到兩個(gè)方波是穩(wěn)定的(即彼此鎖定),并且VSQR相對于FREF偏移約90°。請記住,當(dāng)XOR鑒相器的兩個(gè)輸入相差90°時(shí),其濾波輸出將處于其輸出范圍的一半或約2.5 V。

圖8.完整的PLL FREF和VSQR曲線

以小增量增大和減小基準(zhǔn)頻率FREF,以確定PLL會鎖定的最小和最大頻率。當(dāng)更改基準(zhǔn)輸入的頻率時(shí),注意FREF和VSQR之間的相對相位差。執(zhí)行此操作時(shí),測量AD654引腳4上的濾波直流控制電壓,并將這些讀數(shù)與步驟1中掃描VFC直流控制電壓時(shí)測得的讀數(shù)進(jìn)行比較。

將示波器通道2連接到圖6中C點(diǎn)處異或門的輸出端。將所看到的方波與異或門A (VSQR)和門B (FREF)的輸入進(jìn)行比較。當(dāng)PLL鎖定在最小和最大鎖定頻率以及鎖定范圍的中心頻率時(shí),C處的波形如何變化?

附加第3步指導(dǎo)

圖6中的簡單PLL電路不是十分有意義,因?yàn)檩敵鲂盘栔皇禽斎胄盘柕南嘁瓢姹尽H鐖D1所示,如果在從VFC輸出端到鑒相器輸入端的反饋路徑中插入一個(gè)數(shù)字分頻器模塊,則輸出信號將是一個(gè)更高的倍頻信號。使用任何可用的數(shù)字分頻器IC,如CD4020、CD4040、CD4060甚至SN7490(幾乎任何分頻器IC都可以),斷開與異或輸入A的連接,并插入分頻器模塊,如圖9所示。

圖9.PLL倍頻器

根據(jù)您構(gòu)建的分頻器的分頻系數(shù)N,您需要相應(yīng)地改變FREF輸入頻率。例如,當(dāng)N=8時(shí),如果FREF之前是250 kHz,新的FREF將是250/8或31.25 kHz。異或門鑒相器輸出端的脈沖頻率也將是原來的八分之一。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<