Imec 是世界上最先進(jìn)的半導(dǎo)體研究公司,最近在比利時安特衛(wèi)普舉行的 ITF 世界活動上分享了其亞 1 納米硅和晶體管路線圖。該路線圖讓我們了解了到 2036 年公司將在其實(shí)驗(yàn)室與臺積電、英特爾、Nvidia、AMD、三星和 ASML 等行業(yè)巨頭合作研發(fā)下一個主要工藝節(jié)點(diǎn)和晶體管架構(gòu)的時間表,在許多其他人中。該公司還概述了向其所謂的 CMOS 2.0 的轉(zhuǎn)變,這將涉及將芯片的功能單元(如 L1 和 L2 緩存)分解為比當(dāng)今基于小芯片的方法更先進(jìn)的 3D 設(shè)計(jì)。

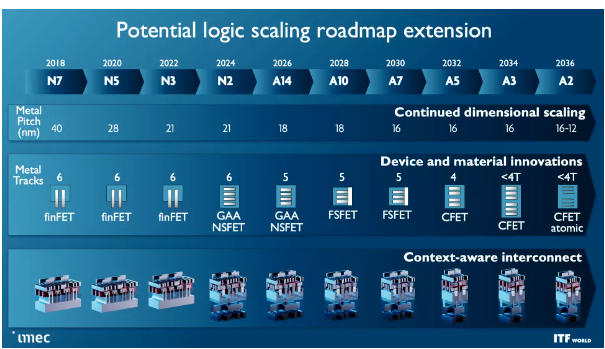

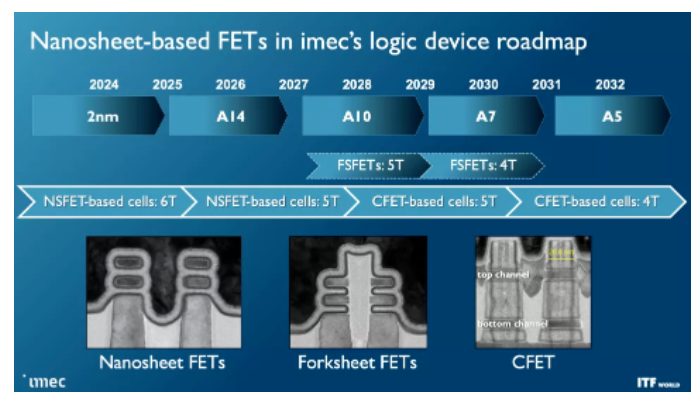

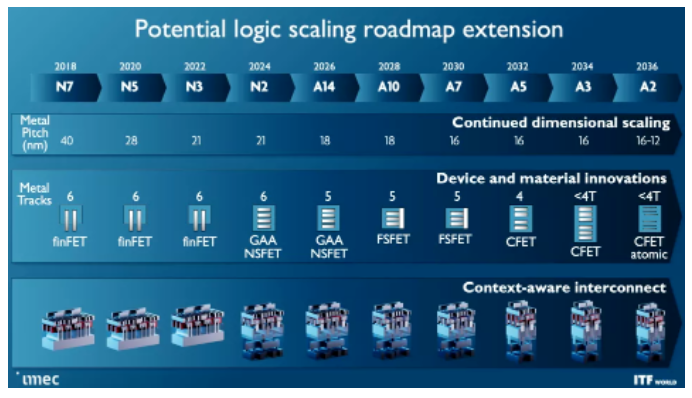

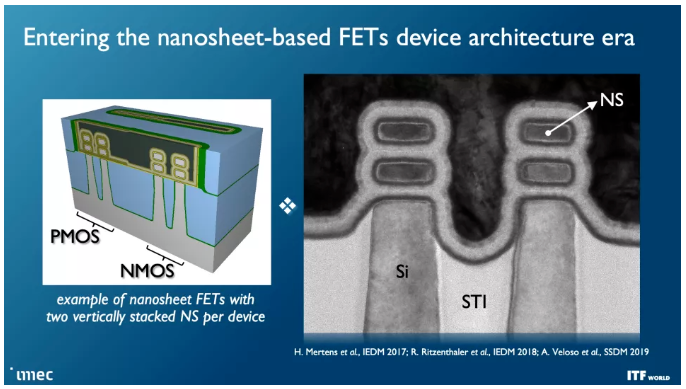

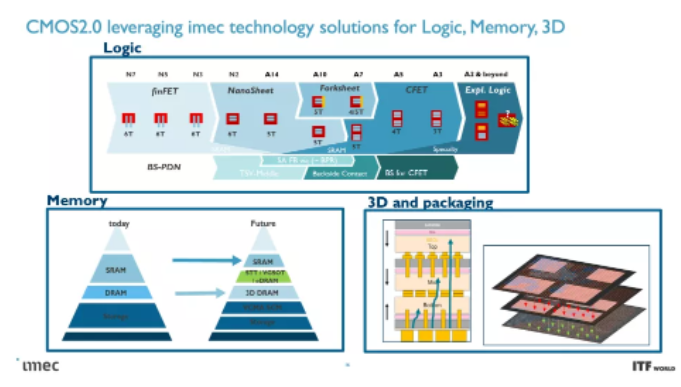

提醒一下,10 埃等于 1 納米,因此 Imec 的路線圖包含亞“1 納米”工藝節(jié)點(diǎn)。該路線圖概述了標(biāo)準(zhǔn) FinFET 晶體管將持續(xù)到 3nm,然后過渡到新的全柵 (GAA) 納米片設(shè)計(jì),該設(shè)計(jì)將在 2024 年進(jìn)入大批量生產(chǎn)。Imec 繪制了 2nm 和 A7(0.7nm)Forksheet設(shè)計(jì)的路線圖,隨后分別是 A5 和 A2 的 CFET 和原子通道等突破性設(shè)計(jì)。

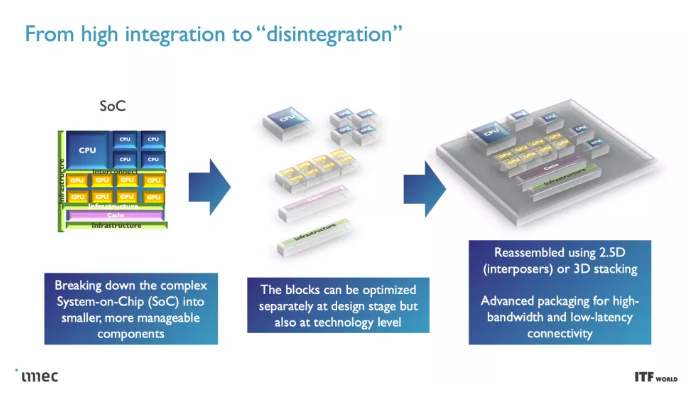

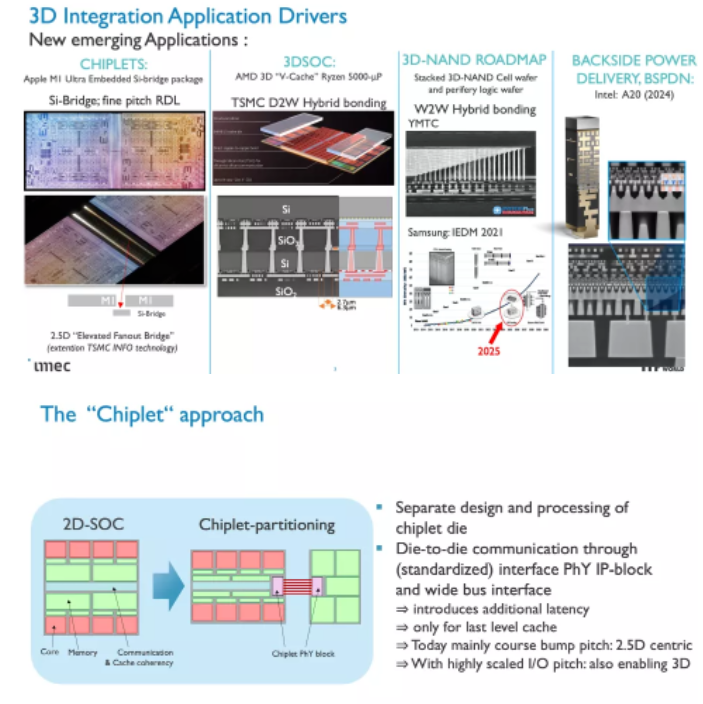

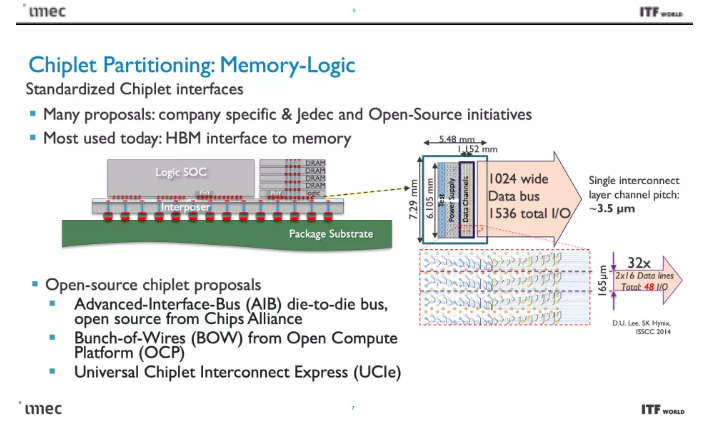

隨著時間的推移,轉(zhuǎn)移到這些較小的節(jié)點(diǎn)變得越來越昂貴,并且使用單個大芯片構(gòu)建單片芯片的標(biāo)準(zhǔn)方法已經(jīng)讓位于小芯片。基于小芯片的設(shè)計(jì)將各種芯片功能分解為連接在一起的不同芯片,從而使芯片能夠作為一個內(nèi)聚單元發(fā)揮作用——盡管需要權(quán)衡取舍。

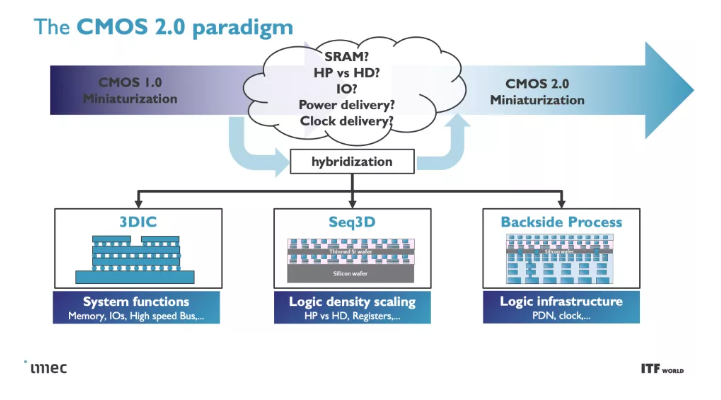

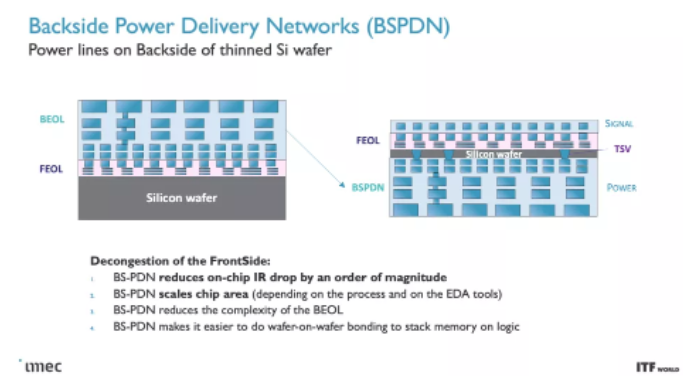

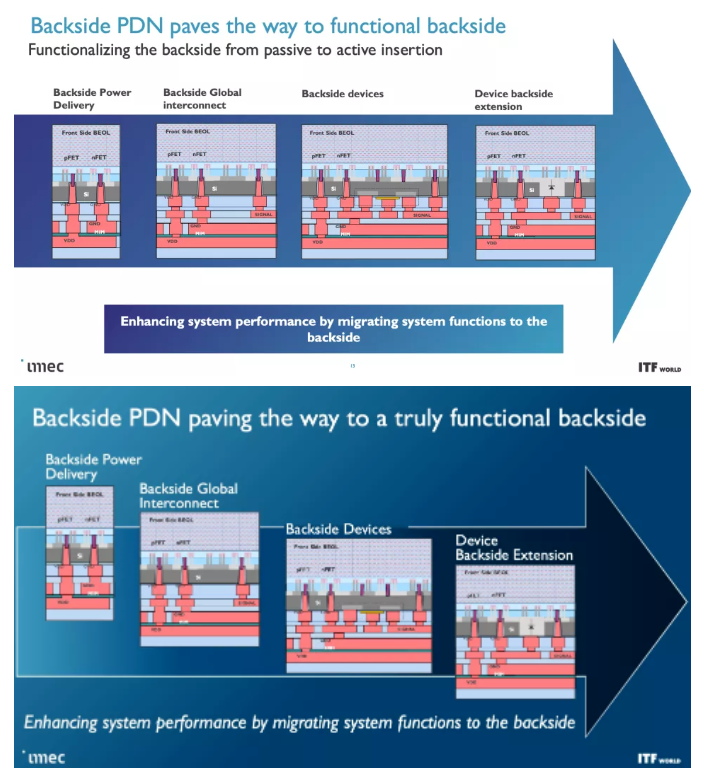

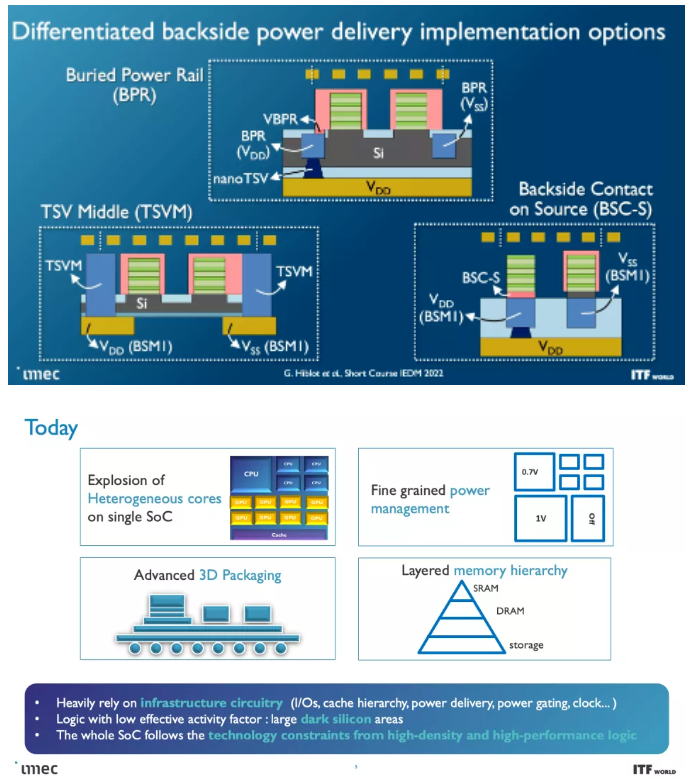

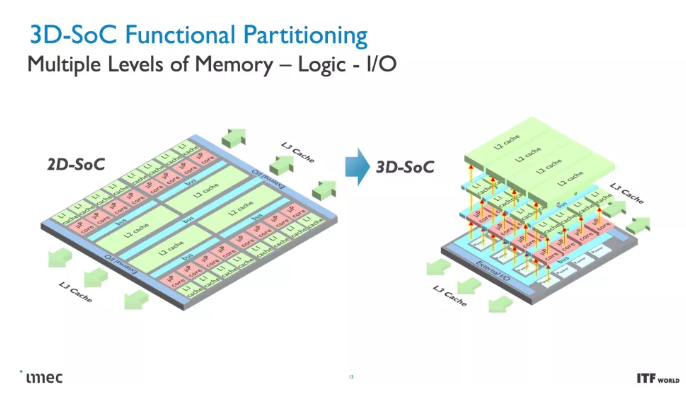

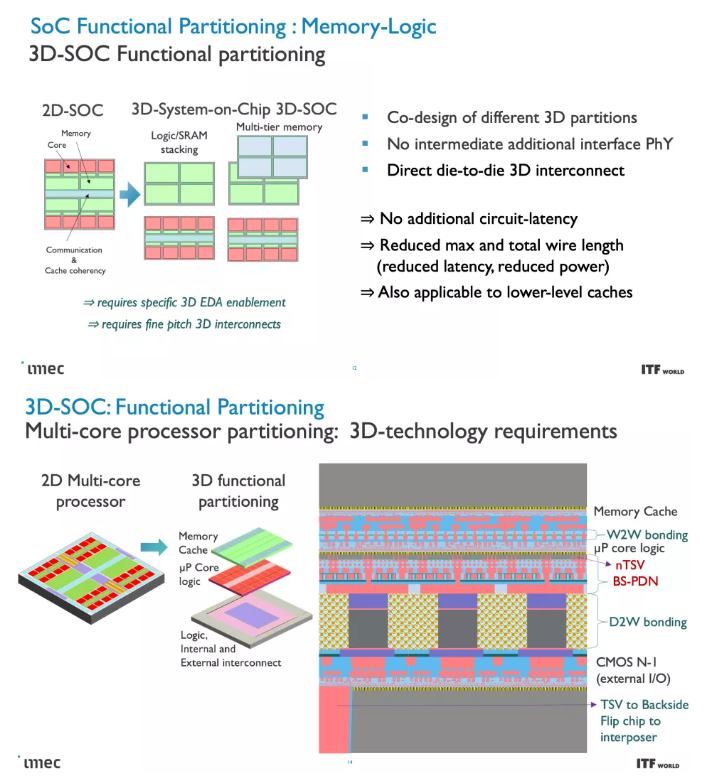

Imec 對 CMOS 2.0 范式的設(shè)想包括將芯片分解成更小的部分,將緩存和存儲器分成具有不同晶體管的自己的單元,然后以 3D 排列堆疊在其他芯片功能之上。這種方法還將嚴(yán)重依賴背面供電網(wǎng)絡(luò) (BPDN),該網(wǎng)絡(luò)通過晶體管的背面路由所有電力。

讓我們仔細(xì)看看 imec 路線圖和新的 CMOS 2.0 方法。

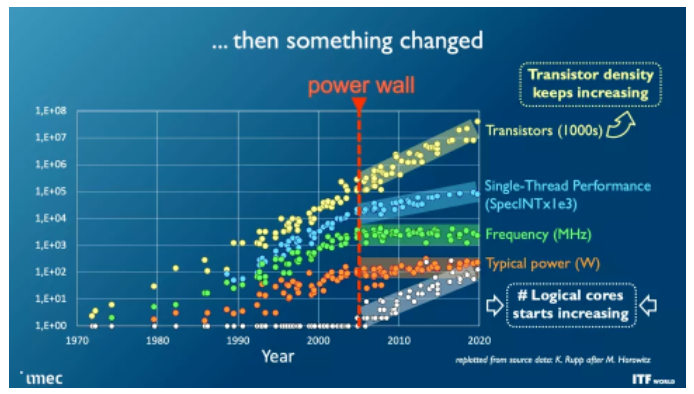

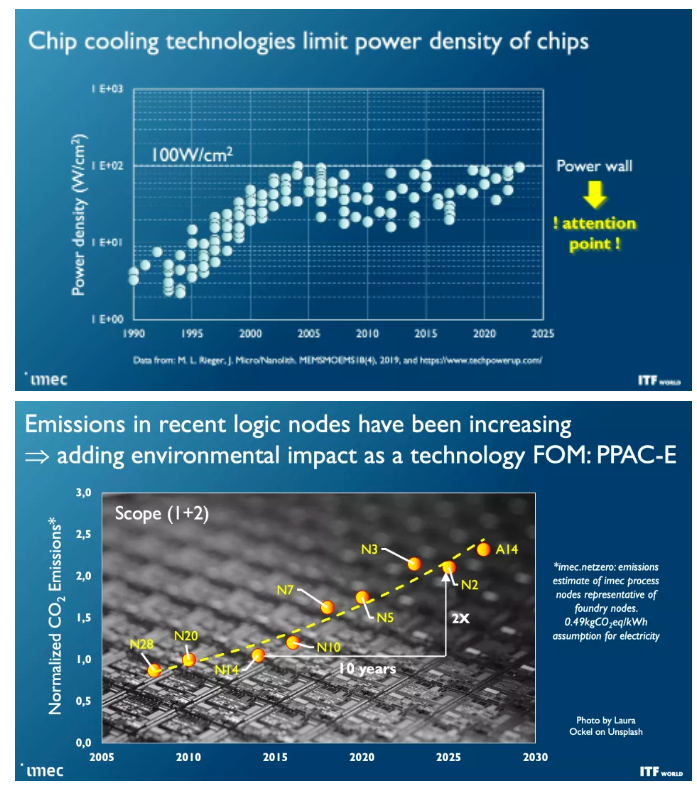

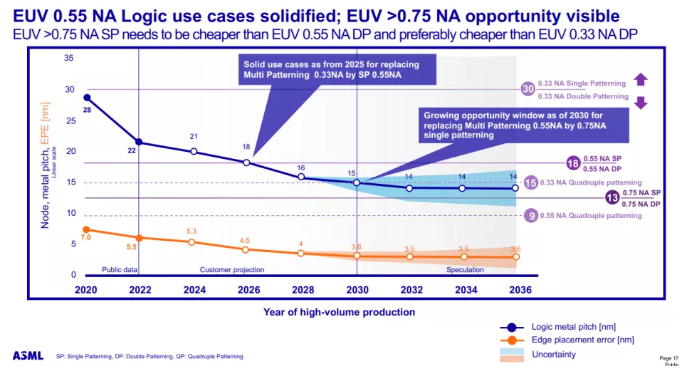

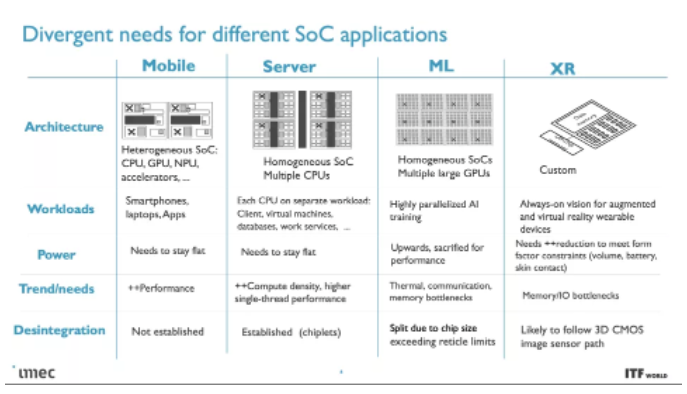

正如您在上面的相冊中看到的那樣,隨著節(jié)點(diǎn)的進(jìn)步,該行業(yè)面臨著看似無法克服的挑戰(zhàn),但對更多計(jì)算能力的需求,尤其是對機(jī)器學(xué)習(xí)和人工智能的需求呈指數(shù)級增長。這種需求并不容易滿足。成本飆升,而高端芯片的功耗穩(wěn)步增加——功率縮放仍然是一個挑戰(zhàn),因?yàn)?CMOS 工作電壓頑固地拒絕低于 0.7 伏,并且持續(xù)需要擴(kuò)展到更大的芯片帶來了電源和冷卻挑戰(zhàn),這將需要全新的規(guī)避解決方案。

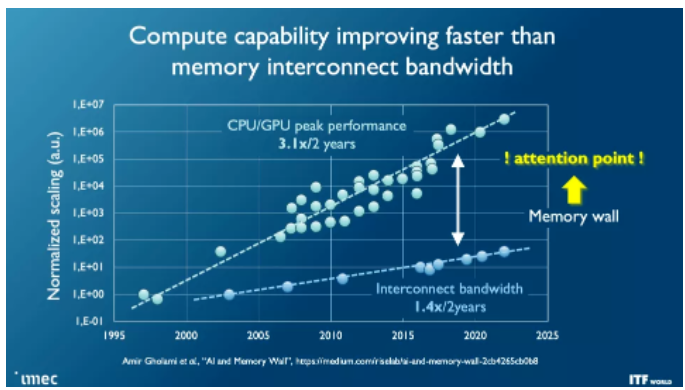

雖然晶體管數(shù)量在可預(yù)測的摩爾定律路徑上繼續(xù)翻倍,但其他基本問題也越來越成為每一代新一代芯片的問題,例如互連帶寬的限制嚴(yán)重落后于現(xiàn)代 CPU 和 GPU 的計(jì)算能力,從而阻礙了性能并限制這些額外晶體管的有效性。

imec 晶體管和工藝節(jié)點(diǎn)路線圖

不過,速度更快、密度更大的晶體管是首要任務(wù),而這些晶體管的第一波浪潮將伴隨著 2024 年以 2nm 節(jié)點(diǎn)首次亮相的 Gate All Around (GAA)/Nanosheet 器件,取代為當(dāng)今領(lǐng)先技術(shù)提供動力的三柵極 FinFET 。GAA 晶體管賦予晶體管密度和性能改進(jìn),例如更快的晶體管開關(guān),同時使用與多個鰭片相同的驅(qū)動電流。泄漏也顯著減少,因?yàn)闇系劳耆粬艠O包圍,調(diào)整溝道的厚度可以優(yōu)化功耗或性能。

我們已經(jīng)看到多家芯片制造商采用了這種晶體管技術(shù)的不同變體。行業(yè)領(lǐng)導(dǎo)者臺積電計(jì)劃其帶有 GAA 的 N2 節(jié)點(diǎn)將于 2025 年量產(chǎn),因此它將是最后采用新型晶體管的。英特爾采用“intel 20A”工藝節(jié)點(diǎn)的四層 RibbonFET具有四個堆疊的納米片,每個納米片完全由一個門包圍,并將于 2024 年首次亮相。三星是第一家生產(chǎn)用于運(yùn)輸產(chǎn)品的 GAA,但小批量 SF3E pipe-cleane的節(jié)點(diǎn)不會看到大規(guī)模生產(chǎn)。相反,該公司將在 2024 年推出其用于大批量制造的先進(jìn)節(jié)點(diǎn)。

提醒一下,10 埃 (A) 等于 1 納米。這意味著 A14 是 1.4 納米,A10 是 1 納米,我們將在 2030 年的時間框架內(nèi)與 A7 一起進(jìn)入亞 1 納米時代。但請記住,這些指標(biāo)通常與芯片上的實(shí)際物理尺寸不匹配。

Imec 預(yù)計(jì) forksheet 晶體管從 1nm (A10) 開始,一直到 A7 節(jié)點(diǎn) (0.7nm)。正如您在第二張幻燈片中看到的那樣,該設(shè)計(jì)分別堆疊 NMOS 和 PMOS,但使用電介質(zhì)勢壘將它們分開,從而實(shí)現(xiàn)更高的性能和/或更好的密度。

互補(bǔ) FET (CFET:Complementary FET) 晶體管在 2028 年首次以 1nm 節(jié)點(diǎn) (A10) 出現(xiàn)時將進(jìn)一步縮小占位面積,從而允許更密集的標(biāo)準(zhǔn)單元庫。最終,我們將看到帶有原子通道的 CFET 版本,進(jìn)一步提高性能和可擴(kuò)展性。CFET 晶體管(您可以 在此處閱讀更多相關(guān)信息)將 N 型和 PMOS 器件堆疊在一起以實(shí)現(xiàn)更高的密度。CFET 應(yīng)該標(biāo)志著納米片器件縮放的結(jié)束,以及可見路線圖的結(jié)束。

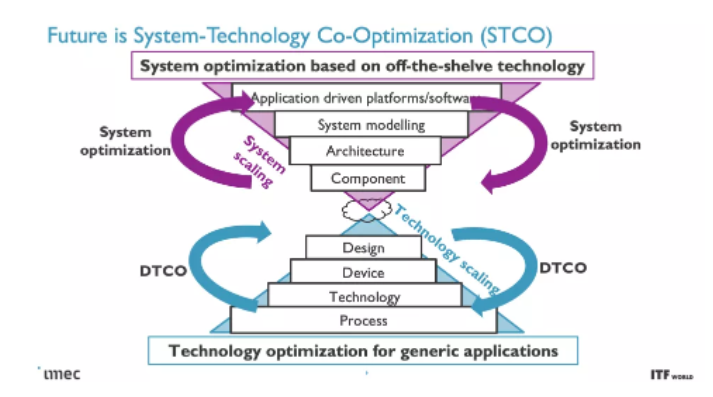

然而,將需要其他重要技術(shù)來打破性能、功率和密度縮放障礙,imec 設(shè)想這將需要新的 CMOS 2.0 范例和系統(tǒng)技術(shù)協(xié)同優(yōu)化 (SCTO)。

STCO 和背面供電

在最高級別,系統(tǒng)技術(shù)協(xié)同優(yōu)化 (STCO:system technology co-optimization) 需要通過對系統(tǒng)和目標(biāo)應(yīng)用程序的需求建模來重新思考設(shè)計(jì)過程,然后使用這些知識來為創(chuàng)建芯片的設(shè)計(jì)決策提供信息。這種設(shè)計(jì)方法通常會導(dǎo)致“分解”通常作為單片處理器的一部分的功能單元,例如供電、I/O 和高速緩存,并將它們拆分為單獨(dú)的單元,以通過使用不同的方法針對所需的性能特性優(yōu)化每個單元類型的晶體管,然后也提高了成本。

完全分解標(biāo)準(zhǔn)芯片設(shè)計(jì)的目標(biāo)之一是將高速緩存/內(nèi)存拆分到 3D 堆疊設(shè)計(jì)中它們自己的不同層(更多內(nèi)容見下文),但這需要降低芯片堆棧頂部的復(fù)雜性。改造后端生產(chǎn)線 (BEOL:Back End of Line) 流程,重點(diǎn)是將晶體管連接在一起并實(shí)現(xiàn)通信(信號)和電力傳輸,是這項(xiàng)工作的關(guān)鍵。

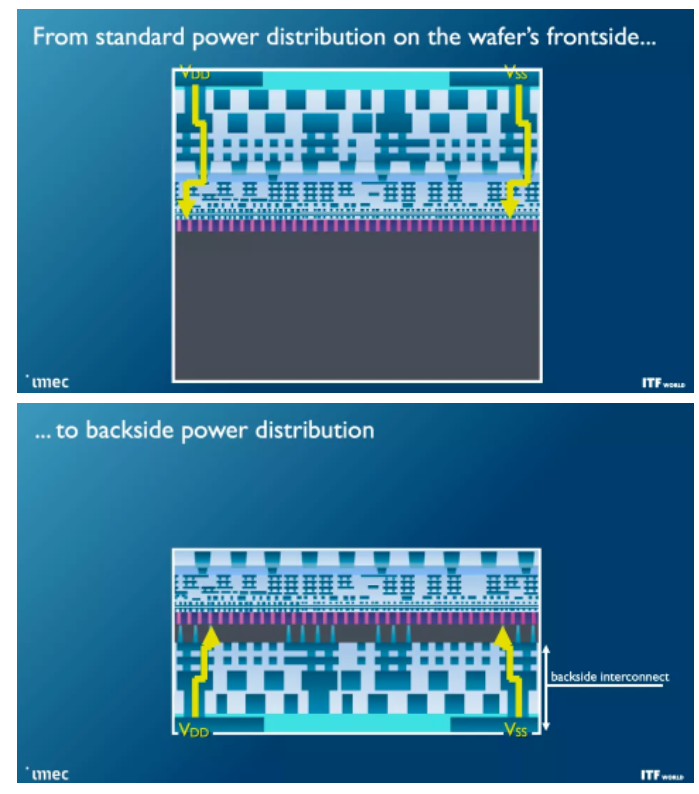

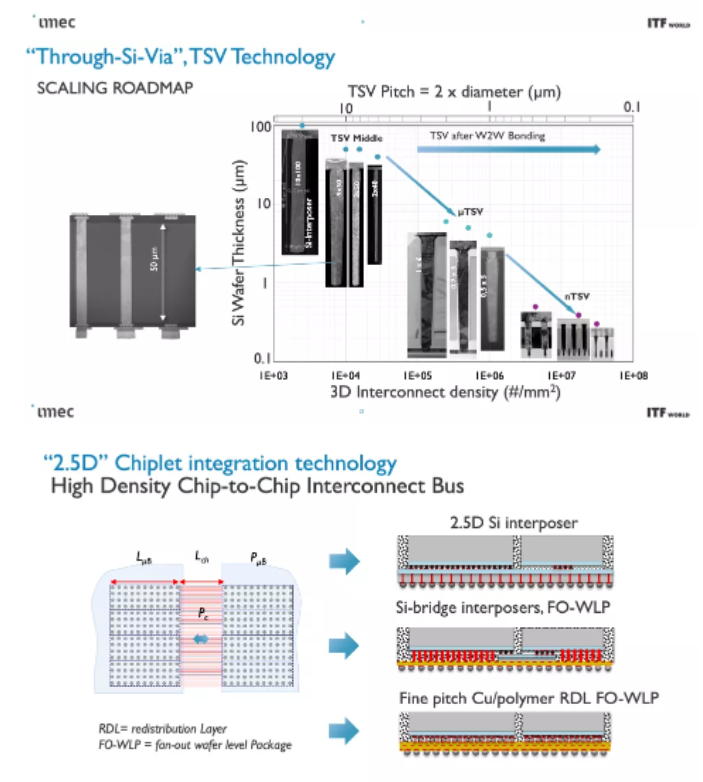

與當(dāng)今從芯片頂部向下向晶體管傳輸功率的設(shè)計(jì)不同,背面配電網(wǎng)絡(luò) (BPDN:backside power distribution networks ) 使用 TSV 將所有功率直接路由到晶體管的背面,從而將功率傳輸與保留在其內(nèi)部的數(shù)據(jù)傳輸互連分開另一邊的正常位置。將電源電路和數(shù)據(jù)傳輸互連分開可改善壓降特性,從而實(shí)現(xiàn)更快的晶體管開關(guān),同時在芯片頂部實(shí)現(xiàn)更密集的信號路由。信號完整性也有好處,因?yàn)楹喕牟季€可以更快地連接電阻和電容。

將供電網(wǎng)絡(luò)移至芯片底部可以更輕松地在裸片頂部進(jìn)行晶圓到晶圓的鍵合,從而釋放在存儲器上堆疊邏輯的潛力。Imec 甚至設(shè)想可能將其他功能轉(zhuǎn)移到晶圓的背面,例如全局互連或時鐘信號。

英特爾已經(jīng)宣布了自己的 BPDN 技術(shù)版本,稱為PowerVIA,將于 2024 年以intel 20A 節(jié)點(diǎn)首次亮相。英特爾將在即將舉行的 VLSI 活動中透露有關(guān)該技術(shù)的更多細(xì)節(jié)。同時,臺積電也宣布將BPDN引入其2026年量產(chǎn)的N2P節(jié)點(diǎn),因此這項(xiàng)技術(shù)將落后于英特爾相當(dāng)長的一段時間。也有傳言稱三星將在其 2nm 節(jié)點(diǎn)采用該技術(shù)。

CMOS 2.0 是 imec 對未來芯片設(shè)計(jì)愿景的巔峰之作,涵蓋了全 3D 芯片設(shè)計(jì)。我們已經(jīng)看到 AMD 第二代 3D V-Cache 的內(nèi)存堆疊,將 L3 內(nèi)存堆疊在處理器之上以提高內(nèi)存容量,但 imec 設(shè)想整個緩存層次結(jié)構(gòu)包含在其自己的層中,具有 L1、L2 和 L3 緩存垂直堆疊在構(gòu)成處理核心的晶體管上方的自己的芯片上。每個級別的緩存都將使用最適合該任務(wù)的晶體管創(chuàng)建,這意味著 SRAM 的舊節(jié)點(diǎn),隨著SRAM 縮放速度開始大幅放緩,

這變得越來越重要. SRAM 縮小的規(guī)模導(dǎo)致緩存占用了更高比例的裸片,從而導(dǎo)致每 MB 成本增加,并阻礙了芯片制造商使用更大的緩存。因此,將 3D 堆疊的緩存轉(zhuǎn)移到密度較低的節(jié)點(diǎn)所帶來的成本降低也可能導(dǎo)致比我們過去看到的緩存更大的緩存。如果實(shí)施得當(dāng),3D 堆疊還可以幫助緩解與較大緩存相關(guān)的延遲問題。

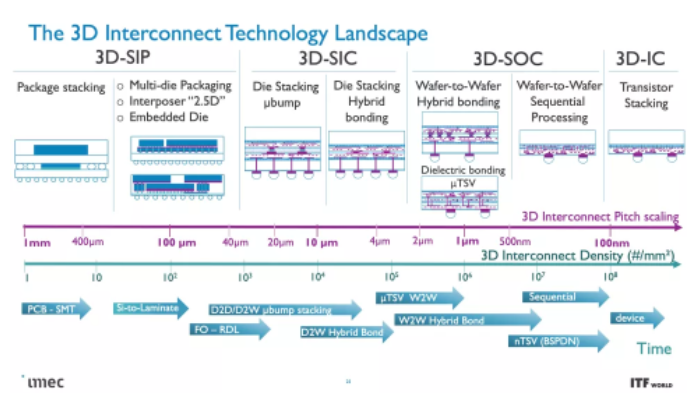

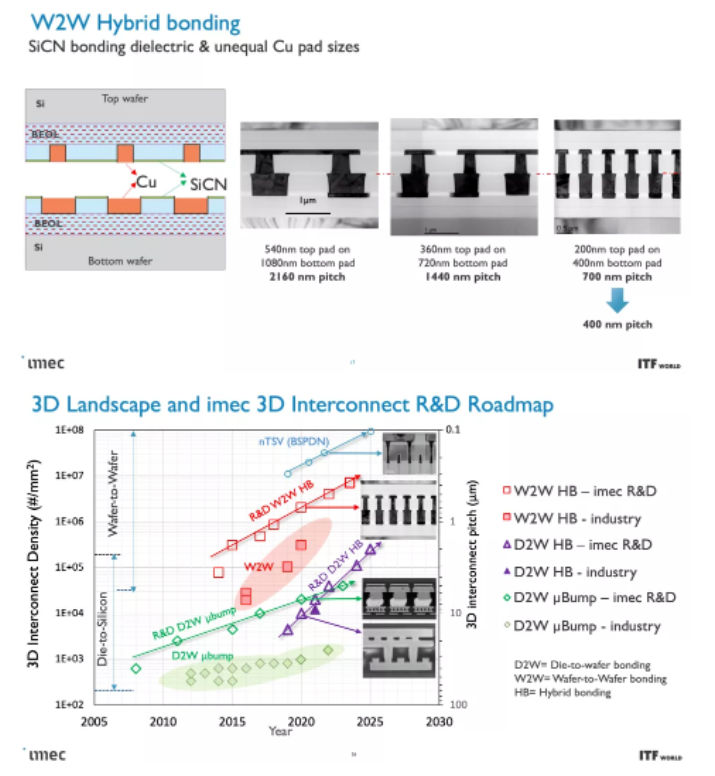

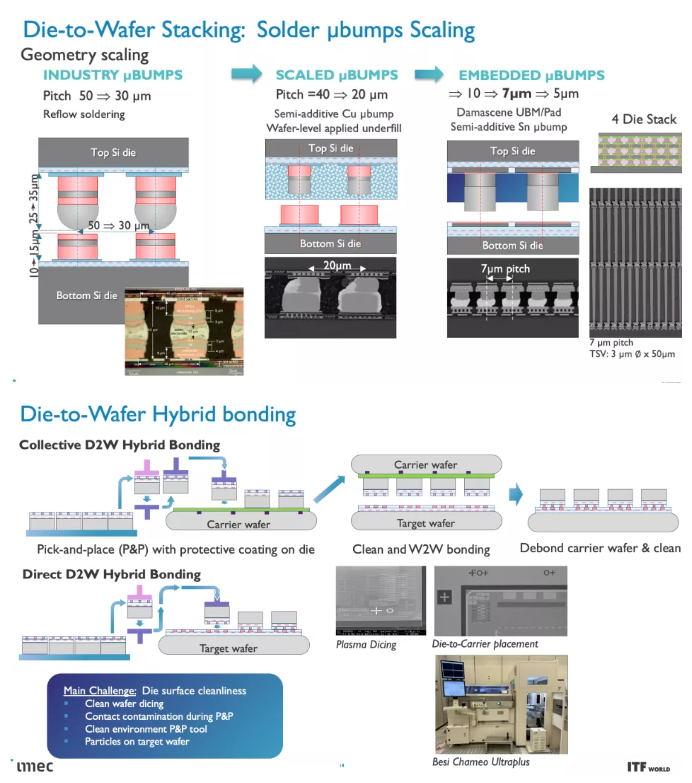

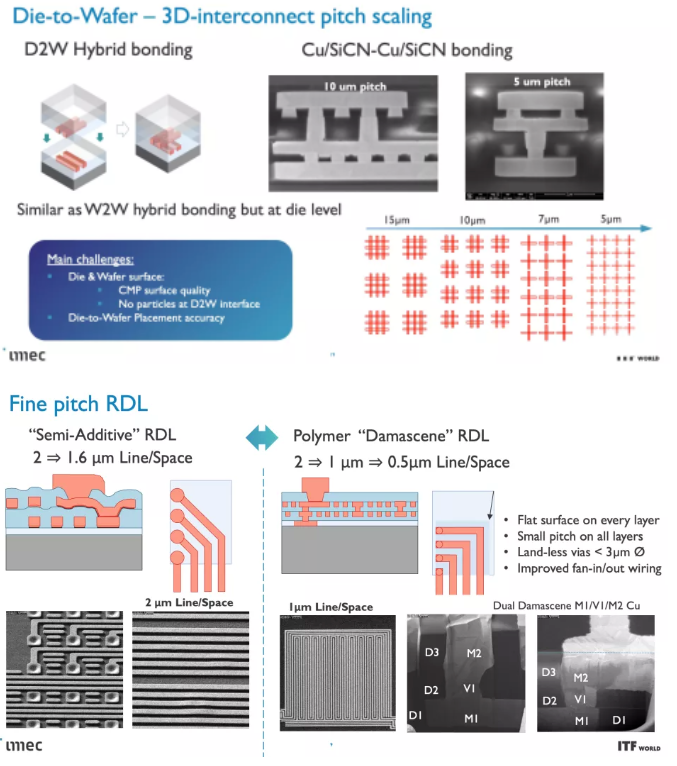

這些 CMOS 2.0 技術(shù)將利用 3D 堆疊技術(shù)(如晶圓到晶圓混合鍵合)來形成直接的芯片到芯片 3D 互連。

正如您在上面的專輯中看到的那樣,Imec 也有一個 3D-SOC 路線圖,概述了將 3D 設(shè)計(jì)結(jié)合在一起的互連的持續(xù)縮小,從而在未來實(shí)現(xiàn)更快、更密集的互連。這些進(jìn)步將在未來幾年通過使用更新類型的互連和處理方法來實(shí)現(xiàn)。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<