原文作者:arXiv

本文來源: 半導(dǎo)體行業(yè)觀察

原文鏈接:https://mp.weixin.qq.com/s/xKiDx3TCyCYB3FT9k3-ZsQ

摘要

在光通信發(fā)展的推動(dòng)下,硅光子技術(shù)已發(fā)展成為主流技術(shù)。目前的技術(shù)已經(jīng)使得集成光子器件從數(shù)千個(gè)激增到數(shù)百萬個(gè),它們主要以數(shù)據(jù)中心通信收發(fā)器的形式出現(xiàn),此外傳感和運(yùn)算等許多令人興奮的應(yīng)用領(lǐng)域的產(chǎn)品也指日可待。需要什么才能將硅光子器件的出貨量從數(shù)百萬增加到數(shù)十億?下一代硅光子技術(shù)會(huì)是什么樣子?硅光子應(yīng)用面臨的集成和制造瓶頸有哪些共同點(diǎn)?哪些新興技術(shù)可以解決這些問題?

這篇觀點(diǎn)文章試圖回答這些問題。我們繪制了硅光子學(xué)技術(shù)的發(fā)展趨勢(shì)圖,從CMOS技術(shù)的世代定義中進(jìn)行了比較。我們確定了在CMOS制造兼容器件、電路、集成和封裝方面取得巨大進(jìn)步所必須解決的關(guān)鍵挑戰(zhàn)。我們確定了對(duì)下一代系統(tǒng)和應(yīng)用至關(guān)重要的挑戰(zhàn)——通信、信號(hào)處理和傳感領(lǐng)域。通過發(fā)現(xiàn)和總結(jié)這些挑戰(zhàn)和機(jī)遇,我們旨在促進(jìn)對(duì)硅光子生態(tài)系統(tǒng)的器件、電路和系統(tǒng)的進(jìn)一步研究。

1.技術(shù)路線圖

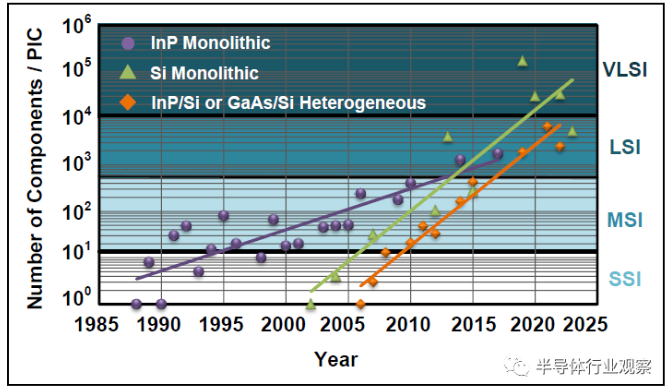

圖1 小規(guī)模、中等規(guī)模、大規(guī)模和超大規(guī)模集成(分別為SSI、MSI、LSI、VLSI)的硅光子集成電路(PIC)上組件數(shù)量的時(shí)間線。元件是指與其他單元組合以構(gòu)建電路的單元,如波導(dǎo)、定向耦合器、加熱器、光柵耦合器等。異質(zhì)硅光子學(xué)比混合型延遲約兩年。為了進(jìn)行比較,我們還展示了基于InP的集成光子學(xué)的數(shù)據(jù)。通常,高速調(diào)制器的數(shù)量越高,縮放就越具有挑戰(zhàn)性。

圖1展示了硅光子技術(shù)的演變。硅基光子集成電路(PIC)于1985年推問世,1991年至1992年在厚絕緣體上硅(SOI)工藝中實(shí)現(xiàn)了低損耗波導(dǎo)。接下來出現(xiàn)了各種光學(xué)器件。很快,硅光子就進(jìn)入了小規(guī)模集成(SSI)時(shí)代——在PIC上有1到10個(gè)組件,其中包括高速pn結(jié)調(diào)制器和光電探測(cè)器(PD),以及III-V激光器與硅PIC的異質(zhì)集成。下一個(gè)時(shí)代迎來了硅光子的商業(yè)成熟。在中等規(guī)模集成(MSI)時(shí)代,Mach-Zehnder調(diào)制器(MZM)成功用在數(shù)據(jù)中心內(nèi)的IMDD收發(fā)器中——PIC上有10到500個(gè)組件,包括單波長(zhǎng)和多波長(zhǎng)。基于微環(huán)調(diào)制器(MRM)的IMDD收發(fā)器(見圖2a)體現(xiàn)了PIC技術(shù)的多路復(fù)用和能效優(yōu)勢(shì)。硅光子/電子平臺(tái)中的相干收發(fā)器證明,該技術(shù)可以在性能上與LiNbO3光子和III-V族電子媲美。除了通信,硅光子還有更多新的應(yīng)用,如倏逝場(chǎng)生物傳感器。硅光子現(xiàn)在開始了大規(guī)模集成(LSI)的下一個(gè)時(shí)代——在同一芯片上實(shí)現(xiàn)500到10000個(gè)組件。LSI的應(yīng)用包括激光雷達(dá)(見圖2b)、圖像投影、光子開關(guān)、光子計(jì)算、可編程電路和多路復(fù)用生物傳感器。甚至超大規(guī)模集成電路(>10000個(gè)元件)的原型現(xiàn)在也已出現(xiàn)。在通信領(lǐng)域,一直是硅光子的重要市場(chǎng)驅(qū)動(dòng)力,硅光子已經(jīng)從SSI時(shí)代的挑戰(zhàn)者技術(shù)轉(zhuǎn)變?yōu)镸SI時(shí)代數(shù)據(jù)中心內(nèi)和數(shù)據(jù)中心間互連的主導(dǎo)技術(shù),并有望成為L(zhǎng)SI時(shí)代的主流技術(shù)。硅光子是使共封裝光學(xué)技術(shù)(CPO)取得成功、實(shí)現(xiàn)高性能計(jì)算的規(guī)模化、實(shí)現(xiàn)分解計(jì)算的關(guān)鍵。

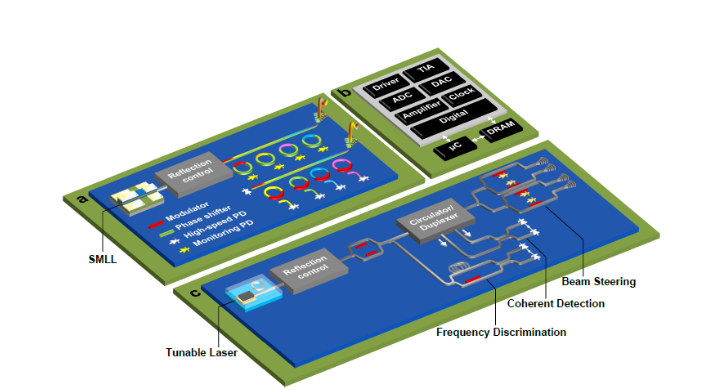

圖2 當(dāng)前和未來技術(shù)的LSI硅光子系統(tǒng)的示意圖:a.WDM收發(fā)器:SMLL向緊湊的、具有WDM功能的調(diào)制器和濾波器陣列提供多波長(zhǎng)CW光。反射控制電路限制反向反射進(jìn)入激光器。高速PD執(zhí)行O/E轉(zhuǎn)換。b.然后電流由TIA和限幅放大器放大。ADC用于將信號(hào)數(shù)字化以用于進(jìn)一步的DSP。監(jiān)測(cè)PD用于控制和穩(wěn)定波長(zhǎng)、相移和溫度。DAC和驅(qū)動(dòng)器用于數(shù)字信號(hào)的E/O調(diào)制。DRAM提供大的內(nèi)存訪問。微控制器也可以用于進(jìn)行一些數(shù)字處理。c.激光雷達(dá):可調(diào)諧激光器為移相器、循環(huán)器/雙工器和相干前端網(wǎng)絡(luò)提供頻率啁啾光,用于零差/外差FMCW測(cè)距和檢測(cè)。使用OPA/FPA進(jìn)行光束探測(cè)。延遲線干涉儀通過直接控制可調(diào)諧激光器或調(diào)制器以及通過DSP進(jìn)行各種形式的誤差校正,有助于校準(zhǔn)接收到的拍頻,并支持線性調(diào)頻。

2.硅光子技術(shù)的技術(shù)視角

經(jīng)過幾代CMOS工藝的發(fā)展,許多材料被添加到硅中,以降低功率、提高性能和縮小面積——這些通常被稱為PPA指標(biāo)。添加物包括用于金屬跡線的Al和Cu,用于誘導(dǎo)應(yīng)變和實(shí)現(xiàn)異質(zhì)結(jié)BJT的Ge,以及用于鈍化和擴(kuò)散勢(shì)壘的氮化硅(SiN)。CMOS的研發(fā)預(yù)算和商業(yè)市場(chǎng)比硅光子技術(shù)大幾個(gè)數(shù)量級(jí)。因此,我們?cè)诠韫庾庸に嚨陌l(fā)展中也看到了類似的趨勢(shì)。除了用于高速調(diào)制的p/n摻雜劑之外,現(xiàn)在由幾個(gè)晶圓廠原生支持的兩種材料是(1)Ge高速光電探測(cè)器和(2)SiN,以擴(kuò)展波長(zhǎng)范圍,實(shí)現(xiàn)更高的光功率,并在干涉測(cè)量器件中支持具有更低損耗和更好相位控制的波導(dǎo)。

縮小面積將是LSI和VLSI時(shí)代下一個(gè)十年硅光子工藝開發(fā)的重點(diǎn)。事實(shí)上,最大的密度限制很少來自器件尺寸;消除串?dāng)_的波導(dǎo)之間的間距比實(shí)際波導(dǎo)的尺寸大得多。對(duì)于射頻(RF)器件,有源元件之間的間距(臨界尺寸為微米)通常為數(shù)百微米,以消除射頻串?dāng)_。縮小這些“空白”需要非常詳細(xì)的系統(tǒng)級(jí)模擬和充分的多物理建模,這將是制造更小、更便宜、更高密度芯片的核心。無源器件本身的尺寸減小通常受到折射率對(duì)比度和1-2μm的工作波長(zhǎng)的限制。使用反向設(shè)計(jì)技術(shù)來收縮無源構(gòu)建塊仍有一些余量,但波導(dǎo)本身不能真正收縮到今天硅平臺(tái)的400-500 nm寬度以下。然而,在光學(xué)I/O耦合器和高速調(diào)制器中仍然可以實(shí)現(xiàn)顯著的縮放。為了耦合到光纖,帶有邊緣耦合器的V形槽以相當(dāng)大的芯片面積為代價(jià),提供了低損耗、易于頂包連接。沒有V形槽的邊緣耦合器更小,但需要更精確的主動(dòng)對(duì)準(zhǔn),從而增加了成本。多芯光纖是一種很有吸引力的解決方案。主要的替代耦合方法是通過光柵耦合器,它緊湊的特性提供了在芯片表面上定位的靈活性,能夠進(jìn)行晶圓級(jí)測(cè)試,并且也可以以低插入損耗(IL)來實(shí)現(xiàn),但存在偏振和溫度敏感性以及較低的光帶寬。無源對(duì)準(zhǔn)封裝技術(shù),如光子引線鍵合(PWB),提供了一種有吸引力的潛在替代方案,對(duì)其組件進(jìn)行更多的可靠性研究將有助于其廣泛應(yīng)用。

2.1 E/O 調(diào)制

下一個(gè)十年的探索旨在縮小光子芯片從而提高密度,即在硅光子中找到難以捉摸的“理想”調(diào)制器——長(zhǎng)度(L)小、需要小的驅(qū)動(dòng)電壓來產(chǎn)生π相移(Vπ)、提供低的傳播損耗(α)和IL,對(duì)于一些應(yīng)用,具有高線性和大-3dB E/O帶寬(BW)。此外,該調(diào)制器優(yōu)選的是移相器,因?yàn)檫@能夠?qū)崿F(xiàn)更高階相干調(diào)制格式。

2.1.1 高速調(diào)制器

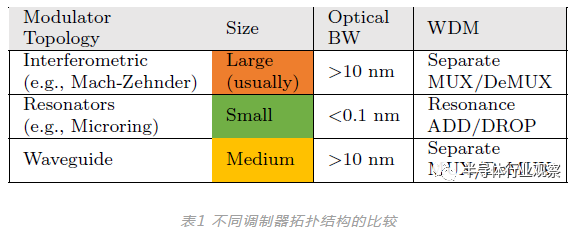

基于波導(dǎo)的調(diào)制器(表1)的常用效率品質(zhì)因數(shù)(FoMeefficiency)為αVπL。對(duì)于非常緊湊的MRM,由于α引起的損耗變得不那么關(guān)鍵,并且更好的FoMeefficiency包含IL和Vpp(特定光學(xué)調(diào)制幅度或OMA的峰間電壓擺動(dòng))。所有調(diào)制器都要在FoMeefficiency和E/O BW之間進(jìn)行權(quán)衡。最后,驅(qū)動(dòng)器中消耗的功率取決于驅(qū)動(dòng)器所看到的調(diào)制器阻抗。電阻阻抗(端接行波調(diào)制器)消耗靜態(tài)(DC)和動(dòng)態(tài)(AC)功率,而高阻抗(電容性)主要消耗動(dòng)態(tài)功率。由于需要增加激光功率來補(bǔ)償損耗,因此高IL也是較高功耗的代表。

除了拓?fù)浣Y(jié)構(gòu)之外,調(diào)制器的PPA度量還取決于用于調(diào)制的材料和機(jī)制。表2顯示了在各種硅光子工藝中用于調(diào)制器的不同材料。利用自由載流子等離子體色散的p-n摻雜劑目前在所有商業(yè)硅光子晶圓廠都可以買到,支持60 GHz甚至更高的E/O BW。目前,商業(yè)市場(chǎng)主要由行波MZM調(diào)制器形式的此類器件主導(dǎo)。等離子體在硅中的分散導(dǎo)致了中等的FoM效率,對(duì)于平均OMA具有高的IL。載波積累允許較短的MZM,但有BW限制。當(dāng)實(shí)現(xiàn)為MRM時(shí),器件要小得多,但I(xiàn)L和OMA對(duì)于支持LSI/VLSI IC來說仍然是次優(yōu)的。

由于Ge PD已經(jīng)得到了大多數(shù)商業(yè)硅光子晶圓廠的支持,各個(gè)團(tuán)隊(duì)都試圖使用GeSi,一種相關(guān)但不完全相同的技術(shù),來實(shí)現(xiàn)更好的調(diào)制器。基于Franz-Kelydysh效應(yīng)的GeSi電吸收調(diào)制器(EAM)可以在高E/O BW的C/L波段工作。然而,它們通常不是光學(xué)寬帶,因?yàn)樗鼈兪褂脦н呎{(diào)制進(jìn)行吸收。對(duì)于O波段操作,利用量子受限斯塔克效應(yīng)(QCSE)的調(diào)制器仍然存在較大的IL。雖然在這一領(lǐng)域已經(jīng)進(jìn)行了多次學(xué)術(shù)和商業(yè)探索,但尚不清楚這些調(diào)制器是否會(huì)進(jìn)入未來幾代的商業(yè)器件。

InP到CMOS的異質(zhì)集成已經(jīng)引起了電子和光子學(xué)研究者的興趣。對(duì)于光子學(xué),它為IMDD收發(fā)器的大批量制造(HVM)中的激光集成鋪平了道路,并正在用于SOA集成。鑒于這些集成努力,InP/Si調(diào)制器仍然非常有前途。用于C/L/O帶的InP/Si EAM已經(jīng)被證明,并且在至少一個(gè)硅光子晶圓廠中可用。

最“純”的電光調(diào)制依賴于Pockels效應(yīng),它提供了本質(zhì)上非常高的E/O BW,甚至超過100 GHz,但這些材料在CMOS集成方面面臨諸多挑戰(zhàn),并且很少或根本沒有與CMOS集成用于電子器件的歷史(與已經(jīng)在CMOS電子器件中引入的Ge和SiN相比)。絕緣體上LiNbO3(LNOI)調(diào)制器提供低IL,并已與源極和PD集成。然而,其αVπL產(chǎn)物需要進(jìn)一步解決。鋰是CMOS制造廠的污染物,其使用可以使用BEOL集成或封裝技術(shù)來解決。聚合物-硅-有機(jī)雜化物(SOH)和等離子體-有機(jī)雜化體(POH)需要極化和氣密密封,這給制造穩(wěn)定的器件帶來了重大挑戰(zhàn)。盡管最近的結(jié)果很有希望,但它們的高溫可靠性和回流兼容性仍有待進(jìn)一步證明。POH調(diào)制器,盡管它們?cè)赑PA指標(biāo)中看起來很有吸引力,但與CMOS SOI制造的兼容性更差。良好的等離子體金屬(Cu、Ag、Au)也是嚴(yán)重的污染物,并且需要光學(xué)損耗很大的擴(kuò)散阻擋層(例如TaN)。鐵電薄膜材料(如BaTiO3)的多晶層顯示出比LNOI大得多的Pockels系數(shù)(以pm/V表示),并且與聚合物相當(dāng),最近大的E/O BW的證明使它們很有前景。注意,器件中的大波克爾系數(shù)是非常重要的,這需要電調(diào)制場(chǎng)和傳播光學(xué)模式的良好重疊。一般來說,對(duì)Ge PD處理和回流的兼容性將是商業(yè)晶圓廠采用新調(diào)制器技術(shù)的要求。

改善所有PPA指標(biāo)和HVM適用性對(duì)于商業(yè)晶圓廠和LSI應(yīng)用至關(guān)重要。然而,由于大量的光子應(yīng)用,將始終需要極高的E/O BW調(diào)制器,一些專注于原型和研發(fā)晶圓廠將繼續(xù)解決相關(guān)的制造挑戰(zhàn)。最后,盡管>100 GHz E/O BW調(diào)制器對(duì)電信和數(shù)據(jù)中心應(yīng)用都很有吸引力,但它們需要能夠以這樣的速度驅(qū)動(dòng)它們的電子器件。除非Vπ(或Vpp)顯著降低,否則無論CMOS/BiCMOS/III-V實(shí)現(xiàn)如何,這種電子器件都將消耗大量功率。

2.1.2 用于調(diào)諧和切換的移相器

許多光子應(yīng)用需要消耗很少或不消耗功率的移相器,并且具有用于配置、調(diào)諧和切換的低αVπL。對(duì)于某些應(yīng)用,這些移相器也應(yīng)該具有很高的速率,但不需要10GHz E/O BW。雖然在許多電路中,光只通過一個(gè)高速調(diào)制器,但它必須穿過許多低速移相器進(jìn)行調(diào)諧和切換。利用熱光效應(yīng)的金屬加熱器(或摻雜波導(dǎo)),如今可用于所有制造平臺(tái)。它們具有1-10μs的響應(yīng)時(shí)間,并且消耗相當(dāng)大的功率,產(chǎn)生熱串?dāng)_,從而限制LSI/VLSI的縮放。改善熱絕緣降低了它們的功耗,但代價(jià)是更高的響應(yīng)時(shí)間。

圖3b中列出的最后一組材料和技術(shù)是加熱器的有吸引力的替代品。它們包括液晶(LC)、MEMS/NOEMS和相變材料(PCM)。用于顯示應(yīng)用的硅上LC(LCOS)調(diào)諧已經(jīng)被大規(guī)模地證明,并且LC也是自由空間波長(zhǎng)選擇開關(guān)的選擇技術(shù)。作為移相器,它們使用極低的功率,但目前受到IL的影響,盡管最近在可見光波段已經(jīng)證明了極低的IL。芯片上的液體集成帶來了一系列溫度和封裝方面的挑戰(zhàn),基于PCM的非易失性存儲(chǔ)器已經(jīng)在電子工業(yè)中實(shí)現(xiàn)了HVM,并且正在被探索用于神經(jīng)網(wǎng)絡(luò)應(yīng)用。PCM在硅光子中的使用承諾了緊湊的調(diào)諧能力,但存在高IL和顯著的動(dòng)態(tài)功耗。基于MEMS/NOEMS的移相器本質(zhì)上是低功率的,并且已經(jīng)在多家晶圓廠進(jìn)行了驗(yàn)證。諸如用光學(xué)和電氣饋通進(jìn)行氣密密封等挑戰(zhàn)是可以解決的。最后,BaTiO3等材料有望實(shí)現(xiàn)高速調(diào)制和高效相移,但代價(jià)是面臨非常嚴(yán)峻的技術(shù)和經(jīng)濟(jì)整合挑戰(zhàn)。

2.2 激光集成

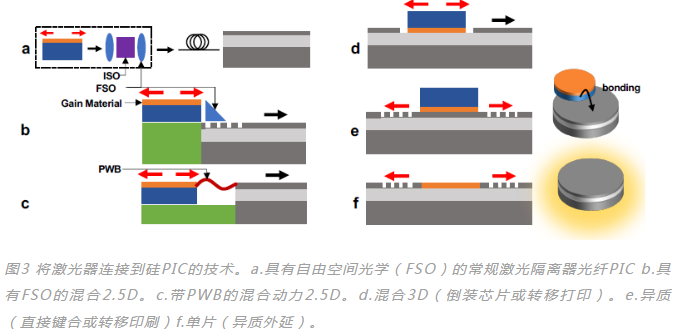

硅的間接帶隙阻礙了PIC上的激光器(CW載波)所需的有效光學(xué)增益。這種缺陷需要替代材料或方法在硅片上引入光源,過去幾十年的發(fā)展中涌現(xiàn)了不同的解決方案(圖3)。傳統(tǒng)技術(shù)是用激光器和隔離器將PIC光纖連接起來(圖第3a段)。更具可擴(kuò)展性的方法將III-V族增益材料與不含光纖的PIC集成在一起。但是,如果激光器不能容忍反射,仍然需要一個(gè)隔離器。芯片外隔離器性能良好,但體積龐大,增加了封裝復(fù)雜性和成本。務(wù)實(shí)地說,通常可以設(shè)計(jì)芯片和封裝,避免背反成為限制因素;傳輸路徑中的高損耗在外部世界和任何光源之間提供了屏障。當(dāng)設(shè)計(jì)成封裝時(shí),可以管理緊湊型隔離器的成本。芯片上反射控制方法(圖2)可以消除對(duì)大體積隔離器的需求,包括仔細(xì)設(shè)計(jì)光子組件以將反射降低到激光器的容差閾值以下、通過使用具有低線寬增強(qiáng)因子的量子點(diǎn)增益區(qū)域來降低激光器的反射靈敏度、磁光材料的單片集成(例如,Ce:YIG)、時(shí)空調(diào)制器或有源反射消除電路。一種對(duì)近端(相干)和遠(yuǎn)端(非相干)調(diào)制多波長(zhǎng)反射具有魯棒性的通用、低成本、可擴(kuò)展、片上、低損耗、低功耗和緊湊的解決方案仍然是一個(gè)研究問題。

激光集成的一個(gè)實(shí)用解決方案是混合集成,將來自不同材料技術(shù)的多個(gè)芯片共同封裝在一起。例如,為數(shù)據(jù)通信應(yīng)用制造并經(jīng)過預(yù)測(cè)試的低成本高產(chǎn)量的(亞)毫米DFB激光器可以與硅光子芯片共同封裝。一種商業(yè)上成功的2.5D集成技術(shù)將已知良好的激光器同環(huán)氧樹脂、球透鏡和隔離器共同封裝(圖第3b段)。其他2.5D技術(shù)包括使用對(duì)接耦合或光子引線鍵合來實(shí)現(xiàn)松弛的對(duì)準(zhǔn)公差(圖3c)。這些2.5D技術(shù)足以用于當(dāng)今的幾種定制硅光子應(yīng)用。混合3D集成技術(shù)(倒裝芯片或微轉(zhuǎn)印)有望以使用PIC區(qū)域?yàn)榇鷥r(jià)進(jìn)一步縮小組件尺寸(圖3D),但需要高精度的放置和粘合。

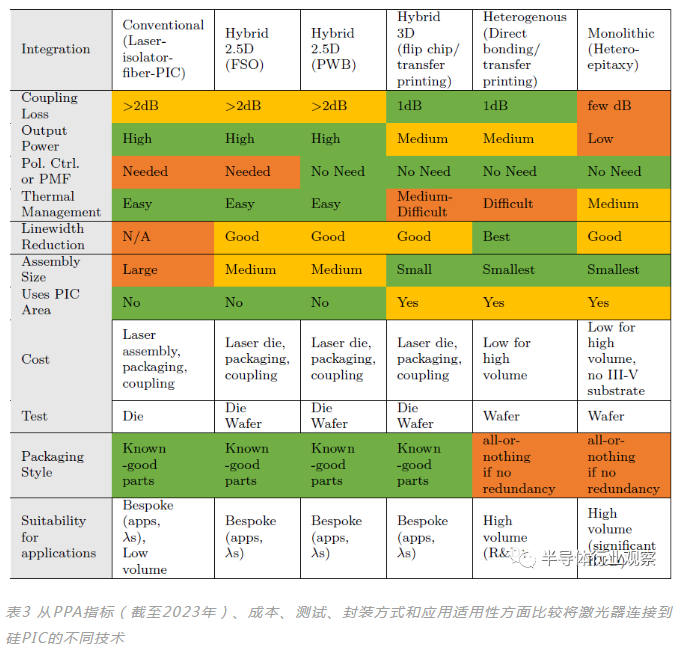

表3總結(jié)了各種集成方案的PPA和其他指標(biāo)。大多數(shù)C/L/O波段激光器的壁塞效率(WPE)僅約為10%,這一指標(biāo)需要更集中的研究來改進(jìn)。對(duì)于類似的WPE,激光器與PIC之間的耦合損耗可以作為功耗的代表。在2.5D混合集成中,單獨(dú)的激光器提供了選擇具有所需光功率的激光器的靈活性,并且熱管理也很容易。為了實(shí)現(xiàn)更高的功率處理,可以在PIC上使用SiN。有一些方法可以從DFB的典型線寬提高激光器的線寬,也可以消除反射以提高隔離。具有高Q Si或SiN外腔的3D技術(shù)支持將線寬降低至1 Hz及更低,足以用于相干通信和汽車激光雷達(dá)等應(yīng)用。混合集成還允許多個(gè)波長(zhǎng)。盡管如此,相對(duì)于需要多個(gè)激光器、增益元件等的>8λWDM LSI PIC的擴(kuò)展,混合集成的好處仍有待徹底證明。

HVM中另一項(xiàng)商業(yè)上成功的技術(shù)是異質(zhì)集成,即在晶圓級(jí)將多種材料或外延堆疊一起加工成一個(gè)硅片。此外,還采取了各種戰(zhàn)略,它們包括通過粗對(duì)準(zhǔn)將III-V族芯片結(jié)合到Si上,然后對(duì)Si晶片進(jìn)行后處理以制造量子阱(QW)激光器(圖3e)。為了實(shí)現(xiàn)高溫操作、效率和可靠性,必須仔細(xì)解決掩埋氧化物(BOX)對(duì)增益介質(zhì)的熱隔離和不匹配的熱膨脹系數(shù)問題。放置冗余激光器有助于提高故障及時(shí)率。異質(zhì)方法的好處包括亞dB耦合損耗,這是一種利用硅中的低損耗外腔使用自注入鎖定顯著降低激光線寬的機(jī)制。

量子點(diǎn)(QD)激光器所需的另一種長(zhǎng)期方法是在硅晶片上直接生長(zhǎng)外延增益材料。由于其較低的線寬增強(qiáng)因子αH,QD激光器能夠?qū)崿F(xiàn)較低的帶寬和降低的反射靈敏度。它們還具有較低的閾值電流密度。使用異質(zhì)外延生長(zhǎng)的單片集成(圖3f),其中甚至不需要III-V襯底,仍然是最終目標(biāo)。

多家硅光子晶圓廠正在開發(fā)混合或異質(zhì)激光解決方案。出于可擴(kuò)展性的目的,它們可能會(huì)傾向于支持多波長(zhǎng)的技術(shù),這對(duì)一些LSI應(yīng)用至關(guān)重要。很可能首先通過結(jié)合多個(gè)單波長(zhǎng)激光器來支持橫向擴(kuò)展。梳狀激光器,如無源半導(dǎo)體鎖模激光器(SMLL),正被各種研究小組積極研究。DFB陣列確保在每個(gè)波長(zhǎng)中都有大的輸出光功率,而在SMLL中,功率在波長(zhǎng)之間分配,降低了SNR。可飽和吸收體的存在進(jìn)一步降低了SMLL的總輸出功率(并因此降低了每波長(zhǎng))。然而,SMLL明顯小于DFB陣列。無源SMLL的線寬通常低于DFB陣列。預(yù)計(jì)SMLL將在未來十年進(jìn)行更多的研發(fā),以展示更高的功率、可靠性和壽命。這種對(duì)DWDM應(yīng)用的要求甚至更嚴(yán)格,任何溫度漂移都會(huì)產(chǎn)生通道間串?dāng)_。

2.3 雪崩光電探測(cè)器

大多數(shù)硅光子應(yīng)用受到激光器輸出功率和WPE有限以及電路中高IL的限制。一種替代方案是在檢測(cè)階段提高SNR(圖2)。低電壓APD具有大的-3dB O/E BW、高的整體響應(yīng)度和同時(shí)低的噪聲,將有利于提高接收機(jī)的信噪比。需要注意的是,整體響應(yīng)度(以A/W為單位)和低噪聲至關(guān)重要。具有差的固有響應(yīng)性的APD的大的倍增增益不會(huì)延伸出優(yōu)越的性能。盡管在硅APD中相對(duì)更容易實(shí)現(xiàn),但同時(shí)優(yōu)化增益-BW噪聲對(duì)于低電壓Si/Ge APD來說仍然具有挑戰(zhàn)性。與Ge PD相比,APD通常具有較差的BW、線性度和功率,這限制了它們?cè)诟鞣N應(yīng)用中的使用。APD還需要針對(duì)溫度和電壓漂移進(jìn)行最佳偏置和穩(wěn)定,但這也比已經(jīng)證明的微環(huán)電路具有更小挑戰(zhàn)性。

3.硅光子技術(shù):系統(tǒng)視角

3.1 光子&電子相輔相成

硅PIC幾乎總是與電子IC(EIC)一起存在。當(dāng)我們審視基于光子芯片的系統(tǒng)時(shí),今天的格局幾乎100%由數(shù)據(jù)通信主導(dǎo),我們預(yù)計(jì)這種情況將在不久的將來繼續(xù)持續(xù)下去。在這種情況下,EIC有幾個(gè)用途(圖2):(1)啟用端到端數(shù)據(jù)的E/O和O/E轉(zhuǎn)換。(2) 對(duì)溫度和制造變化進(jìn)行偏置、控制和補(bǔ)償。因此,光子學(xué)通過提供數(shù)據(jù)鏈路為電子器件服務(wù),而電子器件通過提供控制和讀出以及數(shù)字信號(hào)處理(DSP)為光子學(xué)服務(wù)。光子學(xué)和電子學(xué)之間的一個(gè)主要區(qū)別是,光子不相互作用,因此非常適合信息傳輸,而電子相互作用并相互排斥,因此是很好的開關(guān)和計(jì)算元件。因此,每個(gè)硅光子開關(guān)都需要相應(yīng)的電子開關(guān)。總的來說,必須伴隨LSI PIC的EIC中的晶體管數(shù)量比PIC中的組件數(shù)量大幾個(gè)數(shù)量級(jí)。這是一種自然的相互作用,因?yàn)榫w管在(1)開關(guān)、(2)提供增益(線性和限制性)和(3)提供高精度時(shí)消耗的功率要低得多,同時(shí)比光子組件小幾個(gè)數(shù)量級(jí)。另一方面,與銅相比,光子組件(1)在較長(zhǎng)距離上移動(dòng)數(shù)據(jù)時(shí)能夠?qū)崿F(xiàn)較低的頻率相關(guān)損耗,(2)可以通過異步和無中繼器的數(shù)據(jù)移動(dòng)提供較低的延遲,以及(3)使非常高速的數(shù)據(jù)在光波導(dǎo)上的并行性(通過WDM)變得容易。當(dāng)數(shù)據(jù)已經(jīng)在光域中時(shí),光子信號(hào)切換或處理可能會(huì)變得有吸引力。前者是一種廣泛部署的技術(shù),而后者尚未實(shí)現(xiàn)從研究到產(chǎn)品的飛躍,以取代DSP的功能。因此,認(rèn)識(shí)到PIC和EIC技術(shù)各自的優(yōu)點(diǎn)是很好的。例如,必須仔細(xì)分析光子域中處理電子數(shù)據(jù)的E/O和O/E開銷。相反,硅光子技術(shù)為縮小大型光學(xué)系統(tǒng)提供了機(jī)會(huì),并將新的應(yīng)用(如傳感和成像)帶到了現(xiàn)實(shí)中,而電子技術(shù)本身無法實(shí)現(xiàn)這些應(yīng)用。最后,硅光子技術(shù)在數(shù)百太赫茲的載波上工作,而硅電子器件僅限于亞太赫茲。這種不同的屬性開啟了有吸引力的共同設(shè)計(jì)機(jī)會(huì),例如設(shè)計(jì)具有超低相位噪聲的電子時(shí)鐘。

3.2 光子&電子生態(tài)系統(tǒng)

摩爾定律表明,每一代CMOS技術(shù)都會(huì)降低晶體管的關(guān)鍵尺寸,從而降低每個(gè)組件的成本。隨著時(shí)間的推移,半導(dǎo)體行業(yè)的經(jīng)濟(jì)規(guī)模呈指數(shù)級(jí)增長(zhǎng),這使得該行業(yè)能夠?yàn)樵絹碓桨嘿F的晶圓廠和工藝開發(fā)買單。晶圓廠使許多用戶能夠訪問這些高級(jí)流程,而無需每個(gè)用戶自己付費(fèi)開發(fā)流程。在最極端的情況下,晶圓廠托管的MPW(多項(xiàng)目晶圓)運(yùn)行允許多個(gè)用戶分擔(dān)單個(gè)晶圓運(yùn)行的成本,以經(jīng)濟(jì)高效地開發(fā)產(chǎn)品。

隨著工藝的成熟,產(chǎn)量上升并且成本下降。晶圓廠和第三方知識(shí)產(chǎn)權(quán)(IP)供應(yīng)商能夠提供工藝設(shè)計(jì)工具包(PDK)和設(shè)計(jì)IP庫,使客戶能夠構(gòu)建極其復(fù)雜的電子電路,并在第一時(shí)間將其做好。通過依靠久經(jīng)考驗(yàn)的器件和久經(jīng)考驗(yàn)的電路級(jí)IP,設(shè)計(jì)師可以專注于片上系統(tǒng)(SoC)集成,而在某些情況下永遠(yuǎn)不會(huì)觸及晶體管級(jí)別。

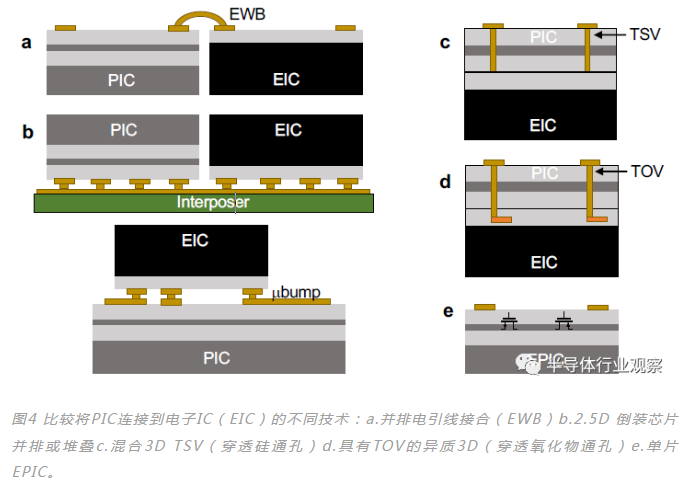

一旦芯片被制造出來,就會(huì)有一個(gè)由測(cè)試公司、封裝服務(wù)提供商等組成的豐富生態(tài)系統(tǒng)。引線接合(圖4a)和倒裝接合(具有C4凸塊和微凸塊,圖4b)是可靠且流行的封裝方式,后者提供更多的凸塊而不僅僅是外圍連接。更先進(jìn)的封裝技術(shù)(見圖4),如通硅過孔(TSV)、無TSV內(nèi)插器和異質(zhì)集成,用于通過將復(fù)雜的大型SoC分解成更小的小芯片來提高信號(hào)完整性、功率和熱分布以及管芯成品率。由于FPGA、GPU和CPU都是在HVM中生產(chǎn)的,盡管封裝技術(shù)復(fù)雜,但總體成本仍在下降。然而,明智的封裝決策是為了避免不必要的復(fù)雜性;一般來說,最簡(jiǎn)單的封裝是最好的,并且只有在沒有其他替代方案可行的情況下,才會(huì)引入先進(jìn)的封裝技術(shù)(晶片上芯片、芯片堆疊等)。

光子學(xué)行業(yè)有幾個(gè)相似之處,但也有許多明顯的差異。就像在電子行業(yè)一樣,增加光子組件的數(shù)量并不總是為了降低成本,而是為了提供新的功能、提高性能或減少每個(gè)組件的面積。盡管成熟的PDK和抽象語言仍處于非常早期的階段,但現(xiàn)在許多晶圓廠都可以運(yùn)行MPW。到目前為止,第三方知識(shí)產(chǎn)權(quán)支持基本上不存在。公司采用最先進(jìn)的PIC工藝來保護(hù)其投資和知識(shí)產(chǎn)權(quán)。這讓人想起CMOS行業(yè)的前幾十年,作為虛擬集成器件制造商(IDM),在工藝和PDK層面保持差異化。同時(shí),學(xué)術(shù)研究主要集中在器件的改進(jìn)上。

光子晶圓廠面臨著一個(gè)重大的困境:他們的客戶經(jīng)常要求他們定制工藝,這涉及到大量的研發(fā)費(fèi)用,并危及最終晶圓的可靠性和產(chǎn)量。推動(dòng)客戶進(jìn)入標(biāo)準(zhǔn)流程是解決這一問題的解決方案,但為了做到這一點(diǎn),客戶需要看到穩(wěn)定性以及穩(wěn)定的PDK和IP生態(tài)系統(tǒng)中的重大價(jià)值;只有少數(shù)設(shè)計(jì)師是這樣看待問題的,因?yàn)榻裉煸O(shè)計(jì)界的許多成員都是作為器件設(shè)計(jì)師而不是SoC設(shè)計(jì)師接受培訓(xùn)的。在這樣的設(shè)計(jì)者看來,改變工藝參數(shù)通常是產(chǎn)生性能差異的最簡(jiǎn)單方法,但從可靠性和工藝維護(hù)的角度來看,這種改變的下游成本可能非常高。隨著越來越多習(xí)慣于固定PDK想法的設(shè)計(jì)師畢業(yè)并進(jìn)入該領(lǐng)域,破壞性的流程變化將慢慢變得越來越不常見;晶圓廠也可能會(huì)越來越抗拒來自客戶的流程變化,而這些變化并沒有得到大量采購承諾的證明。

3.3 光子&電子共同集成

自從第一個(gè)商業(yè)上成功的硅光子產(chǎn)品問世以來,PIC與EIC集成的選擇就一直存在。開發(fā)單片EPIC工藝(圖4e),從CMOS(或BiCMOS)SOI工藝開始,并針對(duì)光子應(yīng)用對(duì)其進(jìn)行優(yōu)化,已多次獲得成功。從商業(yè)化和上市時(shí)間的角度來看,單片EPIC通常“似乎”是首選的優(yōu)越技術(shù)(表4)。驅(qū)動(dòng)器和TIA等高速電路可以與調(diào)制器和PD并排放置,從而減少寄生效應(yīng)和功耗。控制器(熱、波長(zhǎng))可以被設(shè)計(jì)并放置在光子組件旁邊,而不需要專用焊盤。對(duì)于LSI應(yīng)用,單片EPIC可以顯著簡(jiǎn)化封裝復(fù)雜性。然而,當(dāng)管芯區(qū)域由光子(光子元件比電子元件大幾個(gè)數(shù)量級(jí))主導(dǎo)時(shí),在沒有充分利用CMOS器件的情況下,整體管芯成本可能會(huì)顯著增加。這種分析必須針對(duì)個(gè)別產(chǎn)品逐一進(jìn)行。

原則上,在開發(fā)出具有卓越FoMeefficiency的下一代調(diào)制器之前,基于微環(huán)的電路似乎對(duì)單片EPIC工藝非常有吸引力(第2.1.1節(jié))。但要得出它們?cè)诮o定的特定應(yīng)用中是否有意義的結(jié)論,需要進(jìn)行完整的系統(tǒng)分析;微環(huán)具有相當(dāng)大的控制開銷和性能權(quán)衡,尤其是在非常高的速度下。如果應(yīng)用需要高速ADC/DAC,尤其是DSP(圖2),還必須添加另一個(gè)finFET EIC以節(jié)省功耗,因?yàn)槟壳霸?5 nm CMOS SOI中最快的單片EPIC工藝仍然比finFET工藝慢幾代(扇出延遲)。在未來幾年內(nèi),將光子組件直接集成到45nm節(jié)點(diǎn)以下的CMOS晶片上的可能性不大;在PICs和規(guī)模微電子之間的片上鍵合相對(duì)簡(jiǎn)單的世界里,這樣做在經(jīng)濟(jì)或技術(shù)上都沒有意義。

EPIC的其他可能性也被廣泛探討。將光子添加到上一代CMOS工藝中會(huì)導(dǎo)致高功率、較慢的驅(qū)動(dòng)和TIA,從而導(dǎo)致更糟糕的收發(fā)器設(shè)計(jì),并使其對(duì)硅光子的最大客戶——數(shù)據(jù)通信和電信——沒有吸引力。盡管如此,這樣的過程對(duì)大學(xué)研究人員很有吸引力,因?yàn)樗鼮橐缘统杀竞头庋b努力共同設(shè)計(jì)和創(chuàng)新新的EPIC電路開辟了機(jī)會(huì)。另一方面,正在進(jìn)行多項(xiàng)努力,將雙極晶體管集成到與硅光子器件相同的晶片上。然而,到目前為止,這樣做依然涉及對(duì)雙極電子器件的性能的不可接受的妥協(xié)。

目前HVM中的大多數(shù)硅光子收發(fā)器都基于2.5D集成方法,其中PIC和EIC在其各自的最佳工藝中進(jìn)行設(shè)計(jì)、尺寸確定、優(yōu)化、測(cè)試,然后倒裝到中介層基板上(圖4b,表4)。EIC工藝可以從眾多CMOS/SiGe晶圓廠中選擇。多個(gè)EIC芯片也可以是倒裝芯片,例如(1)具有相當(dāng)大的擊穿電壓的SiGe芯片或縮放CMOS芯片,以允許高擺動(dòng)驅(qū)動(dòng)器和合理的開關(guān)速度來支持RF速度要求,以及(2)用于DSP/ADC/DAC的高級(jí)FinFET芯片。具有更快晶體管的EIC工藝甚至可以補(bǔ)償由于額外的焊盤、ESD和布線(與單片EPIC解決方案相比)而產(chǎn)生的寄生電容。對(duì)于大多數(shù)PIC組件需要相對(duì)較低速度的電子器件(如激光雷達(dá))的LSI應(yīng)用,倒裝芯片解決方案似乎是合理的。然而,對(duì)于需要許多高速驅(qū)動(dòng)/讀出線的LSI應(yīng)用,倒裝芯片解決方案意味著內(nèi)插器上有許多RF跡線,這導(dǎo)致了復(fù)雜性和串?dāng)_問題。在任何一種情況下,由于需要許多I/O凸塊,PIC的尺寸都會(huì)增加,盡管使用微凸塊和銅柱技術(shù),但這些增加在商業(yè)上通常可以忽略不計(jì)。在某些情況下,可以考慮混合3D集成,其中EIC在(較大的)PIC芯片上倒裝,并使用先進(jìn)的技術(shù),如硅通孔(TSV)(圖4c,表4)。RF線路仍然需要從小型EIC布線到PIC上的幾個(gè)地方,這仍然具有挑戰(zhàn)性。異構(gòu)3D集成也在研究中,在這種集成技術(shù)中,光子組件的性能有望得到進(jìn)一步改進(jìn)(圖4d,表4),其中一種可能性是使用集成在PIC上的多個(gè)EIC 3D。

總的來說,應(yīng)用、性能規(guī)格和發(fā)貨量(影響成本)將決定更昂貴的單片EPIC(具有更簡(jiǎn)單的封裝)、多芯片2.5D集成(具有更復(fù)雜的封裝)還是3D集成(具有更加復(fù)雜的處理/封裝)哪種是正確的選擇(表4)。我們預(yù)計(jì)所有這些場(chǎng)景都將共存,就像在電子生態(tài)系統(tǒng)中一樣。

4.硅光子技術(shù):應(yīng)用前景

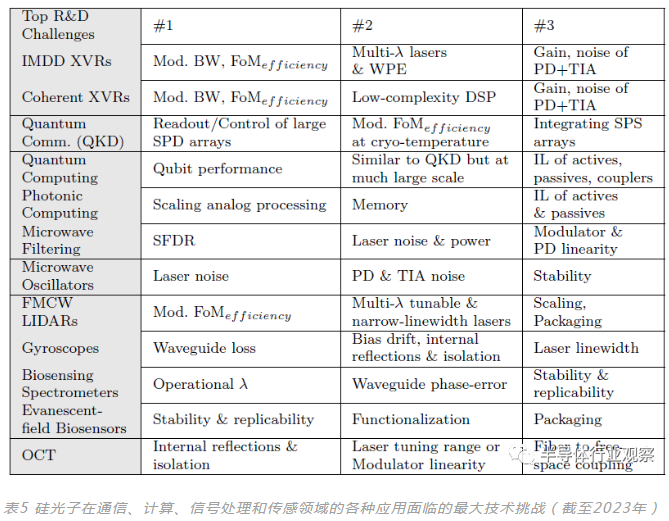

在本節(jié)中,我們描述了各種硅光子應(yīng)用成功的主要技術(shù)障礙(表5),將它們與前幾節(jié)中討論的一些挑戰(zhàn)和機(jī)遇聯(lián)系起來。我們僅限制PIC/EIC技術(shù)的障礙,不包括經(jīng)濟(jì)、監(jiān)管、市場(chǎng)和其他因素,如化學(xué)、生物標(biāo)志物、量子優(yōu)勢(shì)等。我們也沒有深入研究硅光子對(duì)這些應(yīng)用的好處,因?yàn)橹暗拇蠖鄶?shù)工作都對(duì)其進(jìn)行了詳細(xì)描述。

為了使IMDD收發(fā)器進(jìn)一步提高其能量效率(pJ/b)并擴(kuò)展到更高的數(shù)據(jù)速率,調(diào)制器FoMeefficiency需要進(jìn)一步降低,?3dB E/O BW需要提高到100 GHz。改進(jìn)激光器的WPE對(duì)于大多數(shù)應(yīng)用來說是必不可少的,但對(duì)于通信和計(jì)算應(yīng)用來說尤其重要。還需要在每個(gè)波長(zhǎng)中具有足夠大功率的高效多波長(zhǎng)光源。O/L/C頻帶中的低噪聲、大增益帶寬APD可以在沒有顯著功耗損失的情況下提供SNR改進(jìn),但從歷史上看,它們的帶寬、線性、噪聲和功率處理特性阻礙了它們?cè)谧罡邘捪碌氖褂谩W詈螅褂酶咴鲆妗⒌驮肼昑IA放大PD信號(hào)仍然是一個(gè)關(guān)鍵的挑戰(zhàn)。最近已經(jīng)證明了幾種基于均衡的技術(shù)可以使用低BW TIA來限制噪聲,但大多數(shù)技術(shù)都只是在接收機(jī)時(shí)鐘可用的假設(shè)下操作的。

為了使相干收發(fā)器在數(shù)據(jù)中心內(nèi)部具有競(jìng)爭(zhēng)力,必須解決額外的挑戰(zhàn)(相對(duì)于IMDD)。TIA和驅(qū)動(dòng)器的線性要求更加嚴(yán)格,需要盡可能減少對(duì)耗電DSP的依賴。研究人員正在探索的一種策略是利用集成光子和模擬電子電路將一些信號(hào)處理任務(wù)轉(zhuǎn)移到光學(xué)領(lǐng)域。后者需要大量的電子-光子協(xié)同設(shè)計(jì)工作,為CMOS設(shè)計(jì)者利用混合信號(hào)和RF IC的專業(yè)知識(shí)提供了機(jī)會(huì)。

實(shí)際的量子通信和計(jì)算應(yīng)用需要具有先進(jìn)CMOS控制器的LSI-VLSI光子組件。對(duì)于芯片級(jí)離散可變量子密鑰分布(QKD),最重要的要求是超導(dǎo)納米線單光子探測(cè)器(SPD)陣列的低溫兼容光子/電子讀出和控制;開發(fā)低損耗、低功率低溫調(diào)制器和低溫兼容WDM復(fù)用器/解復(fù)用器;以及在低噪聲、低串?dāng)_的芯片級(jí)光子電子解決方案中集成發(fā)射器處的單光子源(SPS)陣列。超導(dǎo)納米線SPD在電信波長(zhǎng)下工作,有助于將現(xiàn)有光纖用作量子通道。除了大規(guī)模并行化之外,減少接收機(jī)中的損耗和提高SPD性能將有助于提高傳輸速率。對(duì)于量子計(jì)算應(yīng)用,挑戰(zhàn)是相似的,但需要更大的量子位控制/讀出可擴(kuò)展性,包括光子學(xué)和低延遲控制電子器件。當(dāng)然,量子位的質(zhì)量是至關(guān)重要的。控制/讀取的可擴(kuò)展性隨著IL而降低——每損失一個(gè)光子都會(huì)以指數(shù)方式降低量子系統(tǒng)的能力。因此,需要超低損耗耦合器來連接到PIC。

光子計(jì)算涉及光子域中信息的模擬計(jì)算和處理。這需要處理多級(jí)信令并提高權(quán)重控制的精度,以保持足夠高的SNR,從而與現(xiàn)有的CMOS EIC計(jì)算引擎相比保持精度。訪問高速內(nèi)存以防止非重量固定的激活和任務(wù)出現(xiàn)內(nèi)存墻是另一個(gè)挑戰(zhàn)。光子計(jì)算采用高并行性,因此需要減少無源和有源器件(調(diào)制器、移相器)的IL,并提高多波長(zhǎng)激光器的輸出功率,以增加網(wǎng)絡(luò)規(guī)模。

對(duì)于汽車駕駛,硅光子激光雷達(dá)將自己定位為利用機(jī)械或基于MEMS的掃描的飛行時(shí)間(ToF)激光雷達(dá)的固態(tài)挑戰(zhàn)者。激光雷達(dá)由兩個(gè)子系統(tǒng)組成——測(cè)距和波束控制,這兩個(gè)子系統(tǒng)都可以使用硅光子技術(shù)。ToF和調(diào)頻連續(xù)波(FMCW)是測(cè)距技術(shù)。FMCW提供了以下優(yōu)點(diǎn):(1)相干檢測(cè)低至幾個(gè)光子的信號(hào),(2)對(duì)來自環(huán)境源的干擾的魯棒性,以及(3)同時(shí)進(jìn)行距離和速度測(cè)量。相干檢測(cè)的所有必要組件都可以集成在單個(gè)芯片上。對(duì)于波束控制,存在兩種集成的可能性:(1)基于連續(xù)可調(diào)諧移相器和光柵的光學(xué)相位陣列。體光學(xué)解決方案,如旋轉(zhuǎn)鏡和振蕩鏡,具有廉價(jià)、成熟和簡(jiǎn)單的優(yōu)點(diǎn);用片上OPA取代這樣的解決方案將是一個(gè)重大挑戰(zhàn)。為了使OPA發(fā)射單個(gè)波束,光柵天線的間距需要小于半個(gè)波長(zhǎng)(在自由空間中)——這對(duì)于硅芯片上的2D波束控制來說是一個(gè)具有挑戰(zhàn)性的命題。因此,硅光子OPA通常具有布置用于1D中的光束轉(zhuǎn)向的光柵,并且激光的波長(zhǎng)被掃過以將光束轉(zhuǎn)向另一個(gè)方向。(2) 基于片上開關(guān)網(wǎng)絡(luò)和光柵耦合器的焦平面陣列。其中包括需要MEMS開關(guān)的2D FPA,或具有波長(zhǎng)控制的1D FPA。無論解決方案如何,低功率(10s的nW)和改進(jìn)的FoMeefficiency移相器對(duì)于波束控制來說都是重要的和必要的。改進(jìn)激光是下一個(gè)挑戰(zhàn)。對(duì)于1D運(yùn)算放大器或FPA,多波長(zhǎng)激光器可以放松波長(zhǎng)調(diào)諧。對(duì)于FMCW解調(diào),窄線寬(<100kHz)連續(xù)可調(diào)諧激光器(優(yōu)選無模式跳變)至關(guān)重要。縮放和封裝是第三個(gè)挑戰(zhàn)。縮放許多發(fā)射器和移相器的光子學(xué)和電子器件,并為激光器和復(fù)雜的DSP集成相當(dāng)大的延遲(圖2,見補(bǔ)充),這兩者都是必要的。

微波光子的應(yīng)用(如濾波器和低相位噪聲振蕩器)與迄今為止討論的大多數(shù)其他應(yīng)用相比,具有不同的挑戰(zhàn)。用于微波濾波的無雜散動(dòng)態(tài)范圍(SFDR)規(guī)范在當(dāng)前一代硅光子中實(shí)現(xiàn)起來相當(dāng)具有挑戰(zhàn)性。調(diào)制器和PD需要嚴(yán)格的線性,同時(shí),必須將幾種噪聲源(激光、PD、TIA)降至最低。獲得RF凈增益的目標(biāo)使設(shè)計(jì)更加復(fù)雜。通過具有優(yōu)于僅CMOS對(duì)應(yīng)物的相位噪聲的硅光子實(shí)現(xiàn)激光輔助微波振蕩器還需要最小化激光噪聲、PD和TIA噪聲。還需要良好的短期和長(zhǎng)期穩(wěn)定性。

硅光子還可以用于低成本和緊湊設(shè)計(jì)的陀螺儀。但是,為了在性能上與基于光纖的同行競(jìng)爭(zhēng),利用Sagnac效應(yīng)的硅光子中的陀螺儀必須證明波導(dǎo)中的超低損耗(模仿光纖)、在振動(dòng)和溫度變化的極端條件下由于反射而導(dǎo)致的偏置漂移的減少(以不掩蓋Sagnac相移)以及高靈敏度的低噪聲。SiN波導(dǎo)的工程化已經(jīng)將損耗降低到0.5dB/m,還需要進(jìn)一步改進(jìn)。必須消除片上和片外的背反射,為此必須可靠地實(shí)現(xiàn)片上隔離器、反射消除電路或自注入鎖定。由于陀螺儀既不需要LSI實(shí)現(xiàn),也不需要高速調(diào)制器,因此如果解決了上述挑戰(zhàn),它將會(huì)是一種很有前途的定制應(yīng)用。它對(duì)振動(dòng)的魯棒性也要求異構(gòu)實(shí)現(xiàn),HVM必須解決其挑戰(zhàn)。

用于生物傳感應(yīng)用的硅光子光譜儀通常需要與C/L/O波段不兼容的工作波長(zhǎng)。這成為最重要的瓶頸,因?yàn)楸仨氃O(shè)計(jì)、測(cè)試和表征新的波導(dǎo)(相對(duì)于標(biāo)準(zhǔn)的220nm)和其他光子組件。激光器也是很具有挑戰(zhàn)性的,并且在這些非標(biāo)準(zhǔn)波長(zhǎng)下對(duì)寬波長(zhǎng)調(diào)諧或多波長(zhǎng)激光器的需求造成了嚴(yán)重的困難。最后,測(cè)量的穩(wěn)定性和可復(fù)制性對(duì)于生物傳感應(yīng)用至關(guān)重要,盡管存在環(huán)境漂移,但必須保持PIC和激光器的性能。

倏逝場(chǎng)生物傳感器的穩(wěn)定性和可復(fù)制性要求甚至更嚴(yán)格,因?yàn)閷?duì)血液或其他體液的侵入性測(cè)量增加了用戶對(duì)信任的期望。檢測(cè)的系統(tǒng)極限不僅取決于諧振器對(duì)溫度、激光噪聲、PD和TIA噪聲的響應(yīng),還取決于流體流動(dòng)、機(jī)械振動(dòng)和生物噪聲引起的噪聲。在氧化物開放步驟之后,諧振器表面的功能化在很大程度上取決于波導(dǎo)設(shè)計(jì)和親和力。生物傳感器的封裝和集成帶來了下一組挑戰(zhàn)。臺(tái)式機(jī)使用昂貴的可調(diào)諧激光器和納米定位器,但使用簡(jiǎn)單的無源PIC進(jìn)行生物傳感。另一方面,護(hù)理點(diǎn)設(shè)備必須緊湊、廉價(jià),并且需要使用低成本可調(diào)諧激光器或與PIC、EIC和流體學(xué)的其余部分集成的固定波長(zhǎng)激光器進(jìn)行操作。

目前用于視網(wǎng)膜成像的以硅光子為掃描源的光學(xué)相干斷層掃描(OCT)原型的靈敏度較差。首先,它們?cè)贠或C波段工作,而眼科OCT優(yōu)選在1050 nm處,以更深地穿透組織。移動(dòng)到1050nm將需要基于SiN的PIC和該波長(zhǎng)的可調(diào)諧激光源。最大限度地減少內(nèi)部反射并改善隔離將提高靈敏度。下一個(gè)障礙是激光源的調(diào)諧范圍和掃描速率有限,降低了圖像采集速率。最后,由于激光安全性的限制,激光功率不能太高。這反過來又需要PIC和成像光學(xué)器件之間幾乎無損的連接。

5.總結(jié)與結(jié)論

我們?cè)诠韫庾臃矫嫒〉昧司薮蟮娘w躍——從幾十年前才制造出第一個(gè)高限制波導(dǎo)和第一個(gè)調(diào)制器——到戰(zhàn)略性地利用CMOS行業(yè)的材料、集成和封裝技術(shù)成為收發(fā)器領(lǐng)域的主導(dǎo)技術(shù)。與此同時(shí),硅光子在很大程度上仍然是一項(xiàng)正在開發(fā)中的技術(shù),而一系列的可能性(本文僅描述了其中的一些)預(yù)示著未來的前景。未來十年將出現(xiàn)一些明顯的贏家,整合也將發(fā)生。盡管如此,應(yīng)用程序的多樣性將確保該技術(shù)有足夠的機(jī)會(huì)擴(kuò)大規(guī)模并廣泛傳播。

我們相信,在下一個(gè)十年,我們將看到以下可能實(shí)現(xiàn)的里程碑:

混合、異構(gòu)和單片集成將為大規(guī)模集成電路甚至超大規(guī)模集成電路實(shí)現(xiàn)提供具有必要密度、可配置性和可編程性的激光器、移相器、調(diào)制器和電子器件。這些集成技術(shù)中的每一種都有其優(yōu)點(diǎn),并且在可預(yù)見的未來都可能共存。

集成激光器和硅光子SOA將迅速發(fā)展。大多數(shù)晶圓廠將提供集成激光器,WPE超過20%。將支持多波長(zhǎng)激光器和可調(diào)諧激光器。

硅光子最終將從可插拔收發(fā)器轉(zhuǎn)向其他成功的商業(yè)產(chǎn)品,廣泛應(yīng)用于CPO和xPU應(yīng)用。使用插入器和小芯片架構(gòu)構(gòu)建的復(fù)雜系統(tǒng)將采用光子技術(shù)進(jìn)行互連。相干光子將進(jìn)一步發(fā)展——例如用于內(nèi)部通信(甚至數(shù)據(jù)中心內(nèi)部)、傳感(FMCW激光雷達(dá)、生物傳感)和計(jì)算。

基于等離子體色散的調(diào)制器將繼續(xù)充分用于許多WDM通信應(yīng)用,但與此同時(shí),Pockels調(diào)制器和移相器將在SOI CMOS工藝中商業(yè)化。LNOI將被引入硅光子工藝中,用于需要非常高速調(diào)制和低Vπ的應(yīng)用,盡管它們的尺寸較長(zhǎng)。

同樣,高效熱光加熱器不會(huì)在一夜之間推出。但是,對(duì)理想的低功耗移相器的追求將帶來一個(gè)真正能夠?qū)崿F(xiàn)LSI/VLSI應(yīng)用的解決方案。許多技術(shù)正在競(jìng)爭(zhēng),明顯的贏家尚未出現(xiàn)。

商用晶圓廠通常支持多層SiN和Si,并將針對(duì)這些SiN層優(yōu)化高性能無源元件(濾波器、延遲線)。

我們預(yù)計(jì)逆向設(shè)計(jì)的趨勢(shì)將開始產(chǎn)生更緊湊、更高性能和更堅(jiān)固的波導(dǎo)塊,這些波導(dǎo)塊將成為PDK不可或缺的一部分。同樣的技術(shù)也將提高超材料和超表面的性能。

光纖到PIC耦合的IL、帶寬和片上面積將不斷改善,典型的IL將會(huì)降至<0.5 dB。

我們還期待硅光子能夠擁有更完整的生態(tài)。將光子電路設(shè)計(jì)流程與EDA環(huán)境集成(或集成到EDA環(huán)境中)已經(jīng)開始,隨著電路變得更加復(fù)雜,光子和電子的協(xié)同設(shè)計(jì)將變得更加關(guān)鍵。光子電路的規(guī)模化和與電子學(xué)的融合也將帶來光子電路更大的可配置性和可編程性,降低構(gòu)建利用光物理用于新應(yīng)用的新系統(tǒng)的門檻。

太空時(shí)代催生了CMOS產(chǎn)業(yè),互聯(lián)網(wǎng)時(shí)代催生了光子產(chǎn)業(yè),而數(shù)據(jù)時(shí)代將為這兩者提供燃料。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<