本文綜合自:汽車ECU開發(fā)和賢哥幸福婚戀課公眾號(hào)

原文鏈接:https://mp.weixin.qq.com/s/uJtEXlGj8iok0MpuvOuB6w

https://mp.weixin.qq.com/s/t0gzi9rSJE6TonmFwW3s6w

1.RISC-V概述及歷史

RISC-V 起源于加州大學(xué)伯克利分校。在 2010 年夏季,Krste Asanovic 教授帶領(lǐng)他的兩個(gè)學(xué)生 Andrew Waterman 和 Yunsup Lee 啟動(dòng)了一個(gè)3個(gè)月的項(xiàng)目,目標(biāo)是針對(duì) x86 和ARM 指令集架構(gòu)復(fù)雜和需要IP 授權(quán)的問題,開發(fā)一個(gè)簡(jiǎn)化和開放的指令集架構(gòu)。RISC-V基金會(huì)創(chuàng)建于2015 年,是一家非營(yíng)利組織。基金會(huì)董事會(huì)最早由 Bluespec、Google、Microsemi、NVIDIA、NXP、UC Berkeley、Western Digital 七家單位組成,目前的主席是 Krste Asanovi 教授。

成員單位現(xiàn)在已經(jīng)比較多了:

基金會(huì)為核心芯片架構(gòu)制定標(biāo)準(zhǔn)和建立生態(tài),標(biāo)準(zhǔn)公開免費(fèi)下載。基金會(huì)旗下有超過 1 000 家成員,包括高通、NXP、阿里巴巴和華為等。RISC-V 基金會(huì)成員可以使用 RISC-V 商標(biāo)。RISC-V 指令集架構(gòu)采用開源BSD 授權(quán),任何企業(yè)、高校和個(gè)人都可以遵循RISC-V 架構(gòu)指南設(shè)計(jì)自己的 CPU.秉承開放、中立的宗旨,RISC-V 基金會(huì)總部從美國(guó)遷往瑞士,并于 2020年3月完成在瑞士的注冊(cè),更名為 RISC-V 國(guó)際基金會(huì)(RISC-V International Association)。近日,基金會(huì) CEO Calista Redmond 撰文 RISC-V Catalyst for ChangRISC-V,文章指出,RISC-V 標(biāo)準(zhǔn)是免費(fèi)和開放的,沒有任何一個(gè)實(shí)體可以控制RISC-V 技術(shù)。企業(yè)、學(xué)術(shù)界和機(jī)構(gòu)都可以自由地在 RISC-V 指令集架構(gòu)上進(jìn)行創(chuàng)新,共同推動(dòng)計(jì)算前沿技術(shù)的迅速發(fā)展。

自RISC-V 架構(gòu)誕生以來,市場(chǎng)上已有數(shù)十個(gè)版本的 RISC-V 內(nèi)核和SoC芯片它們中的一部分是開源免費(fèi)的,而商業(yè)公司開發(fā)的 RISC-V 處理器內(nèi)核和平臺(tái)是需要商業(yè)授權(quán)的。某些商業(yè)公司開發(fā)用于內(nèi)部使用的 RISC-V 內(nèi)核,但也可以開源運(yùn)作。西部數(shù)據(jù)的 SweRV架構(gòu)(RV32IMC)是 RISC-V內(nèi)核處理器的典型代表,它是一個(gè)32 bit 順序執(zhí)行指令架構(gòu),具有雙向超標(biāo)量設(shè)計(jì)和9 級(jí)流水線,采用 28 nm 工藝技術(shù)實(shí)現(xiàn),運(yùn)行頻率高達(dá) 1.8 GHz,可提供 4.9 CoreMark/MHz 的性能,略高于ARM的 Cortex A15,已經(jīng)在西部數(shù)據(jù)的 SSD和 HDD 控制器上使用,SweRV項(xiàng)目是一個(gè)開源項(xiàng)目(Chip Alliance)典型的開源 RISC-V 內(nèi)核有 Rocket Core,它是加州大學(xué)伯克利分校開發(fā)的一個(gè)經(jīng)典的 RV64 設(shè)計(jì)。伯克利分校還開發(fā)了一個(gè) BOOM Core,它與 Rocket Core不同的是面向更高的性能。蘇黎世理工大學(xué)(ETH Zurich)開發(fā)的 Zero-riscy,是經(jīng)典的RV32 設(shè)計(jì)。蘇黎世理工大學(xué)還開發(fā)了另外一款 RISC-V R15CY Core,可配置成RV32E,面向的是超低功耗、超小芯片面積的應(yīng)用場(chǎng)景。由 Clifford Wolf 開發(fā)的RISC-V Core-Pico RV32,其內(nèi)核重點(diǎn)在于追求面積和 CPU頻率的優(yōu)化。

開源的 RISC-V 內(nèi)核非常適用于研究和教學(xué),但用于商業(yè)芯片設(shè)計(jì)還有許多工作要做。SiFive(美國(guó)賽防科技)由 Yunsup Lee 創(chuàng)立,他也是 RISC-V 的創(chuàng)始人之一。2017 年 SiFive公司發(fā)布首個(gè) RISC-V 內(nèi)核SOC平臺(tái)家族,以及相關(guān)支持軟件和開發(fā)板。在這些芯片中,包括采用 28 nm 制造技術(shù),支持 Linux 操作系統(tǒng)的64位多核CPUU500,以及采用 180 nm 制造技術(shù)的多外設(shè)低成本IOT 處理器內(nèi)核 E300。

國(guó)產(chǎn)處理器芯片起步較晚,從2013年至今,集成電路每年的進(jìn)口額均超過了 2000 億美元。RISC-V和AI(人工智能)芯片是我國(guó)最有希望突破的領(lǐng)域之一。RISC-V使用的領(lǐng)域還是對(duì)于生態(tài)依賴比較小的嵌入式系統(tǒng)或者新興的IoT(物聯(lián)網(wǎng))、邊緣計(jì)算、人工智能領(lǐng)域,但RISC-V得到了產(chǎn)業(yè)界和社區(qū)的廣泛支持,同時(shí),現(xiàn)在很多企業(yè)開始對(duì) RISC-V 重視,所以說RISC-V 應(yīng)用前景會(huì)非常樂觀。

2. 什么是指令集,指令集與處理芯片之間有什么關(guān)系?RISC-V指令集的特點(diǎn)是什么?

處理器是一塊芯片。而芯片并不會(huì)自己工作,需要有人告訴它該做什么操作。例如告訴芯片下個(gè)操作做加法,這就是一條指令。

在人類社會(huì)中指令基本上是以語(yǔ)言或者聲音的形式存在,而在計(jì)算機(jī)系統(tǒng)中,指令是以二進(jìn)制數(shù)存在的。一個(gè)芯片指令的合集就叫指令集。指令集規(guī)定了二進(jìn)制數(shù)的格式、尋址方式、操作類型等。市面上常見的指令集有PC機(jī)常用的X86指令集、ARM的指令集等等。

一般來講,先有指令集,才會(huì)有芯片來支持指令集。所以指令集可以說是芯片的早期藍(lán)圖。指令集類似一種標(biāo)準(zhǔn),定義了芯片支持的功能。而芯片是一個(gè)實(shí)物,實(shí)現(xiàn)指令集定義的功能。所以你常聽的RISC-V處理器,實(shí)際上是支持了RISC-V指令集的處理器芯片。

CPU 支持的所有指令和指令的字節(jié)級(jí)編碼就是這個(gè) CPU 的指令集架構(gòu)(Instruction Set Architecture,ISA),指令集在計(jì)算機(jī)軟件和硬件之間搭起了一座橋梁。不同的 CPU 家族,例如 86、PowerPC 和 ARM,都有不同的 ISA。RISC-VISA 開源,更確切地講是它的指令集規(guī)范和標(biāo)準(zhǔn)開源。

RISC-V指令集是基于精簡(jiǎn)指令集計(jì)算原理建立的開放指令集架構(gòu)(ISA),RISC-V是在指令集不斷發(fā)展和成熟的基礎(chǔ)上建立的全新指令。RISC-V ISA可以免費(fèi)使用,允許任何人設(shè)計(jì)、制造和銷售 RISC-V 芯片和軟件。

RISC-V(讀音“risk-five”)是一個(gè)新的指令集體系結(jié)構(gòu)(ISA),它最初用于支持計(jì)算機(jī) 體系結(jié)構(gòu)研究和教學(xué),但現(xiàn)在我們希望它也成為一個(gè)對(duì)于工業(yè)實(shí)現(xiàn)來說標(biāo)準(zhǔn)、免費(fèi)、開放的 體系結(jié)構(gòu)。RISC-V官方定義 RISC-V 的目的包括:

一個(gè)完全開放的 ISA,能夠自由地提供給學(xué)術(shù)界和工業(yè)界使用。

一個(gè)真正的 ISA,能夠適合直接在硬件上實(shí)現(xiàn),而不僅僅是適用于模擬或者二進(jìn)制 翻譯。

一個(gè)避免對(duì)某一種微體系結(jié)構(gòu)風(fēng)格(例如微編碼、按序、去耦合、亂序等)或者實(shí) 現(xiàn)技術(shù)(例如全定制、ASIC、FPGA)“過度體系結(jié)構(gòu)化(over-architecting)”的 ISA, 但是也能夠非常高效地利用任何一種技術(shù)實(shí)現(xiàn)。

包含一個(gè)小的基本整數(shù) ISA(可以作為一個(gè)定制的加速器的基礎(chǔ)或者作為教學(xué)用途) 和多個(gè)可選的標(biāo)準(zhǔn)擴(kuò)展的 ISA,可以支持通用的軟件開發(fā)。

支持修訂的 2008 IEEE-754浮點(diǎn)標(biāo)準(zhǔn)。

ISA 支持豐富的用戶級(jí) ISA 擴(kuò)展和各種特殊的變種。

對(duì)應(yīng)用程序、操作系統(tǒng)內(nèi)核、硬件實(shí)現(xiàn)的32 位、64 位地址空間變種。

ISA 支持高度并行的多核、眾核實(shí)現(xiàn),包括異構(gòu)多處理器等。

可選的變長(zhǎng)指令,以支持?jǐn)U展可用的指令編碼空間、支持一個(gè)可選的密集指令編碼, 以提高性能、靜態(tài)代碼大小和能耗效率。

一個(gè)可完全虛擬化的 ISA,以簡(jiǎn)化虛擬機(jī)監(jiān)督管理器(Hypervisor)的開發(fā)。

ISA 支持新的管理員級(jí)(supervisor-level)和虛擬機(jī)監(jiān)督管理級(jí)(hypervisor-level) ISA 設(shè)計(jì)。

3.關(guān)于RISC-V的V

RISC-V 這個(gè)名字,代表了 UC Berkeley 大學(xué)設(shè)計(jì)的第五代主要的 RISC ISA(前 四個(gè)是 RISC-I[18]、RISC-II[11]、SOAR[27]和 SPUR[14])。羅馬數(shù)字“V”也暗示 了“變種(Variations)”和“向量(Vectors)”,以支持各種體系結(jié)構(gòu)研究,包括各種數(shù)據(jù)并行加速器,也是這個(gè) ISA 設(shè)計(jì)的明確目標(biāo)。

4、發(fā)明者為什么要開發(fā)一個(gè)新的ISA

關(guān)于為什么要有RISC-V,發(fā)明者這么說:

硬件上實(shí)現(xiàn)一些研究思想特別感興趣(自從這個(gè)規(guī)范的第一個(gè)版本發(fā)布之后, 我們已經(jīng)完成了 11 塊不同的 RISC-V 硅片的制造),在課堂上提供給學(xué)生真實(shí) 的實(shí)現(xiàn)(在 Berkeley,RISC-V 處理器的 RTL 設(shè)計(jì)代碼已經(jīng)用于多個(gè)本科生、研 究生的課程)。在我們當(dāng)前的研究中,由于傳統(tǒng)晶體管不斷變小帶來的能耗約 束,我們對(duì)特殊、異構(gòu)的加速器特別感興趣。我們需要一個(gè)高度靈活、高度可 擴(kuò)展的基本 ISA,在此基礎(chǔ)上可以構(gòu)建我們自己的研究。

我們總被問及這樣一個(gè)問題“為什么要開發(fā)一個(gè)新的 ISA?”。使用一個(gè)已 有的商業(yè)化的 ISA,其顯而易見最大的優(yōu)勢(shì)在于其已經(jīng)具備了豐富和廣泛支持。

的軟件生態(tài)系統(tǒng),包括開發(fā)工具和可移植的應(yīng)用程序,而在研究和教學(xué)中,這 些都是可以利用的。其他的好處包括擁有大量的文檔和教程示例。然而,我們 的經(jīng)驗(yàn)證明,在科研和教學(xué)中使用商業(yè)的指令集,在實(shí)際中獲得的好處很小, 而且掩蓋不了它的缺點(diǎn):

商業(yè) ISA 都是私有的。除了 SPARC V8(它是一個(gè)開放的IEEE 標(biāo)準(zhǔn)[1]), 絕大多數(shù) ISA 的擁有者非常小心地保護(hù)他們的知識(shí)產(chǎn)權(quán),并且并不歡 迎自由實(shí)現(xiàn)的競(jìng)爭(zhēng)實(shí)現(xiàn)。對(duì)于僅僅使用軟件模擬器來進(jìn)行學(xué)術(shù)研究和 教學(xué)來說,這并不是一個(gè)問題,但是對(duì)于那些希望分享真實(shí)硬件實(shí)現(xiàn) 的科研小組來說,這就是一個(gè)大問題。對(duì)于那些被強(qiáng)迫信任僅有的幾 個(gè)商業(yè) ISA 實(shí)現(xiàn),而不允許創(chuàng)建自己的全新實(shí)現(xiàn)(clean room implementation)的企業(yè)來說,這也是一個(gè)大問題。我們并不能確保 所有的 RISC-V 實(shí)現(xiàn)沒有侵犯第三方專利,但是我們確保我們絕不會(huì) 起訴一個(gè) RISC-V 的實(shí)現(xiàn)者。

(1)商業(yè) ISA 僅僅在某個(gè)市場(chǎng)領(lǐng)域比較流行。當(dāng)書寫此文檔時(shí),最顯而易 見的例子就是 ARM 體系結(jié)構(gòu)在服務(wù)器領(lǐng)域并沒有得到很好的支持, 而 Intel x86 體系結(jié)構(gòu)(或者幾乎任何一種其他的體系結(jié)構(gòu))在移動(dòng)領(lǐng) 域并沒有得到很好的支持,雖然 Intel 和 ARM 正在試圖進(jìn)入對(duì)方的市 場(chǎng)領(lǐng)域。另外一個(gè)例子是 ARC 和 Tensilica,它們提供了可擴(kuò)展的內(nèi)核, 但是只關(guān)注嵌入式市場(chǎng)。這種市場(chǎng)的劃分,使得支持某種特定商業(yè) ISA 獲得的好處大大削弱,因?yàn)槭聦?shí)上軟件生態(tài)系統(tǒng)只存在于某個(gè)領(lǐng) 域,到了別的領(lǐng)域,必須重新構(gòu)建。

(2)商業(yè) ISA 此起彼伏。以前基于商業(yè) ISA 構(gòu)建的研究基礎(chǔ)設(shè)施,并不流 行(SPARC、MIPS),甚至不再生產(chǎn)(Alpha)。這對(duì)于一個(gè)活躍的軟件 生態(tài)系統(tǒng)來說是一個(gè)大損失,一些圍繞 ISA 和支持工具的知識(shí)產(chǎn)權(quán)問 題,也使得感興趣的第三方難以繼續(xù)支持這個(gè) ISA。一個(gè)開放的 ISA 也可能失去流行性,但是任何感興趣的人,都可以繼續(xù)使用它并研發(fā) 相應(yīng)的生態(tài)系統(tǒng)。

(3)流行的商業(yè) ISA 是復(fù)雜的。占統(tǒng)治地位的 ISA(x86 和 ARM)若要支 持常用軟件棧和操作系統(tǒng),那么其硬件實(shí)現(xiàn)都非常復(fù)雜。更糟糕的是, 幾乎所有的復(fù)雜性都來自于糟糕的、或者至少是過時(shí)的ISA設(shè)計(jì)考慮, 而不是那些真正提高效率的特性。

(4)僅靠商業(yè) ISA 并不足以運(yùn)行應(yīng)用程序。即使我們努力實(shí)現(xiàn)了一個(gè)商業(yè) ISA,對(duì)于運(yùn)行一個(gè)現(xiàn)有的應(yīng)用程序來說,仍然是不夠的。絕大多數(shù) 應(yīng)用程序需要一個(gè)完整的 ABI(application binary interface)才能運(yùn)行, 而不僅僅是用戶級(jí) ISA。絕大多數(shù) ABI 依賴于庫(kù)(libraries),而庫(kù)又 依賴于操作系統(tǒng)支持。為了運(yùn)行一個(gè)已有的操作系統(tǒng),需要實(shí)現(xiàn)管理 員級(jí) ISA、OS 需要的設(shè)備接口。這些通常并沒有很好的規(guī)范,而在實(shí) 現(xiàn)上比用戶級(jí) ISA 具有更大的復(fù)雜性。

(5)流行的商業(yè) ISA 不是為可擴(kuò)展性設(shè)計(jì)的。占統(tǒng)治地位的商業(yè) ISA 并沒 有為可擴(kuò)展性而進(jìn)行特殊的設(shè)計(jì),結(jié)果就是,隨著后續(xù)指令集不斷地 增長(zhǎng),指令編碼的復(fù)雜度大幅度增加。而類似 Tensilica(被 Cadence 公司收購(gòu))、ARC(被 Synopsys 公司收購(gòu))這樣的公司,它們圍繞 可擴(kuò)展性構(gòu)建了 ISA 和工具鏈(toolchain),但是它們瞄準(zhǔn)的是嵌入 式應(yīng)用而不是通用計(jì)算系統(tǒng)。

一個(gè)修改過的商業(yè) ISA 實(shí)際上是一個(gè)新的 ISA。我們的一個(gè)主要目標(biāo) 是支持體系結(jié)構(gòu)研究,包括主要的 ISA 擴(kuò)展。即使是很小的擴(kuò)展,也 減弱了使用標(biāo)準(zhǔn) ISA 而帶來的好處,因?yàn)楸仨毿薷木幾g器,而應(yīng)用程 序必須從源代碼進(jìn)行重新編譯,以利用這些擴(kuò)展。引入了新的體系結(jié) 構(gòu)狀態(tài)的大一些的擴(kuò)展,也需要對(duì)操作系統(tǒng)進(jìn)行修改。最終使得一個(gè) 修改的商業(yè) ISA 變成一個(gè)新的 ISA,但是不得不肩負(fù)著所有基本 ISA 遺留下來的包袱。我們堅(jiān)信 ISA 是整個(gè)計(jì)算系統(tǒng)中最重要的接口,沒有理由把這么重要的接 口變成私有的。占統(tǒng)治地位的商業(yè) ISA 都是基于超過 30 年歷史的指令集。軟 件開發(fā)者應(yīng)當(dāng)能夠定位到一個(gè)開放標(biāo)準(zhǔn)的硬件目標(biāo)機(jī),商業(yè)處理器設(shè)計(jì)者應(yīng)當(dāng) 在實(shí)現(xiàn)質(zhì)量上進(jìn)行競(jìng)爭(zhēng)。我們并不是第一個(gè)為了適合硬件實(shí)現(xiàn)而提出開放 ISA 設(shè)計(jì)的。我們也考慮 了其他現(xiàn)有的開放 ISA 設(shè)計(jì),其中 OpenRISC 體系結(jié)構(gòu)[17]與我們的目標(biāo)最為 接近。

我們由于幾個(gè)技術(shù)原因,并不采用 OpenRISC ISA:

1、OpenRISC 有條件碼(condition code)和分支延遲槽(branch delay slot), 這對(duì)于更高性能的實(shí)現(xiàn)來說,變得更為復(fù)雜。

2、OpenRISC 使用了 32 位定長(zhǎng)指令編碼和 16 位立即數(shù),阻礙了更密集 的指令編碼,并對(duì)后續(xù) ISA 擴(kuò)展限制了空間。

3、OpenRISC 并不支持 2008 修訂的 IEEE-754 浮點(diǎn)標(biāo)準(zhǔn)。

在我們開始的時(shí)候,64 位 OpenRISC 設(shè)計(jì)并沒有完成。從零開始,我們可以設(shè)計(jì)一個(gè)符合我們所有需求的 ISA,當(dāng)然,這花了比 我們?cè)陂_始時(shí)預(yù)期多得多的努力。現(xiàn)在我們?cè)跇?gòu)建 RISC-V ISA 基礎(chǔ)設(shè)施上投入 了大量的精力,包括文檔、編譯器工具鏈、操作系統(tǒng)移植、參考 ISA 模擬器、 FPGA 實(shí)現(xiàn)、高效的 ASIC 實(shí)現(xiàn)、體系結(jié)構(gòu)測(cè)試套件、教學(xué)材料等。自本文檔的 上一個(gè)版本以來,在學(xué)術(shù)界和工業(yè)界對(duì)此 RISC-V ISA 都有大量的吸收(uptake), 我們也創(chuàng)建了非盈利的 RISC-V 基金會(huì)來保護(hù)和推進(jìn)這個(gè)標(biāo)準(zhǔn)。RISC-V 基金會(huì)的 網(wǎng)址在 http://riscv.org,包含了基金會(huì)成員最新的信息和各種各樣使用 RISC-V 的開源項(xiàng)目。

5.RISC-V指令集的優(yōu)勢(shì)

(1)完全開源。對(duì)于 RISC-V 指令集的使用,RISC-V基金會(huì)不收取高額的授權(quán)費(fèi)。開源采用寬松的BSD 協(xié)議,企業(yè)可以完全自由免費(fèi)使用,同時(shí)也允許企業(yè)添加自有指令集,而不必開放共享,實(shí)現(xiàn)差異化發(fā)展。

(2)架構(gòu)簡(jiǎn)單。RISC-V設(shè)。處理器領(lǐng)域,流的架構(gòu)為x8與ARM架構(gòu)。x86與ARM架構(gòu)的發(fā)展過程也伴隨了現(xiàn)代處理器架構(gòu)技術(shù)的不斷發(fā)展成熟,但作為商用的架構(gòu),為了能夠保持架構(gòu)的向后兼容性,不得不保留許多過時(shí)的定義,導(dǎo)致其指令數(shù)目多,指令冗余嚴(yán)重,文檔數(shù)量龐大,所以要在這些架構(gòu)上開發(fā)新的操作系統(tǒng)或者直接開發(fā)應(yīng)用門檻很高。而RISC-V 架構(gòu)則完全拋棄包袱,借助計(jì)算機(jī)體系結(jié)構(gòu)經(jīng)過多年的發(fā)展已經(jīng)成為比較成熟的技術(shù)的優(yōu)勢(shì),從輕上路。RISC-V基礎(chǔ)指令集只有40多條,加上其他的模塊化擴(kuò)展指令總共也就幾十條指令。RISC-V的規(guī)范文檔僅有145頁(yè),而特權(quán)架構(gòu)文檔的篇幅也僅為 91頁(yè)。

(3)易于移植操作系統(tǒng)。現(xiàn)代操作系統(tǒng)都做了特權(quán)級(jí)指令和用戶級(jí)指令的分離,特權(quán)指今只能由操作系統(tǒng)調(diào)用,而用戶級(jí)指令才能在用戶模式調(diào)用,保障操作系統(tǒng)的穩(wěn)定。RISC-V提供了特權(quán)級(jí)指令和用戶級(jí)指令,同時(shí)提供了詳細(xì)的 RISC-V 特權(quán)級(jí)指令規(guī)范和 RISC-V 用戶級(jí)指令規(guī)范的詳細(xì)信息,使開發(fā)者能非常方便地移植 Linux 和 UNIX 系統(tǒng)到RISC-V平臺(tái)上。

(4)模塊化設(shè)計(jì)。RISC-V 架構(gòu)不僅短小精悍,其不同的部分還能以模塊化的方式組紗在一起,從而試圖通過一套統(tǒng)一的架構(gòu)滿足各種不同的應(yīng)用場(chǎng)景。用戶能夠靈活選擇不同的模塊組合,來實(shí)現(xiàn)自己定制化設(shè)備的需要,比如針對(duì)小面積低功耗嵌入式場(chǎng)景,用戶可以選擇RV32IC 組合的指令集,僅使用Machine Mode(機(jī)器模式);而高性能應(yīng)用操作系統(tǒng)場(chǎng)景則可以選擇RV32IMFDC 指令集,使用 Machine Mode(機(jī)器模式)與User Mode()戶模式)兩種模式。

(5)完整的工具鏈。對(duì)于設(shè)計(jì)CPU 來說,工具鏈?zhǔn)擒浖_發(fā)人員和 CPU 交互的窗口,若沒有工具鏈,則對(duì)軟件開發(fā)人員開發(fā)軟件要求很高,甚至軟件開發(fā)者無法讓CPU 工作起來在CPU 設(shè)計(jì)中,工具鏈的開發(fā)是一個(gè)巨大的工作。如果用RISC-V來設(shè)計(jì)芯片,芯片設(shè)計(jì)公司則不用再擔(dān)心工具鏈問題,只需專注于芯片設(shè)計(jì),RISC-V社區(qū)已經(jīng)提供了完整的工具鏈 RISC-V 基金會(huì)持續(xù)維護(hù)該工具鏈。當(dāng)前RISC-V的支持已經(jīng)合并到主要的工具中,比如編評(píng)工具鏈 GCC、仿真工具 QEMU 等。

6、RISC-V的特點(diǎn)

1)沒有立即數(shù)減法

只有立即數(shù)加法指令(addi),沒有立即數(shù)減法指令(subi),那么減法怎么辦?無論是數(shù)學(xué)上還是程序上,x-y都等價(jià)于x+(-y),也就是說可以把減法變成加法,把被減數(shù)轉(zhuǎn)化成負(fù)數(shù)然后再加上減數(shù)就實(shí)現(xiàn)了和減法一樣的功能。正是基于這個(gè)原理,RISC-V只提供立即數(shù)加法,沒有提供立即數(shù)減法,如果需要立即數(shù)減法,那么就要麻煩編譯器把這個(gè)立即數(shù)轉(zhuǎn)化成負(fù)數(shù),然后繼續(xù)使用加法。這也是 RISC-V將立即數(shù)作為有符號(hào)數(shù)處理的原因。

2)x0 寄存器簡(jiǎn)化指令集

引入x0 寄存器后,很多特殊指令只需用普通的指令加上 x0 做操作數(shù)就能解決,指令的數(shù)量大大減少,處理器的解碼電路也大大簡(jiǎn)化。

3)32 位常量

之前使用的ARM 處理器是將立即數(shù)表示不下的常量存到常量池,然后用PC相關(guān)的LDR指令加載到寄存器。RISC-V 的常量完全是用指令拼接,不需要 Load 指令,使用 Load 指令需要額外的訪問周期。RISC-V 單條指令可以表示 12 位的有符號(hào)常量,超過 12 位需要兩條指令來合成。其中一條指令是 lui,lui 指令加載常量的高 20 位,低 12 位可以用addi指令上去,這個(gè)過程需要編譯器算出立即數(shù)到底是什么,因?yàn)?addi 指令執(zhí)行的是有符號(hào)加法,其中的 12 位立即數(shù)會(huì)先被符號(hào)擴(kuò)展成 32 位的有符號(hào)數(shù)再參與計(jì)算。ARM 的常量加載需要8個(gè)字節(jié),一條指令加一個(gè)常量;RISC-V的常量加載也是需要8個(gè)字節(jié),兩條指令,兩者占用的程序空間一樣。

4)只有小于和大于等于

RISC-V 的比較跳轉(zhuǎn)指令只有 blt 和 bge,即只有小于和大于等于。但大于和小于等于也是需要的,RISC-V用了一個(gè)很巧妙的辦法用兩條指令實(shí)現(xiàn)了四條指令的工作,將 blt 的兩個(gè)參與比較的操作數(shù)位置換一下就有了 bgt(大于跳轉(zhuǎn)),將bge 的兩個(gè)參與比較的操作數(shù)位置換一下就有了 ble(小于或等于跳轉(zhuǎn))。

5)讓編譯器做更多工作

對(duì) RISC 的理解是處理器盡量少做、編譯器盡量多做,這是非常有道理的,畢竟編譯的次數(shù)遠(yuǎn)少于執(zhí)行的次數(shù)。上面幾點(diǎn)就提到不少要讓編譯器多做的工作,又例如 B-type 是比較跳轉(zhuǎn)指令的格式,J-type 是長(zhǎng)跳轉(zhuǎn)或函數(shù)調(diào)用指令格式,注意它們的立即數(shù)排列次序,把填充這里的立即數(shù)交給了鏈接器的工作。這樣排放偏移地址立即數(shù)是為了簡(jiǎn)化處理器的設(shè)計(jì),但明顯給編譯器增加了工作。

6)其他省掉的指令

很多常用的指令都被省掉了,比如nop、move、not、neg 等,但所有這些功能都還有只不過都是用其他的指令來等價(jià)實(shí)現(xiàn),比如not 指令是用xorird,rs,-1實(shí)現(xiàn)。

7、RISC-V的x0寄存器

Linux 有兩個(gè)特殊的設(shè)備:/dev/zero 和/dev/null。從/dev/zero 可以源源不斷地讀到0,往dev/null 寫的任何內(nèi)容都被丟棄。如果要?jiǎng)?chuàng)建一個(gè)需要填0的文件,就從dev/zero 拷貝,如果要丟棄一些輸出,就把輸出重定向到/dev/null。RISC-V的x0寄存器就相當(dāng)于是硬件版的/dev/zero 和/dev/null的組合體。從0讀出來的總是0,往x0 寫進(jìn)去的總是被丟棄。所以 x0 提供兩種功能:一是提供常量0,在軟件編程中0可以說是最常用的常量:二是提供一個(gè)可以丟棄結(jié)果的場(chǎng)所。有了 x0 寄存器,很多本來需要單獨(dú)指令的操作只要在普通的指令前加上x0 就可以實(shí)現(xiàn)。

(1)nop 空指令,RISC-V沒有提供nop 指令,而是用addi x0,x0,0來實(shí)現(xiàn)空指令,這條addi 使用x0作為目標(biāo)存器,會(huì)丟棄結(jié)果,所以這條指令不會(huì)對(duì)程序狀態(tài)產(chǎn)生任何影響,和空指令是完全等價(jià)的,這就不需要單獨(dú)的空指令了。

(2)neg 取負(fù)數(shù)指令,RISC-V用 sub rd,x0,rs 來實(shí)現(xiàn),x0-rs 等價(jià)于0-rs,等價(jià)于-rs,有了x0,就可以用更普通的減法指令來實(shí)現(xiàn)取負(fù)數(shù)指令。

(3)j跳轉(zhuǎn)指令,RISC-V 沒有單獨(dú)的跳轉(zhuǎn)指令,只有jal跳轉(zhuǎn)鏈接指令,跳轉(zhuǎn)之前總是要把下一條指令的地址拷貝到寄存器,但是如果用 x0 作為jal 的操作寄存器,即把下-條指令的地址拷貝到 x0,那么效果就等價(jià)于j跳轉(zhuǎn)指令了,因?yàn)閷懭?x0 的任何值都會(huì)被丟棄。

(4)beqz等于零跳轉(zhuǎn)指令等一系列和0比較的跳轉(zhuǎn)指令,程序中和0比較是相當(dāng)常見的操作,RISC-V 中和0比較的指令是普通的比較跳轉(zhuǎn)指令,是用 x0 寄存器做指令的操作數(shù)。還有很多其他這樣的指令,用普通的指令加上 x0 做操作數(shù),就實(shí)現(xiàn)了那些沒有x0 寄存器的處理器需要單獨(dú)指令或者需要組合兩條指令才能實(shí)現(xiàn)的操作。

8. 為什么RISC-V在國(guó)內(nèi)如此受關(guān)注?

RISC-V作為較新的指令集,技術(shù)上是有一定的優(yōu)勢(shì),其實(shí)最大的原因是這個(gè)指令集是開源免費(fèi)的,基于這套指令集設(shè)計(jì)的芯片無論用于科研和商業(yè)均無需給Intel和ARM上稅。目前市面上常見的指令集都是要收費(fèi)的,例如華為麒麟芯片,就購(gòu)買了ARM家的指令集。這些有指令集知識(shí)產(chǎn)權(quán)的公司均為國(guó)外公司,非常不利于我國(guó)實(shí)現(xiàn)關(guān)鍵芯片的自主可控。

目前,國(guó)內(nèi)外已經(jīng)有非常多的RISC-V核心RTL代碼,好多是開源的,如果你感興趣可以下載一個(gè)研究研究。如果用于商用,國(guó)內(nèi)外也有許多商業(yè)公司提供穩(wěn)定的RISC-V IP核心。例如國(guó)外的SiFive公司、Microsemi公司、國(guó)內(nèi)的阿里平頭哥、芯來科技等公司。

9.RISC-V的核心是如何與AI加速核心集成的?

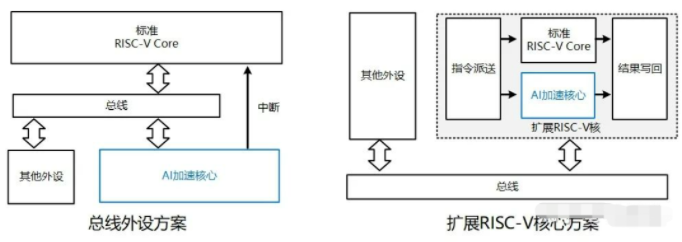

從整體實(shí)現(xiàn)方式上來講,共有兩種方式可以實(shí)現(xiàn)AI加速核心與RISC-V計(jì)算核心的集成。

方法一是總線外設(shè)方案,該方案可以直接把AI加速核心當(dāng)作一個(gè)總線高速外設(shè)掛載于SOC系統(tǒng)。

方案二是RISC-V指令集獨(dú)有的辦法,擴(kuò)展RISC-V核心方案。利用RISC-V指令集可擴(kuò)展的特性,添加專門的AI指令,在設(shè)計(jì)微內(nèi)核時(shí)加入一個(gè)指令派送單元,將AI加速指令直接派送給AI加速核心。

實(shí)際上,由于神經(jīng)網(wǎng)絡(luò)計(jì)算的過程中幾乎不需要條件判斷等操作,規(guī)律的乘加操作占據(jù)大多數(shù)運(yùn)行時(shí)間,兩種實(shí)現(xiàn)方案并無本質(zhì)差別。

擴(kuò)展RISC-V核心的方案優(yōu)勢(shì)在于當(dāng)總線外設(shè)較多時(shí),共用了微內(nèi)核資源,減少了總線開銷。而擴(kuò)展RISC-V核心方案的缺點(diǎn)是對(duì)RISC-V編譯工具鏈要做少許修改,增加額外的工作量。