隨著摩爾定律的逐步失效,數(shù)字邏輯芯片和DRAM芯片隨著制程工藝提升所帶來的密度優(yōu)勢正在降低,成本卻在高速提升。相比之下,NAND Flash閃存的情況卻并非如此。與半導(dǎo)體行業(yè)的其他行業(yè)不同,NAND每年的成本都在大幅下降。

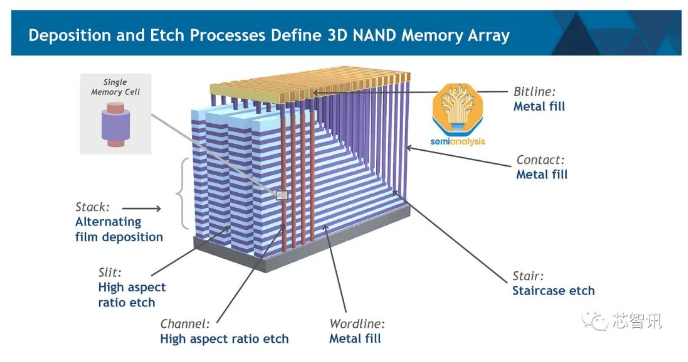

這主要是因?yàn)镹AND顛覆了摩爾定律,不再依賴對于晶體管的微縮。相反,NAND轉(zhuǎn)向了全新的3D NAND架構(gòu),并于2013年首次商業(yè)化。從那時(shí)起,NAND制造商通過添加越來越多的存儲(chǔ)單元層的堆疊來提高NAND的密度和成本結(jié)構(gòu)。制造的焦點(diǎn)也幾乎完全從光刻轉(zhuǎn)移到了沉積和蝕刻處理步驟。結(jié)果,自從引入3D NAND以來,NAND的密度以非常一致的速度每年提高30%。

近日,半導(dǎo)體研究機(jī)構(gòu)Semianalysis發(fā)布文章,對NAND半導(dǎo)體市場、工藝技術(shù)擴(kuò)展途徑、制造工藝、NAND定價(jià)趨勢、當(dāng)前供過于求/未來短缺、2023年至2025年NAND晶圓制造設(shè)備支出前景、西部數(shù)據(jù)和Kioxia的未來進(jìn)行了分析,并深入探討了NAND高縱橫比蝕刻市場、3D DRAM的可能性。Semianalysis認(rèn)為,沉積方面也即將發(fā)生的重大材料變化,以及由于兩次制造變化,代表超過10億美元的收入可能易手,市場份額可能從泛林集團(tuán)(Lam Research)大幅轉(zhuǎn)移到東京電子(TEL)。

一如既往,技術(shù)背景將為每個(gè)人詳細(xì)介紹。NAND的沉積和蝕刻、3D DRAM的可能性、業(yè)務(wù)影響、變化、高層成果和WDC/Kioxia評論方面的兩項(xiàng)新發(fā)展也將詳細(xì)介紹。包括從超大規(guī)模集成電路日本和半導(dǎo)體西部的工具公司和NAND制造商那里收集的市場情報(bào)。

自引入3D NAND以來,這種密度的增加使每比特的NAND成本每年下降約21%,盡管未來可能會(huì)面臨一些挑戰(zhàn),但預(yù)計(jì)仍將繼續(xù)擴(kuò)展。

美光認(rèn)為,NAND每比特的成本可以繼續(xù)以每年低至百分之十幾的速度下降,而DRAM更難擴(kuò)展,只能以每年高個(gè)位數(shù)的成本下降為目標(biāo)。這是DRAM行業(yè)最近經(jīng)歷的21%的倒退。

NAND中這些大規(guī)模成本改進(jìn)的主要原因是晶圓廠可以在工藝步驟數(shù)沒有大規(guī)模相應(yīng)增加的情況下增加密度。3D NAND中最關(guān)鍵的步驟是薄膜沉積和高縱橫比蝕刻。

NAND的一個(gè)過于簡單的制造過程是沉積交替的薄膜,然后有一些不同的蝕刻穿過堆疊,將cell分開/連接到外部世界。Lam Research是許多工藝步驟的領(lǐng)導(dǎo)者,包括最關(guān)鍵的高縱橫比蝕刻。

NAND擴(kuò)展的四條大道

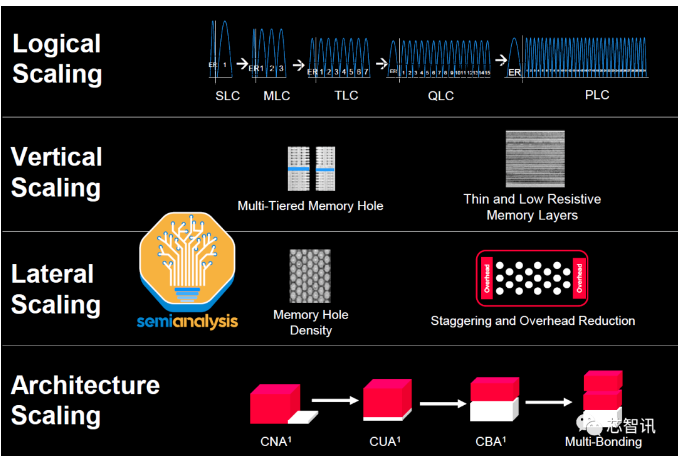

有4種主要途徑可以擴(kuò)展NAND閃存每片的存儲(chǔ)容量。

邏輯縮放:每個(gè)單元存儲(chǔ)的位數(shù)。這需要每個(gè)單元存儲(chǔ)2^n個(gè)電壓電平;

垂直縮放:垂直堆疊的NAND單元的數(shù)量;

橫向縮放:可以在2D矢量上擬合的單元格的大小/數(shù)量;

體系結(jié)構(gòu)擴(kuò)展:各種技術(shù)可提高密度并減少單元/外圍的開銷。

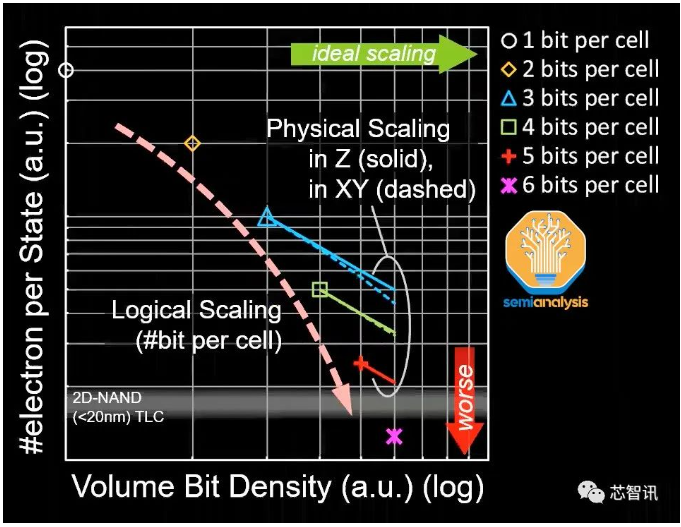

首先是邏輯縮放,即每個(gè)物理存儲(chǔ)單元存儲(chǔ)更多的位。每個(gè)單元存儲(chǔ)的每個(gè)附加位需要將單元必須保持的可辨別電壓狀態(tài)的數(shù)量增加一倍。IE:每個(gè)單元1bit(SLC)的2個(gè)電壓電平,每個(gè)單元2bit(MLC)的4個(gè)電壓電平、每個(gè)單元3bit(TLC)的8個(gè)電壓電平以及每個(gè)單元4bit(QLC)的16個(gè)電壓電平和每個(gè)單元5bit(PLC)的32個(gè)電壓電平。

理想情況下,這通過增加存儲(chǔ)字節(jié)而不增加存儲(chǔ)單元的物理數(shù)量來實(shí)現(xiàn)“自由”縮放。每個(gè)單元4bit的QLC NAND于2018年問世,SK海力士從英特爾收購的Solidigm團(tuán)隊(duì)一直在談?wù)撁總€(gè)單元5bit PLC浮柵NAND。Kioxia的研究人員甚至在2021年證明了在低溫條件下每個(gè)Cell可以達(dá)到7bit。

然而,邏輯縮放的主要缺點(diǎn)是減少每個(gè)存儲(chǔ)狀態(tài)的電子數(shù)量。增加每個(gè)單元的電壓狀態(tài)的數(shù)量意味著劃分每個(gè)存儲(chǔ)單元的電子存儲(chǔ)容量。每個(gè)狀態(tài)的電子數(shù)量減少會(huì)增加可變性并破壞可靠性。2D NAND已經(jīng)達(dá)到了TLC技術(shù)的極限,3D NAND也很快接近了類似的極限。展望未來,我們開始看到這種影響,這標(biāo)志著邏輯縮放的結(jié)束。

制造商發(fā)現(xiàn),制造更小的Cell(橫向+垂直),每個(gè)Cell容納更少的電子,使每個(gè)Cell的高位無法維持。例如,Solidigm的192層PLC出現(xiàn)故障,由于成本結(jié)構(gòu)較差,不會(huì)大量生產(chǎn)。

三星的大于236層V9代3D NAND也顯示出QLC與TLC的代擴(kuò)展性較差。在V7代中,QLC比TLC密度高40%。使用V9時(shí),QLC的密度僅為TLC的20%。這是因?yàn)镼LC存儲(chǔ)單元不能像TLC單元那樣收縮得那么多。因此,美光和SK海力士相信TLC(每個(gè)單元3bit)NAND將是最具成本效益的長期解決方案。

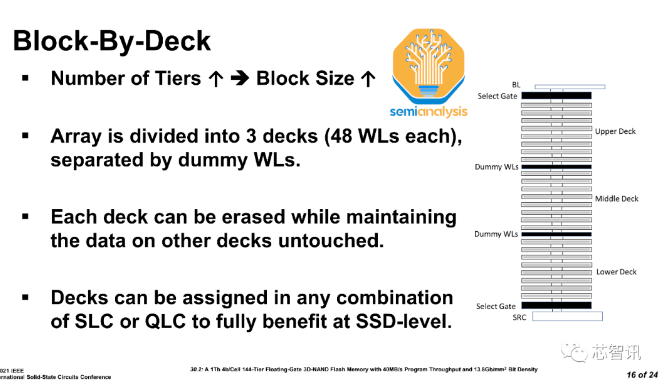

其次是垂直縮放,這是過去十年中NAND密度增長的主要途徑。當(dāng)前的高縱橫比(HAR)蝕刻深度限制為6至7微米,每個(gè)單元的最小厚度約為40nm。到目前為止,制造商只能實(shí)現(xiàn)多達(dá)128個(gè)字線層堆疊(每個(gè)約50nm)。除此之外,還需要將多個(gè)單獨(dú)蝕刻并組合在另一個(gè)deck(層面)上的deck串堆疊。Solidigm的192層設(shè)計(jì)使用了四個(gè)48層deck,而海力士最新一代238層設(shè)計(jì)使用了兩個(gè)deck,每個(gè)deck有119條活動(dòng)字線。

理想情況下,deck越少越好,因?yàn)樾枰貜?fù)的制造步驟越少,堆疊deck時(shí)出現(xiàn)對齊錯(cuò)誤的風(fēng)險(xiǎn)越低。否則,垂直縮放的唯一其他方式是減小每個(gè)存儲(chǔ)器單元和字線的Z方向厚度,或者增加HAR蝕刻深度,下面詳細(xì)說明。這就是為什么東京電子可以從泛林集團(tuán)公司獲得大量業(yè)務(wù)的原因。稍后描述的沉積變化可能同樣具有影響力。

第三是在X和Y方向上進(jìn)行傳統(tǒng)的橫向縮放。這可以通過增加存儲(chǔ)器溝道孔的密度或通過減少狹縫和存儲(chǔ)器塊細(xì)分的面積開銷來實(shí)現(xiàn)。前者已經(jīng)被開發(fā)出來了,因?yàn)樾枰獙⑺袑佣及惭b在側(cè)壁上以形成電荷陷阱單元,所以空穴不會(huì)變得更小。孔之間的間距目前也盡可能小。

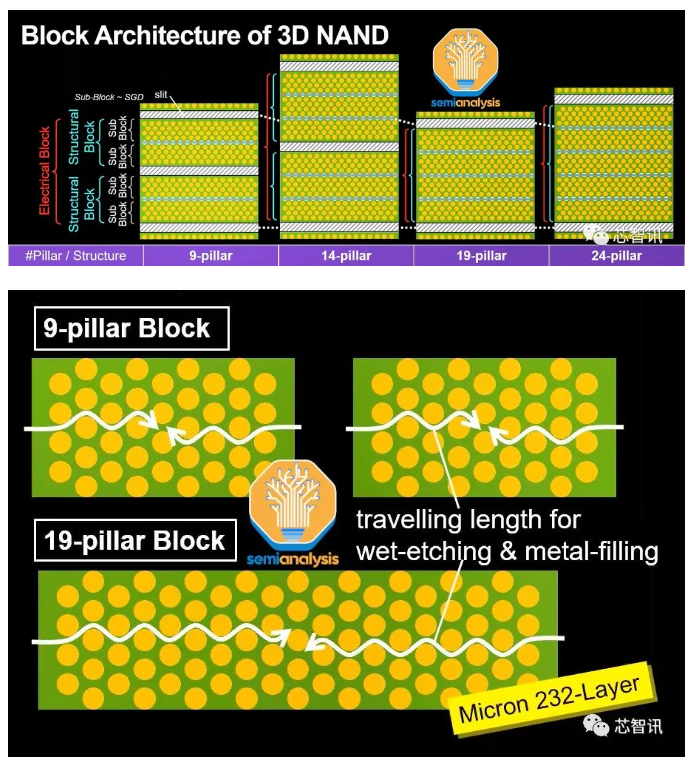

對于后者,美光和西部數(shù)據(jù)/鎧俠(WDC/Kioxia)增加了狹縫之間的通道孔的數(shù)量,減少了狹縫的總數(shù),從而實(shí)現(xiàn)了通孔的更好面積利用。這意味著它們的替換柵極工藝必須水平地深入層中,以正確地去除所有SiN(氮化硅)殘留物并干凈地進(jìn)行隨后的W(鎢)填充。

自64層NAND產(chǎn)生以來,行業(yè)標(biāo)準(zhǔn)一直是狹縫之間的9根支柱。美光的232層NAND在狹縫之間變成了19個(gè)支柱,而西部數(shù)據(jù)/鎧俠 BiCS6 162層在狹縫間變成了24個(gè)支柱,盡管我們尚未發(fā)現(xiàn)這種情況在市場上廣泛普及。他們的 218 層 BiCS8 將會(huì)更進(jìn)一步,不再需要一排虛擬孔來分隔子塊。

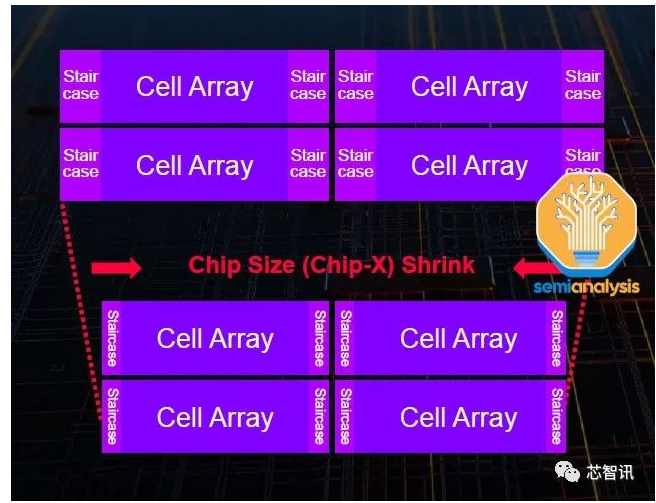

雖然與垂直縮放相比,這些橫向縮放技術(shù)的密度增益較小,但它確實(shí)能夠在不增加WFE(晶圓廠設(shè)備投資)強(qiáng)度的情況下線性降低成本。除此之外,還可以通過使用交錯(cuò)“樓梯”設(shè)計(jì)來減少陣列兩側(cè)“樓梯”的頭頂面積,從而實(shí)現(xiàn)橫向縮放。然而,這是以增加布線密度和字線連接區(qū)域的復(fù)雜性為代價(jià)的。

最后是架構(gòu)縮放。它關(guān)注CMOS邏輯外圍電路的放置位置。設(shè)計(jì)從簡單的CMOS Next to Array,到最近的CMOS Under Array,通過在NAND堆棧下方構(gòu)建電路來節(jié)省芯片面積。然而,由于NAND陣列處理步驟的苛刻性質(zhì),CMOS邏輯處理技術(shù)存在限制。CMOS鍵合陣列(CBA)通過在單獨(dú)的芯片上制造邏輯來解決這一問題,然后通過混合鍵合將該芯片鍵合到存儲(chǔ)器陣列芯片上。

這使得更高級的邏輯和更高的布線密度能夠?qū)崿F(xiàn)階梯和子塊劃分的進(jìn)一步橫向縮放。由于并行制造邏輯和存儲(chǔ)器,可以通過降低設(shè)計(jì)/工藝復(fù)雜性和循環(huán)時(shí)間來抵消接合多個(gè)芯片帶來的成本增加。YMTC憑借其64層Xtacking 1.0和令人驚嘆的1.0微米間距混合粘合引領(lǐng)潮流。西部數(shù)據(jù)/鎧俠 BiCS8 218層也將采用混合鍵合工藝,其他制造商也將效仿。

這些擴(kuò)大規(guī)模的途徑大多已經(jīng)被挖掘出來。雖然垂直擴(kuò)展一直是擴(kuò)展的主要方式,但即使如此,目前的制造設(shè)備也開始采用這種方式。

3D NAND結(jié)構(gòu)和制造流程

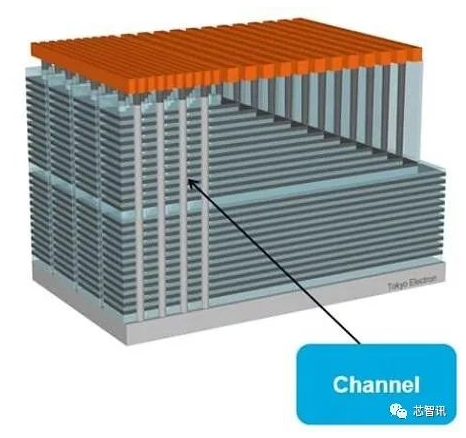

氧化物和氮化物薄膜的交替層首先沉積在基底芯片上。每個(gè)層的厚度在20至30nm之間。每個(gè)疊層的理論極限可以超過250層高并且接近7微米的高度。然后添加厚的硬掩模以準(zhǔn)備高縱橫比(HAR)溝道空穴蝕刻。這種反應(yīng)離子蝕刻工藝挖掘出比寬度深70倍的孔陣列。通道孔在圓度和整個(gè)孔深度上的均勻性對于降低存儲(chǔ)單元性能的可變性至關(guān)重要。對于具有多個(gè)deck的設(shè)計(jì),重復(fù)這些步驟,然后將這些deck堆疊在彼此的頂部。

由此,用多層填充溝道空穴以形成電荷陷阱單元,每一層沉積在側(cè)壁上使得空穴逐漸變窄。接下來是金屬置換柵極工藝。狹縫通過所有層被蝕刻下來,形成暴露出堆疊側(cè)面的溝槽。這允許通過ALD和鎢字線填充進(jìn)行氮化物層的挖掘和隨后的勢壘沉積。在陣列的側(cè)面蝕刻階梯以將字線層暴露于垂直接觸。

最后,位線和金屬互連形成在所制造的CMOS電路之上,并與所制造的包括字線驅(qū)動(dòng)器和用于NAND接口的其他外圍電路的CMOS電路連接。由此,我們看到3D NAND高度依賴于HAR蝕刻和沉積能力來縮放密度和性能。

如前所述,3D NAND主要限制是在制造工藝中蝕刻溝道通孔。這就是為什么每GB的原始處理時(shí)間(以及因此的處理成本)擴(kuò)展預(yù)計(jì)將從我們觀察到的歷史趨勢放緩的原因。這是這篇文章的重點(diǎn)。

NAND市場信息更新

目前NAND市場持續(xù)疲軟,產(chǎn)能嚴(yán)重過剩。由于供應(yīng)過剩,目前晶圓產(chǎn)能利用率在60%的范圍內(nèi)。庫存情況也是巨大的。這是自1997年以來我們看到的最嚴(yán)重的供需不匹配。

現(xiàn)在,主要的NAND制造商都在降低產(chǎn)能利用率,試圖減少庫存,使市場恢復(fù)平衡。然而,技術(shù)轉(zhuǎn)型仍需要一些投資。三星做為最大的NAND生產(chǎn)商(34%的市場份額)在NAND工藝上已經(jīng)落后了。它目前的die仍然主要是128層,176層NAND仍然只是一小部分。這遠(yuǎn)遠(yuǎn)落后于SK海力士和美光,后者處于超過200層的技術(shù)節(jié)點(diǎn)。

三星正試圖將今年的大部分產(chǎn)能轉(zhuǎn)移到236層。他們實(shí)際上在很大一部分生產(chǎn)中跳過了一個(gè)節(jié)點(diǎn)。雖然他們在技術(shù)轉(zhuǎn)型方面的投資將在今年支持NAND WFE,但這只會(huì)推遲NAND市場復(fù)蘇,因?yàn)槊鎸Σ粩嘣鰪?qiáng)的產(chǎn)出能力,需求能力顯得更加疲軟。一旦三星技術(shù)轉(zhuǎn)型完成,他們將為市場帶來另外70%的NAND容量增長。三星想強(qiáng)行進(jìn)行整合,這是一種從公司最高層開始的策略。

Semianalysis相信,與2023年相比,2024年將是NAND資本支出更加精簡的一年。預(yù)計(jì)到2025年NAND供需將強(qiáng)勁復(fù)蘇,因?yàn)榫薮蟮膸齑婧偷彤a(chǎn)能利用率提供了緩沖。長期需求將繼續(xù)增長,該行業(yè)最終需要持續(xù)投資來滿足這一需求。但是,對于NAND制造的資本支出增長可能將會(huì)相對較少,而且頭部的西部數(shù)據(jù)和鎧俠的可能的合并可能也將抑制這方面的資本支出。

東京電子將突破泛林集團(tuán)在NAND刻蝕設(shè)備領(lǐng)域的壟斷?

由于這篇報(bào)告后半部分為收費(fèi)內(nèi)容,因此這里只能給出Semianalysis的最新研究的結(jié)論,即隨著3D DRAM的可能性和即將到來的沉積材料的重大變化,NAND制造設(shè)備市場將會(huì)面臨重大改變,市場份額可能將更多的從泛林集團(tuán)轉(zhuǎn)向東京電子,這可能意味著超過10億美元的收入的易手。

芯智訊此前3D DRAM相關(guān)文章:《DRAM將進(jìn)入3D時(shí)代?230層堆棧,容量可提升8倍!》

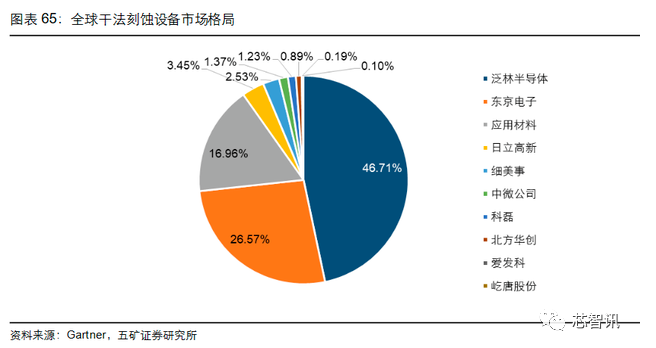

正如前面所介紹的,3D NAND制造過程當(dāng)中,最多的制造步驟是刻蝕和薄膜沉積。而在全球刻蝕設(shè)備和薄膜沉積設(shè)備市場,美國泛林集團(tuán)、日本東京電子和美國應(yīng)用材料這三家廠商占據(jù)主導(dǎo)地位。

Gartner數(shù)據(jù)顯示,在2020年的全球干法刻蝕設(shè)備市場(目前應(yīng)用主要以干法刻蝕為主,占比90%以上),泛林集團(tuán)(46.71%)、東京電子(26.57%)和應(yīng)用材料(16.96%)合計(jì)占據(jù)90%以上的全球刻蝕設(shè)備市場份額,日立高新和細(xì)美事緊隨其后分別占3.45%和2.53%。國內(nèi)刻蝕設(shè)備廠商當(dāng)中,中微公司占比1.37%,北方華創(chuàng)占比0.89%,屹唐股份占比0.10%。有數(shù)據(jù)顯示,2022年,泛林集團(tuán)在刻蝕設(shè)備的市場的份額已經(jīng)高達(dá)55%。

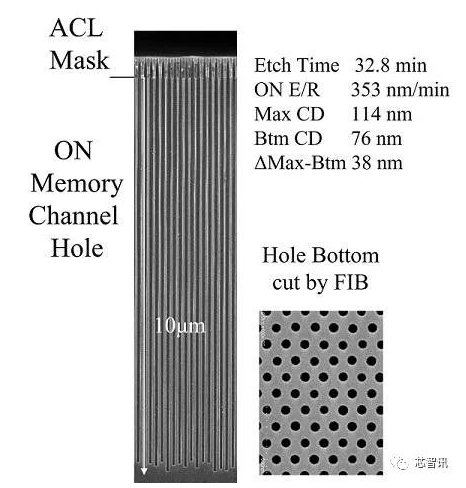

顯然,目前泛林集團(tuán)在刻蝕設(shè)備市場的份額大幅高于東京電子,特別是在NAND刻蝕設(shè)備領(lǐng)域居于近乎壟斷的優(yōu)勢地位。雖然芯智訊并未觀察到Semianalysis所說的材料變化對于NAND制造設(shè)備領(lǐng)域的重大影響,但是芯智訊注意到,東京電子在今年6月的的半導(dǎo)體國際會(huì)議報(bào)告中,展示一項(xiàng)新的蝕刻技術(shù)(疑似命名為MolyDep+),可以在400層以上的3D NAND堆疊結(jié)構(gòu)形成存儲(chǔ)通道孔洞(memory channel holes)。

據(jù)介紹,原本無法在極低溫環(huán)境下實(shí)際運(yùn)作的絕緣膜蝕刻,現(xiàn)在東京電子開發(fā)出新的制程技術(shù),并制作出相應(yīng)的設(shè)備,首次將電介質(zhì)蝕刻應(yīng)用帶入低溫范圍,從而打造了一個(gè)具有極高蝕刻率的系統(tǒng)。可在短短的33分鐘內(nèi)形成高縱橫比的10微米的蝕刻深度,縮減了耗時(shí),而且蝕刻結(jié)構(gòu)的幾何形狀相當(dāng)明顯,也有助于制造更高容量的3D NAND閃存芯片。且比以前減少84%的全球暖化潛能值(Global warming potential),也就是說整體所需的能耗得到了大幅降低。

東京電子還提供了蝕刻后的相關(guān)圖像,展示了開發(fā)的成果。其中包括顯示了蝕刻后通孔圖案的橫截面SEM圖像,以及孔底的FIB切割圖像,另外還有東京電子的3D NAND閃存芯片的一個(gè)案例。

或許東京電子最新的這項(xiàng)在蝕刻技術(shù)上的突破,將有助于其提升在刻蝕設(shè)備市場的競爭力,從而搶下更多屬于泛林集團(tuán)的市場份額。