SPICE與IBIS:為電路仿真選擇更合適的模型

2023-11-26

作者:May Anne Porley,應(yīng)用工程師;Jermaine Lim-Abrogueña,系統(tǒng)集成工程師;Mar Christian Lacida,產(chǎn)品應(yīng)用工程師

來(lái)源:ADI公司

摘要

隨著電路仿真技術(shù)在原型設(shè)計(jì)行業(yè)的不斷普及,仿真模型可能成為廣大終端市場(chǎng)客戶(hù)的一項(xiàng)關(guān)鍵需求。SPICE和IBIS模型是非常受歡迎的兩種仿真模型,有助于在電路板開(kāi)發(fā)的原型設(shè)計(jì)階段節(jié)省成本。本文將介紹SPICE與IBIS建模系統(tǒng)的區(qū)別,以及在制造電路板之前進(jìn)行測(cè)試的重要意義。將討論如何根據(jù)電路設(shè)計(jì)選擇合適的模型。此外還將分析一些示例使用場(chǎng)景和常用的仿真工具,如LTspice? 和HyperLynx?。

簡(jiǎn)介

在這個(gè)技術(shù)飛速發(fā)展的數(shù)字時(shí)代背后,電子制造商源源不斷地開(kāi)發(fā)行業(yè)所需的基本元器件和工具,全力支持這一數(shù)字化發(fā)展進(jìn)程。對(duì)于仿真而言,這意味著電路板開(kāi)始開(kāi)發(fā)后,設(shè)計(jì)人員可以在系統(tǒng)設(shè)計(jì)驗(yàn)證階段通過(guò)仿真模型來(lái)確保其功能設(shè)計(jì)符合預(yù)期。在制造前測(cè)試設(shè)計(jì)時(shí),SPICE和IBIS模型是常用的兩種仿真模型。這兩種模型本質(zhì)上都是行為模型,但對(duì)于仿真中何時(shí)使用某種模型,根據(jù)具體情況有不同的建議。

使用仿真模型的好處

一般而言,仿真模型有助于系統(tǒng)設(shè)計(jì)人員在原型制作之前對(duì)電路設(shè)計(jì)進(jìn)行仿真。使用IBIS和SPICE仿真模型時(shí),目標(biāo)不僅僅是仿真,還包括盡早發(fā)現(xiàn)與信號(hào)完整性和電路設(shè)計(jì)性能等相關(guān)的任何問(wèn)題。這些問(wèn)題通常是由電路板設(shè)計(jì)的特性(包括走線(xiàn))引起的,或者也可能是元器件功能之類(lèi)的簡(jiǎn)單問(wèn)題。

IBIS模型不僅能表示元器件的箝位行為和驅(qū)動(dòng)強(qiáng)度,還能表示數(shù)字輸入/輸出(I/O)緩沖器的阻抗,包括驅(qū)動(dòng)器和/或接收器的輸出和輸入阻抗。這些并未在模型中直接說(shuō)明,但都隱含在表示元器件行為的I-V數(shù)據(jù)中。在仿真過(guò)程中,確定緩沖器阻抗非常重要,因?yàn)檫@些阻抗是解決串?dāng)_和反射等信號(hào)完整性問(wèn)題的關(guān)鍵。串?dāng)_是一種不需要的信號(hào)干擾,當(dāng)一條走線(xiàn)上傳播的信號(hào)與另一條走線(xiàn)上傳播的信號(hào)耦合時(shí)就會(huì)發(fā)生串?dāng)_。另一方面,在制造電路板之前進(jìn)行信號(hào)完整性仿真期間,也往往會(huì)遇到反射問(wèn)題。眾所周知,當(dāng)輸入或輸出緩沖器的阻抗與走線(xiàn)的特性阻抗不匹配時(shí),就會(huì)發(fā)生反射。理想情況下,進(jìn)入器件并沿走線(xiàn)傳播的信號(hào)應(yīng)在沒(méi)有任何干擾的情況下傳輸?shù)阶呔€(xiàn)的另一端。但實(shí)際上,這種情況通常不會(huì)發(fā)生。由于阻抗不匹配,信號(hào)完整性會(huì)受到影響。在發(fā)生反射期間,通常的情況是:沿傳輸線(xiàn)傳播的信號(hào)一部分會(huì)傳輸?shù)搅硪欢耍硪徊糠謱?huì)反射回來(lái)。解決此問(wèn)題的一種辦法是向緩沖器添加端接電阻。設(shè)計(jì)人員可以利用IBIS模型的阻抗特性來(lái)計(jì)算端接所需的串聯(lián)或并聯(lián)電阻,與引腳和傳輸線(xiàn)之間的阻抗相匹配,并解決信號(hào)反射問(wèn)題。

SPICE模型通過(guò)預(yù)測(cè)電路行為,可以在構(gòu)建原型之前發(fā)現(xiàn)、考慮并解決可能存在的問(wèn)題,從而增強(qiáng)電路性能,這對(duì)于時(shí)間和資金的高效利用具有重要意義。成本和速度是SPICE模型仿真的兩個(gè)主要優(yōu)勢(shì)。也就是說(shuō),在開(kāi)發(fā)過(guò)程的早期避免電路錯(cuò)誤,從而消除昂貴且耗時(shí)的原型返工,以免重新訂購(gòu)和重新焊接元器件。如今的仿真模型更加先進(jìn),可以提供準(zhǔn)確的元器件性能近似值。設(shè)計(jì)人員可以輕松更換元器件,以評(píng)估采用不同物料清單(BOM)的電路設(shè)計(jì)。同時(shí),設(shè)計(jì)人員不必花費(fèi)很多時(shí)間制作電路組件原型,也不必在發(fā)現(xiàn)并糾正原型錯(cuò)誤后重新焊接組件。

背景知識(shí)

什么是SPICE模型?

SPICE是Simulation Program with Integrated Circuit Emphasis(以集成電路為重點(diǎn)的仿真程序)的首字母縮寫(xiě)。它是一種通用電路仿真器,采用文本網(wǎng)表描述電路元件(晶體管、電阻和電容)及其連接,并使用節(jié)點(diǎn)分析將其轉(zhuǎn)換為數(shù)學(xué)方程進(jìn)行求解。相對(duì)而言,SPICE模型是一種基于文本的行為模型,SPICE仿真器使用這種模型通過(guò)數(shù)學(xué)運(yùn)算預(yù)測(cè)器件在不同條件下的行為。

什么是IBIS模型?

IBIS是Input/Output Buffer Information Specification(輸入/輸出緩沖器信息規(guī)范)的首字母縮寫(xiě)。它是一種行為模型,描述器件的數(shù)字輸入和輸出緩沖器的模擬行為。它由表格數(shù)據(jù)組成,描述數(shù)字緩沖器內(nèi)元器件的電流-電壓(I-V)關(guān)系,以及輸出或I/O緩沖器的電壓隨時(shí)間變化的(V-t)開(kāi)關(guān)特性。它用于在制造之前對(duì)系統(tǒng)板進(jìn)行信號(hào)完整性分析,并以純ASCII文本格式的數(shù)據(jù)呈現(xiàn)。它不披露任何專(zhuān)有信息,因?yàn)镮BIS模型就像一個(gè)黑盒模型,不包含可逆向工程的內(nèi)部信息。

模型概述

模型看起來(lái)是什么樣子?

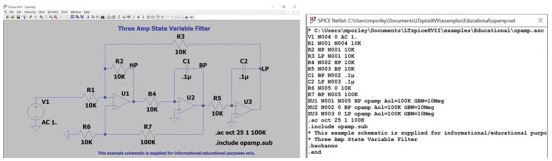

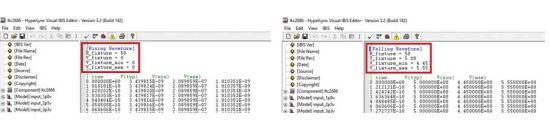

圖1.左側(cè)是使用LTspice打開(kāi)的SPICE文件(.cir),右側(cè)是使用Siemens的HyperLynx打開(kāi)的IBIS文件(.ibs)

如圖1所示,IBIS和SPICE模型都是基于文本的行為模型,可以使用記事本等簡(jiǎn)單工具查看其內(nèi)容。不過(guò),為了更方便地瀏覽模型,建議使用Cadence Model Integrity或Siemens的HyperLynx查看IBIS文件。另一方面,SPICE模型可以在各種SPICE仿真工具中打開(kāi)并安裝,例如LTspice、NI Multisim?、OrCAD? PSpice? 或其他SPICE仿真器。

SPICE和IBIS模型都是不可執(zhí)行文件,并且都是基于文本的描述文件。這兩種模型大多數(shù)都由三個(gè)主要部分組成:

▲頭文件:提供關(guān)于模型、器件、修訂歷史記錄、模型特有的注釋以及建模器件的公司或品牌的簡(jiǎn)要描述或一般信息。

▲模型名稱(chēng)/標(biāo)題:主要提及器件名稱(chēng)、引腳排列和/或引腳到緩沖器映射。對(duì)于SPICE,格式為:點(diǎn)子電路<空格>模型名稱(chēng)(.subckt ADGxx)<空格>引腳排列。對(duì)于IBIS,格式為:[Component] ADGxx。

▲模型結(jié)構(gòu):基于文本的模型表示。SPICE模型由不同的塊組成,這些塊展示器件的每個(gè)參數(shù),包括引腳功能;各個(gè)塊可能包括原始和原生元件,如電容、電阻、二極管、電壓源和電流源等。另一方面,IBIS模型由I/V和V/T數(shù)據(jù)表組成,這些數(shù)據(jù)表是對(duì)每個(gè)數(shù)字I/O緩沖器建模的結(jié)果。

如何獲取模型?

SPICE和IBIS模型大多位于各家半導(dǎo)體公司的網(wǎng)頁(yè)上。如今,半導(dǎo)體制造商針對(duì)自己的產(chǎn)品開(kāi)發(fā)仿真模型,同時(shí)保持模型的包容性、內(nèi)容、準(zhǔn)確性和模型支持。ADI公司網(wǎng)站提供了ADI產(chǎn)品的各種SPICE和IBIS模型,如圖2所示。

圖2.ADI網(wǎng)站中各種SPICE(左)和IBIS(右)模型

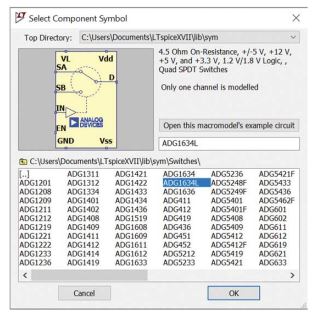

其他SPICE模型可以在制造商的SPICE仿真器庫(kù)中找到。圖3顯示了LTspice的開(kāi)關(guān)庫(kù),它涵蓋了ADI公司的大部分開(kāi)關(guān)產(chǎn)品。為了簡(jiǎn)化仿真方法,選擇具有大量可用SPICE模型庫(kù)的SPICE仿真器會(huì)很有幫助。

圖3.LTspice中包含大量SPICE模型庫(kù)示例

補(bǔ)充文件

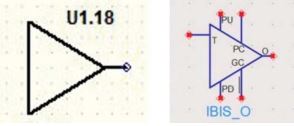

為了在仿真器中使用,SPICE和IBIS模型都需要隨附一個(gè)符號(hào)文件。IBIS模型通常以基于文本的數(shù)據(jù)表示的形式出現(xiàn),但為了使用電子設(shè)計(jì)自動(dòng)化工具對(duì)其進(jìn)行仿真,一般會(huì)將模型置于符號(hào)中,外部元器件可連接到該符號(hào)。與IBIS模型類(lèi)似,SPICE模型也需要一個(gè)符號(hào)文件,該文件通常為點(diǎn)符號(hào)(.asy)格式,必須同時(shí)安裝到SPICE仿真器庫(kù)中。只需將模型和符號(hào)添加/安裝到庫(kù)中,設(shè)計(jì)人員就可以在電路仿真中使用模型。圖4和圖5顯示了IBIS和SPICE模型中使用的符號(hào)文件示例。

圖4.使用HyperLynx(左)和Advanced Design System(右)的輸出緩沖器IBIS符號(hào)

圖5.簡(jiǎn)單3引腳運(yùn)算放大器的SPICE符號(hào)文件(右)模板,及其在LTspice電路仿真中使用的等效符號(hào)(左)

對(duì)于IBIS和SPICE,制造商均不提供符號(hào)文件,但大多數(shù)仿真器提供模板符號(hào),設(shè)計(jì)人員可以根據(jù)引腳數(shù)量或器件類(lèi)型使用這些符號(hào)。另外,SPICE符號(hào)文件還可以自動(dòng)生成,此功能取決于SPICE仿真器。

模型比較

SPICE模型

一般而言,SPICE模型可復(fù)現(xiàn)元器件行為,包括引腳排列、引腳配置、功能和其他操作。這些模型沒(méi)有標(biāo)準(zhǔn)架構(gòu),但其目標(biāo)是創(chuàng)建一個(gè)準(zhǔn)確復(fù)現(xiàn)元器件預(yù)期行為性能(包括其引腳功能)的架構(gòu)。模型可能由電阻、電容、二極管和晶體管等無(wú)源元件組成,如果設(shè)計(jì)得當(dāng),這些元件就會(huì)產(chǎn)生目標(biāo)元件行為。需要記住一點(diǎn),由于SPICE模型可準(zhǔn)確復(fù)現(xiàn)元器件的行為,因此可能會(huì)包含復(fù)雜電路,從而導(dǎo)致仿真周期變慢。SPICE模型可以是簡(jiǎn)單的單行文本,描述電阻之類(lèi)的無(wú)源元件,也可以長(zhǎng)達(dá)數(shù)百行,描述更復(fù)雜的電路和子電路。

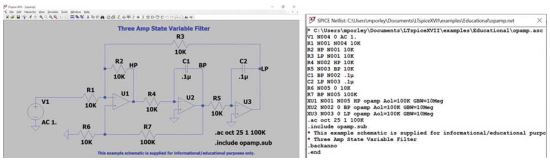

如上所述,SPICE模型可以使用基于文本的工具打開(kāi),但大多數(shù)最新的SPICE仿真器支持查看等效原理示意圖,以便更輕松地進(jìn)行電路分析。如圖6所示,其中三放大器狀態(tài)變量濾波器也可以轉(zhuǎn)換為等效的描述電路元件及其連接的文本網(wǎng)表。

圖6.三放大器狀態(tài)變量濾波器的SPICE模型示例

在模型性能方面,根據(jù)經(jīng)驗(yàn)法則,SPICE模型可提供與器件數(shù)據(jù)手冊(cè)給出的規(guī)格和功能相近的行為性能。例如,開(kāi)關(guān)SPICE模型應(yīng)具有導(dǎo)通電阻和時(shí)序參數(shù),而放大器很可能具有增益帶寬和輸入失調(diào)參數(shù)。相對(duì)而言,模型功能和規(guī)格必須接近數(shù)據(jù)手冊(cè)中提供的典型值、最小值或最大值,或在這些值的范圍以?xún)?nèi)。

IBIS模型

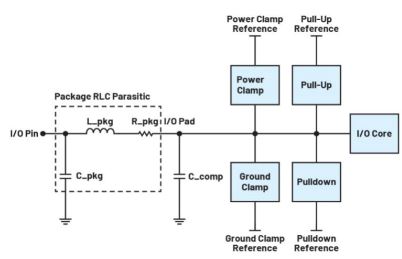

一般而言,IBIS模型以標(biāo)準(zhǔn)架構(gòu)來(lái)表示數(shù)字I/O緩沖器。這通過(guò)IBIS關(guān)鍵詞表示來(lái)實(shí)現(xiàn),關(guān)鍵詞用于描述數(shù)字緩沖器的每個(gè)組件,如圖7所示。IBIS關(guān)鍵詞以V-I查找數(shù)據(jù)表和V-t查找數(shù)據(jù)表的形式出現(xiàn)。

圖7.典型I/O緩沖器的IBIS框圖

圖8.ADG5401F的IBIS關(guān)鍵詞的V-I數(shù)據(jù)(左);使用Siemens HyperLynx繪制的V-I曲線(xiàn)(右)

圖8中的左圖顯示了IBIS模型中的V-I查找表示例,右圖顯示了使用Siemens HyperLynx繪制該V-I查找表得到的波形。它是在一組電壓范圍(通常從-VDD到兩倍VDD)下進(jìn)行的一系列電流測(cè)量,以表示特定IBIS元器件在三種情況(典型工藝角、慢工藝角和快工藝角)下的行為。這可通過(guò)改變器件的工藝角、工作電壓和工作溫度來(lái)完成。這些表以[Power_clamp]和[GND_clamp]關(guān)鍵詞表示接收器的箝位保護(hù)元件,并以[Pullup]和[Pulldown]關(guān)鍵詞表示I/O緩沖器的驅(qū)動(dòng)強(qiáng)度。這4個(gè)V-I關(guān)鍵詞在模型中單獨(dú)表示,因?yàn)榻邮漳J胶万?qū)動(dòng)模式都是信號(hào)完整性仿真所必需的。

另一方面,V-t表以[Rising_Waveform]和[Falling_Waveform]的形式表示驅(qū)動(dòng)器從一種狀態(tài)轉(zhuǎn)換到另一種狀態(tài)時(shí)的開(kāi)關(guān)特性(負(fù)載以VDD和地為參考時(shí))。它還在IBIS關(guān)鍵詞[Ramp]項(xiàng)下包含I/O緩沖器的擺率,該擺率是在轉(zhuǎn)換邊沿的20%到80%范圍測(cè)量的。這些波形和斜坡數(shù)據(jù)描述了驅(qū)動(dòng)器部件開(kāi)啟或關(guān)閉的速度與時(shí)間的關(guān)系。

雖然這些關(guān)鍵詞在模型中是單獨(dú)表示的,但在仿真期間使用時(shí),電子設(shè)計(jì)自動(dòng)化仿真工具會(huì)結(jié)合這些V-I和V-t數(shù)據(jù),根據(jù)其工作區(qū)域構(gòu)建緩沖器模型,并且會(huì)使用該模型執(zhí)行印刷電路板的信號(hào)完整性仿真和時(shí)序分析。

此外,IBIS模型還包含器件的RLC引腳和/或封裝寄生值,以及每個(gè)I/O緩沖器的緩沖器電容(C_Comp)。C_comp是從焊盤(pán)回到緩沖器的電容,不包括封裝電容。

仿真工具

現(xiàn)有各種各樣的行業(yè)標(biāo)準(zhǔn)SPICE和IBIS仿真器,可為大多數(shù)高速設(shè)計(jì)系統(tǒng)以及模擬和混合信號(hào)電路提供設(shè)計(jì)仿真,適合專(zhuān)業(yè)人士和教培人員使用。SPICE仿真器通常根據(jù)電路連接/節(jié)點(diǎn)生成節(jié)點(diǎn)方程,然后嘗試求解各個(gè)節(jié)點(diǎn)處的電流和電壓值。另一方面,IBIS仿真器參照模型中提供的V-I和V-t查找數(shù)據(jù)表來(lái)預(yù)測(cè)信號(hào)的輸出行為。業(yè)界常用的仿真器包括:

IBIS仿真器

▲Siemens的HyperLynx是一款電子設(shè)計(jì)自動(dòng)化工具,用于分析高速電子設(shè)計(jì)中的信號(hào)完整性、電源完整性、電氣設(shè)計(jì)規(guī)則檢查和電磁建模。該工具可用于查看、編輯IBIS模型以及利用模型進(jìn)行仿真。

▲Keysight的Advanced Design System是一款電子設(shè)計(jì)自動(dòng)化工具,可用于各種設(shè)計(jì)流程,例如頻域和時(shí)域電路仿真、原理圖設(shè)計(jì)和布局、設(shè)計(jì)規(guī)則檢查、電磁場(chǎng)仿真等。該工具常用于IBIS模型仿真。

SPICE仿真器

▲LTspice是一款高性能SPICE仿真器軟件,包括原理圖捕獲圖形界面。通過(guò)內(nèi)置波形查看器可探測(cè)原理圖以產(chǎn)生仿真結(jié)果。這款SPICE仿真器的圖形用戶(hù)界面(GUI)基于對(duì)原理圖輸入所需的鍵盤(pán)輸入和鼠標(biāo)動(dòng)作的統(tǒng)計(jì)分析,與其他SPICE仿真相比交互性更強(qiáng)。LTspice包括一個(gè)龐大的SPICE模型庫(kù),其涵蓋了大部分ADI產(chǎn)品和信號(hào)鏈產(chǎn)品,另外還有一個(gè)無(wú)源元件庫(kù)。

▲NI Multisim具有交互式原理圖環(huán)境,可即時(shí)可視化和分析電子電路行為。該仿真器具有虛擬示波器、數(shù)字萬(wàn)用表和其他基準(zhǔn)測(cè)試設(shè)備,使電路仿真體驗(yàn)接近典型的工程師試驗(yàn)臺(tái)評(píng)估環(huán)境。

▲OrCAD PSpice Designer集原理圖輸入、原生模擬、混合信號(hào)和分析引擎于一體,提供完整的電路仿真和驗(yàn)證解決方案。無(wú)論是制作簡(jiǎn)單電路原型、設(shè)計(jì)復(fù)雜系統(tǒng),還是驗(yàn)證元器件良率和可靠性,OrCAD PSpice技術(shù)都能提供出色的高性能電路仿真,讓您在進(jìn)行布局和制造之前有效分析和完善電路、元器件及參數(shù)。

IBIS模型和SPICE模型用例

IBIS模型

IBIS模型通常以基于文本的數(shù)據(jù)表示的形式出現(xiàn),但為了使用EDA工具對(duì)其進(jìn)行仿真,一般會(huì)將模型置于符號(hào)中,外部元器件可連接到該符號(hào)。仿真器使用模型中包含的數(shù)據(jù)來(lái)分析和預(yù)測(cè)給定情況下的緩沖器行為。

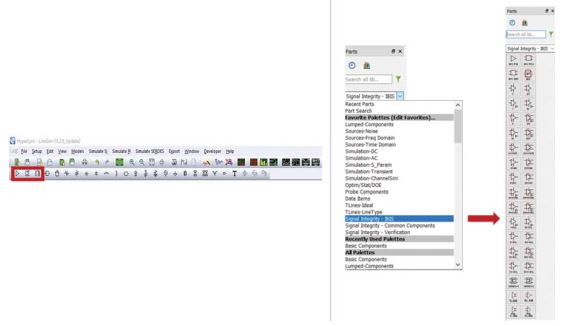

Siemens的HyperLynx和Keysight的Advanced Design System都具有IBIS符號(hào),設(shè)計(jì)人員可以在仿真中使用這些符號(hào)。圖9展示了這些符號(hào)在這些工具中的顯示方式。

圖9.HyperLynx工具欄顯示了可用于IBIS模型仿真的單端緩沖器、差分緩沖器和IC器件的符號(hào)(左);Advanced Design System工具欄顯示了可用于IBIS模型仿真的不同類(lèi)型緩沖器的符號(hào)(右)

▲在HyperLynx中進(jìn)行單端輸入或輸出緩沖器仿真時(shí),可以使用左圖第一個(gè)突出顯示的緩沖器,然后加載IBIS模型并選擇要仿真的具體緩沖器。如果選擇輸出緩沖器模型,工具會(huì)自動(dòng)顯示輸出緩沖器。否則,如果要仿真輸入緩沖器,工具會(huì)自動(dòng)將符號(hào)轉(zhuǎn)換為輸入緩沖器符號(hào)。

▲在Advanced Design System中,“Signal Integrity - IBIS”(信號(hào)完整性 - IBIS)元件板會(huì)顯示各種類(lèi)型的緩沖器模型。如果需要開(kāi)漏輸出,必須選擇標(biāo)記為OSNK的符號(hào);如果要仿真端接電阻,仿真中必須使用標(biāo)記為T(mén)的符號(hào)。請(qǐng)注意,如果選擇的符號(hào)不對(duì),可能會(huì)導(dǎo)致錯(cuò)誤。例如,如果需要輸入緩沖器,卻在原理圖中放置了輸出緩沖器符號(hào),將無(wú)法看到IBIS中建模的輸入緩沖器可用引腳,因?yàn)榉抡嫫髦辉试S符號(hào)中加載輸出緩沖器引腳。

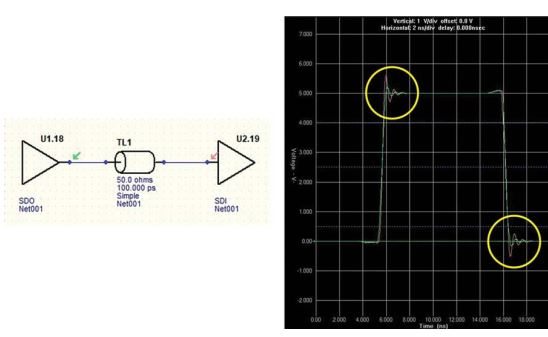

IBIS模型仿真的用途之一是解決不需要的信號(hào)行為,這些行為通常是由緩沖器和充當(dāng)傳輸線(xiàn)的PCB走線(xiàn)之間的阻抗不匹配引起的。例如,圖10中使用HyperLynx的原理圖仿真。

圖10.未采用端接電阻的原理圖(左)及其相應(yīng)的結(jié)果(右)

圖10所示是使用50 Ω走線(xiàn)進(jìn)行的未端接輸出緩沖器仿真,它會(huì)產(chǎn)生不需要的過(guò)沖和欠沖信號(hào)。為了解決此問(wèn)題,可以添加一個(gè)串聯(lián)端接電阻,與緩沖器和走線(xiàn)之間的阻抗相匹配。但在此之前,必須先確定輸出緩沖器的阻抗。

IBIS模型中的V-t表、相對(duì)于地的[Rising_Waveform]和相對(duì)于VDD的[Falling_Waveform]可用于計(jì)算緩沖器的輸出阻抗,因?yàn)樵搮?shù)是模型中表示的數(shù)據(jù)本身固有的。使用分壓器定理可以推導(dǎo)出緩沖器阻抗值,然后使用此值來(lái)計(jì)算需要添加到模型中并與緩沖器和走線(xiàn)之間的阻抗相匹配的適當(dāng)端接電阻。這將有助于解決阻抗失配問(wèn)題,并消除信號(hào)中不需要的過(guò)沖和欠沖。

圖11.分壓器的原理圖

圖11顯示了分壓器的原理圖,其中Zb是緩沖器阻抗,R_fixture和V_fixture可在模型中找到,而VSETTLE是V-t波形穩(wěn)定后的電壓。

圖12.IBIS模型顯示了提取V-T查找表所使用的電路:上升波形(左)和下降波形(右)

確定端接電阻值后,即可將其添加到原理圖中。

圖13.采用端接電阻后的原理圖(左)及其相應(yīng)的結(jié)果(右)

圖13顯示了端接后的原理圖及其相應(yīng)結(jié)果,初始過(guò)沖和下沖問(wèn)題已得到解決。

上述方法只是用于計(jì)算緩沖器阻抗并解決不匹配阻抗問(wèn)題的策略之一。還有其他方法,例如使用IBIS模型的下拉V-I表,并執(zhí)行負(fù)載線(xiàn)路分析來(lái)確定工作點(diǎn)。由此可以推導(dǎo)出輸出阻抗以及串聯(lián)端接電阻的值。

SPICE模型

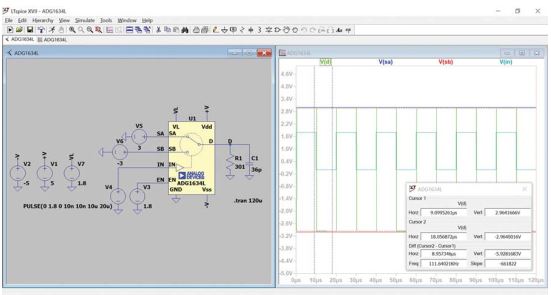

圖14顯示了瞬態(tài)分析中使用ADG1634L模型的SPICE仿真示例。設(shè)計(jì)人員可以評(píng)估ADG1634L的性能(在本例中)并對(duì)其進(jìn)行仿真,以檢查器件的時(shí)序和其他功能;繪圖結(jié)果將在時(shí)域中顯示。瞬態(tài)分析可預(yù)測(cè)器件在指定時(shí)間范圍內(nèi)的行為。SPICE模型還可以在不同類(lèi)型的分析中進(jìn)行仿真,例如直流分析和交流分析。直流分析根據(jù)一系列直流輸入值計(jì)算電路的電壓和電流。交流分析確定電路中節(jié)點(diǎn)的相位和幅度,這對(duì)于檢查頻域中的電路行為可能很有用。

圖14.使用ADG1634L模型的SPICE仿真示例

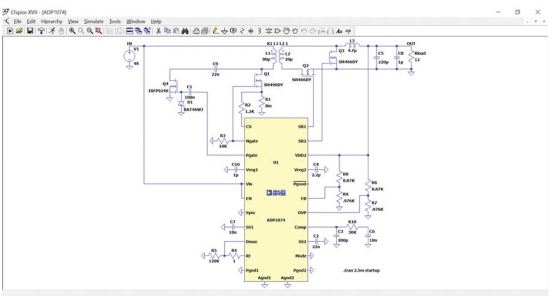

更進(jìn)一步,可以對(duì)更復(fù)雜的電路設(shè)計(jì)進(jìn)行SPICE仿真,從而確定設(shè)計(jì)的性能。參見(jiàn)圖15中的示例。

圖15.LTspice中的正激有源鉗位電路SPICE仿真示例

哪種模型更適合您的仿真?

對(duì)于以下情形,IBIS模型可能非常適合電路仿真:

▲如果設(shè)計(jì)人員正在評(píng)估數(shù)字I/O緩沖器的行為特性,例如緩沖器阻抗、驅(qū)動(dòng)強(qiáng)度、上升時(shí)間或下降時(shí)間

▲當(dāng)您嘗試評(píng)估數(shù)字器件(如FPGA)時(shí)

▲關(guān)注信號(hào)完整性或器件數(shù)字I/O引腳連接到PCB走線(xiàn)時(shí)可能出現(xiàn)傳輸線(xiàn)錯(cuò)誤的設(shè)計(jì)

另一方面,如果需要通過(guò)電路仿真更全面地了解器件性能,包括模擬、數(shù)字和電源引腳功能以及其連接到電路中的多個(gè)器件時(shí)的行為響應(yīng),則建議使用SPICE模型。應(yīng)使用SPICE模型而不是IBIS模型的其他情形包括:

▲需要評(píng)估器件在電路中使用時(shí)的功能及其行為性能時(shí)

▲需要評(píng)估器件在不同分析和域(時(shí)域或頻域)中的行為響應(yīng)時(shí)

▲需要深入細(xì)致的節(jié)點(diǎn)分析并求解電路中的電流和電壓節(jié)點(diǎn)的復(fù)雜設(shè)計(jì)

結(jié)語(yǔ)

SPICE和IBIS模型在業(yè)界越來(lái)越受歡迎,因?yàn)檫@些模型可以幫助設(shè)計(jì)工程師在原型制作之前和期間驗(yàn)證目標(biāo)電路性能,從而節(jié)省設(shè)計(jì)成本和時(shí)間。這兩種模型本質(zhì)上都是行為模型。一般而言,SPICE模型可復(fù)現(xiàn)元器件行為,包括引腳排列、引腳配置、功能和其他操作。IBIS模型使用電壓-電流和電壓-時(shí)間表格數(shù)據(jù)形式的參數(shù)來(lái)模擬器件的數(shù)字I/O行為。為了在仿真器中使用這些模型,SPICE和IBIS模型都需要隨附一個(gè)符號(hào)文件。SPICE模型仿真可預(yù)測(cè)器件的性能,包括其預(yù)期的引腳功能和配置,而IBIS模型仿真通常用于預(yù)測(cè)數(shù)字I/O引腳上出現(xiàn)的信號(hào)完整性問(wèn)題,例如PCB仿真期間的阻抗失配、串?dāng)_、反射、下沖或過(guò)沖。選擇使用哪種模型取決于設(shè)計(jì)人員使用模型的目的。對(duì)于關(guān)注信號(hào)完整性、驅(qū)動(dòng)強(qiáng)度或器件數(shù)字I/O引腳連接到PCB走線(xiàn)時(shí)可能出現(xiàn)傳輸線(xiàn)錯(cuò)誤的設(shè)計(jì),強(qiáng)烈建議使用IBIS模型。另一方面,如果通過(guò)電路仿真了解器件性能,包括在電路中使用時(shí)其模擬、數(shù)字和電源引腳的功能,那么建議使用SPICE模型。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<