如何使用LTspice對(duì)復(fù)雜電路的統(tǒng)計(jì)容差分析進(jìn)行建模

2022-03-09

作者:ADI公司現(xiàn)場(chǎng)應(yīng)用工程師 Steve Knudtsen

來源:ADI公司

摘要

LTspice?可用于對(duì)復(fù)雜電路進(jìn)行統(tǒng)計(jì)容差分析。本文介紹在LTspice中使用蒙特卡羅和高斯分布進(jìn)行容差分析和最差情況分析的方法。為了證實(shí)該方法的有效性,我們?cè)贚Tspice中對(duì)電壓調(diào)節(jié)示例電路進(jìn)行建模,通過內(nèi)部基準(zhǔn)電壓和反饋電阻演示蒙特卡羅和高斯分布技術(shù)。然后,將得出的仿真結(jié)果與最差情況分析仿真結(jié)果進(jìn)行比較。其中包括4個(gè)附錄。附錄A提供了有關(guān)微調(diào)基準(zhǔn)電壓源分布的見解。附錄B提供了LTspice中的高斯分布分析。附錄C提供了LTspice定義的蒙特卡羅分布的圖形視圖。附錄D提供關(guān)于編輯LTspice原理圖和提取仿真數(shù)據(jù)的說明。

本文介紹可以使用LTspice進(jìn)行的統(tǒng)計(jì)分析。這不是對(duì)6-sigma設(shè)計(jì)原則、中心極限定理或蒙特卡羅采樣的回顧。

公差分析

在系統(tǒng)設(shè)計(jì)中,為了保證設(shè)計(jì)成功,必須考慮參數(shù)容差約束。有一種常用方法是使用最差情況分析(WCA),在進(jìn)行這種分析時(shí),將所有參數(shù)都調(diào)整到最大容差限值。在最差情況分析中,會(huì)分析系統(tǒng)的性能,以確定最差情況的結(jié)果是否在系統(tǒng)設(shè)計(jì)規(guī)格范圍內(nèi)。最差情況分析的效力有一些局限性,例如:

u 最差情況分析要求確定哪些參數(shù)需要取最大值,哪些需要取最小值,以得出真實(shí)的最差情況的結(jié)果。

u 最差情況分析的結(jié)果往往會(huì)違反設(shè)計(jì)規(guī)范要求,致使必需選擇價(jià)格高昂的元件才能得到可接受的結(jié)果。

u 從統(tǒng)計(jì)學(xué)來說,最差情況分析的結(jié)果不能代表常規(guī)觀察到的結(jié)果;要研究展示最差情況分析性能的系統(tǒng),可能需要使用大量的被測(cè)系統(tǒng)。

進(jìn)行系統(tǒng)容差分析的另一種替代方法是使用統(tǒng)計(jì)工具來進(jìn)行元件容差分析。統(tǒng)計(jì)分析的優(yōu)點(diǎn)在于:得出的數(shù)據(jù)的分布能夠反映出在物理系統(tǒng)中通常需要測(cè)量哪些參數(shù)。在本文中,我們使用LTspice來仿真電路性能,利用蒙特卡羅和高斯分布來體現(xiàn)參數(shù)容差變化,并將其與最差情況分析仿真進(jìn)行比較。

除了提到的關(guān)于最差情況分析的一些問題外,最差情況分析和統(tǒng)計(jì)分析都能提供與系統(tǒng)設(shè)計(jì)相關(guān)的寶貴見解。關(guān)于如何在使用LTspice時(shí)使用最差情況分析的教程,請(qǐng)參見Gabino Alonso和Joseph Spencer撰寫的文章“LTspice: 利用最少的仿真運(yùn)行進(jìn)行最差情況的電路分析”。

蒙特卡羅分布

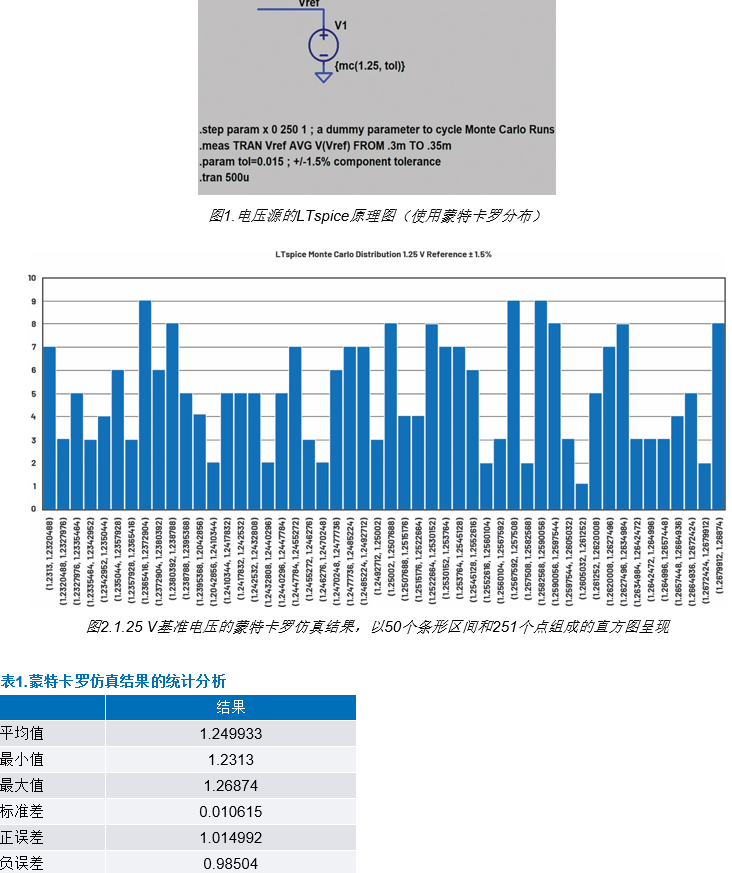

圖1顯示在LTspice中建模的基準(zhǔn)電壓,使用蒙特卡羅分布。標(biāo)稱電壓源為1.25 V,公差為1.5%。蒙特卡羅分布在1.5%的容差范圍內(nèi),定義251個(gè)電壓狀態(tài)。圖2顯示251個(gè)值的直方圖,圖中包含50個(gè)條形區(qū)間(bin)。表1表示與該分布相關(guān)的統(tǒng)計(jì)結(jié)果。

高斯分布

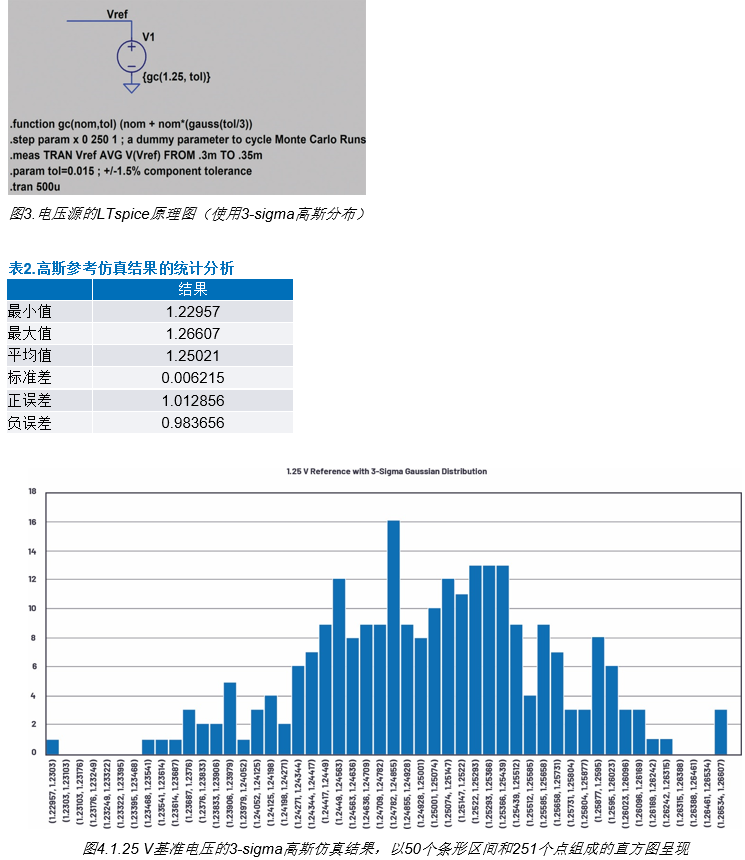

圖3顯示在LTspice中建模的基準(zhǔn)電壓,使用高斯分布。標(biāo)稱電壓源為1.25 V,容差為1.5%。蒙特卡羅分布在1.5%的容差范圍內(nèi),定義251個(gè)電壓狀態(tài)。圖4顯示251個(gè)值的直方圖,圖中包含50個(gè)條形區(qū)間(bin)。表2表示與該分布相關(guān)的統(tǒng)計(jì)結(jié)果。

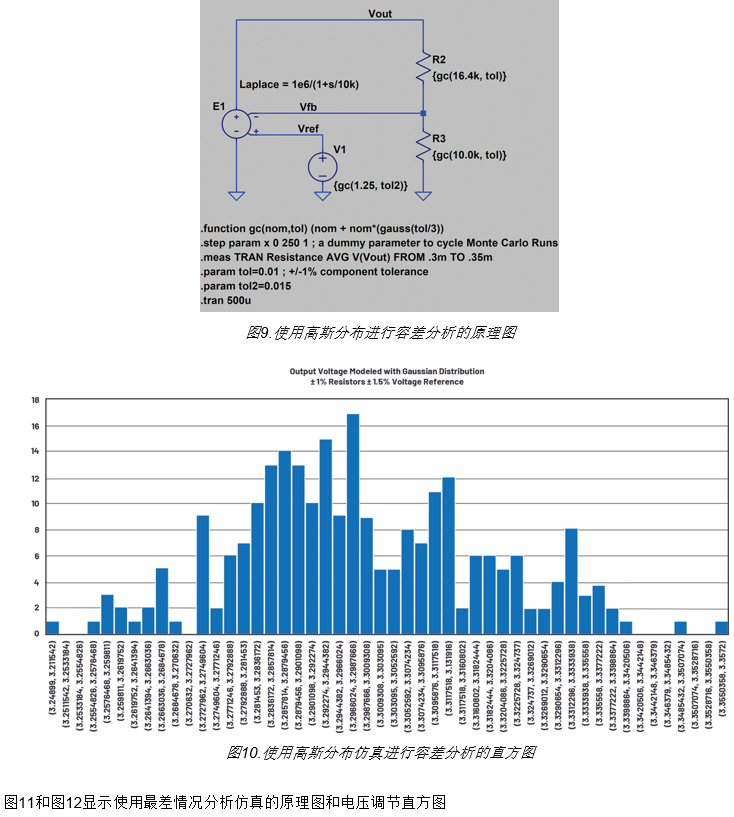

為了仿真電壓調(diào)節(jié)的容差分析,反饋電阻R2和R3的容差定義為1%,內(nèi)部基準(zhǔn)電壓的容差定義為1.5%。本節(jié)介紹三種容差分析方法:使用蒙特卡羅分布的統(tǒng)計(jì)分析、使用高斯分布的統(tǒng)計(jì)分析,以及最差情況分析(WCA)。

圖7和圖8顯示使用蒙特卡羅分布仿真的原理圖和電壓調(diào)節(jié)直方圖。

致謝

Simulations were conducted in LTspice.

仿真均在LTspice中完成。

作者簡(jiǎn)介

Steve Knudtsen是ADI公司的一名高級(jí)現(xiàn)場(chǎng)應(yīng)用工程師,工作地點(diǎn)在美國(guó)科羅拉多。他畢業(yè)于科羅拉多州立大學(xué),擁有電子工程學(xué)士學(xué)位,自2000年開始,一直在凌力爾特和ADI公司工作。