7月2日消息,Intel 12/13/14代酷睿都是P/E混合架構(gòu)設(shè)計(jì),俗稱大小核,整體布局是一致的,但是下一代的Arrow Lake,也就是酷睿Ultra 200系列(沒有15代酷睿了),將會(huì)迎來一次變革。

在目前的架構(gòu)中,P核、E核、GPU核顯、I/O控制器等億次都掛靠在一條環(huán)形總線(Ring Bug),其中P核是一個(gè)整體(最多8個(gè)),E核是另一個(gè)整體(最多16個(gè))。

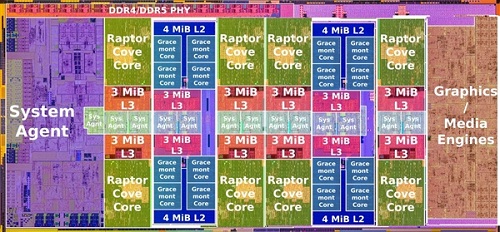

Arrow Lake(包括低功耗版Lunar Lake)的具體架構(gòu)圖現(xiàn)在是沒有的,但是有高手根據(jù)已知信息做了一個(gè)示意圖如下:

P核、E核不再是獨(dú)立的兩部分,而是混合在一起,每一個(gè)P核的旁邊是四個(gè)E核組成的集群,各有自己對應(yīng)的三級緩存。

環(huán)形總線通信的時(shí)候,先經(jīng)過一個(gè)P核,然后是四個(gè)E核,接下來是兩個(gè)P核,再往后是四個(gè)核,緊接著一個(gè)P核,如此往復(fù)。

這么做的好處看起來有兩個(gè),一是P核、E核之間的通信延遲會(huì)大大縮小,可以直接互通,而不需要間隔好幾站。

比如當(dāng)線程調(diào)度器需要分配不同負(fù)載給不同的P核、E核的時(shí)候,或者某個(gè)負(fù)載需要在P核、E核之間轉(zhuǎn)移的時(shí)候,效率會(huì)高得多。

二是改善散熱,更加均衡。

比如在游戲等高負(fù)載場景中,不會(huì)再集中使用P核而導(dǎo)致這部分區(qū)域集中發(fā)熱,E核部分則基本閑置。

當(dāng)然,具體的Arrow Lake架構(gòu)設(shè)計(jì),還需要等發(fā)布之后再挖掘更具體的信息。