是德科技推出 System Designer 和 Chiplet PHY Designer

2024-08-06

來(lái)源:是德科技

借助由仿真驅(qū)動(dòng)的虛擬合規(guī)性測(cè)試解決方案,采用更智能、更精簡(jiǎn)的工作流程,提高 PCIe 設(shè)計(jì)的工作效率

具有設(shè)計(jì)探索和報(bào)告生成能力,可加快小芯片的信號(hào)完整性分析以及 UCIe 合規(guī)性驗(yàn)證,從而幫助設(shè)計(jì)師提高工作效率,縮短新產(chǎn)品上市時(shí)間

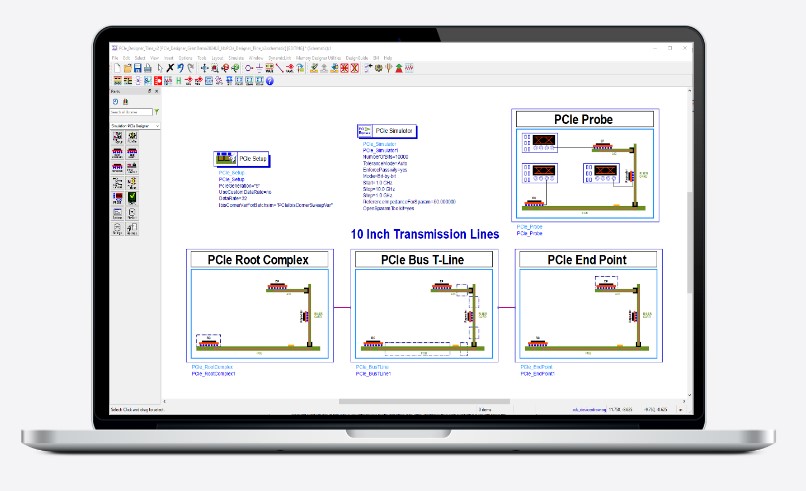

是德科技(Keysight Technologies, Inc.)宣布推出 System Designer for PCIe?,這是其先進(jìn)設(shè)計(jì)系統(tǒng) (ADS)軟件套件中的一款新產(chǎn)品,支持基于行業(yè)標(biāo)準(zhǔn)的仿真工作流程,可用于仿真高速、高頻的數(shù)字設(shè)計(jì)。System Designer for PCIe 是一種智能的設(shè)計(jì)環(huán)境,用于對(duì)最新的 PCIe Gen5 和 Gen6 系統(tǒng)進(jìn)行建模和仿真。是德科技還在改進(jìn)其電子設(shè)計(jì)自動(dòng)化平臺(tái),通過為現(xiàn)有的 Chiplet PHY Designer 工具增加新功能,評(píng)估 Chiplet 中芯片到芯片的鏈路裕度性能,并對(duì)電壓傳遞函數(shù) (VTF)是否符合相關(guān)參數(shù)標(biāo)準(zhǔn)進(jìn)行測(cè)量。

System Designer for PCIe 是一種智能的設(shè)計(jì)環(huán)境,用于對(duì)最新PCIe Gen5 和 Gen6 系統(tǒng)進(jìn)行建模和仿真

PCIe 憑借其高速數(shù)字傳輸能力、出色的可擴(kuò)展性和適應(yīng)能力,成為廣泛適用于電子行業(yè)各領(lǐng)域的重要通用接口標(biāo)準(zhǔn)。它的用途十分廣泛,范圍涵蓋從日常生活中的消費(fèi)電子設(shè)備到高性能計(jì)算和關(guān)鍵基礎(chǔ)設(shè)施系統(tǒng)中的專業(yè)應(yīng)用。

復(fù)雜的 PCIe 設(shè)計(jì)支持多鏈路和多通道系統(tǒng),主要涉及 RootComplex 和 End-Point 之間的復(fù)雜分析設(shè)置,有時(shí)還會(huì)包括中繼器。通常,設(shè)計(jì)人員需要投入大量時(shí)間準(zhǔn)備仿真工作,卻很容易出錯(cuò)。在仿真過程中,往往缺乏針對(duì)特定供應(yīng)商的算法建模接口(AMI)仿真模型,而實(shí)際上在設(shè)計(jì)周期的早期階段就需要使用這些模型來(lái)探索設(shè)計(jì)空間。設(shè)計(jì)師還需要確保他們的原型設(shè)計(jì)能夠在硬件制造開啟之前通過合規(guī)性測(cè)試。

能夠提升工作效率、優(yōu)化工作流程和提高合規(guī)性

System Designer for PCIe 能夠利用一種智能的設(shè)計(jì)環(huán)境,自動(dòng)設(shè)置多鏈路、多通道和多層級(jí)(PAM4)的 PCIe 系統(tǒng)。它簡(jiǎn)化了仿真設(shè)置步驟,縮短了從首次探索到發(fā)現(xiàn)更深層次問題的時(shí)間。

PCIe AMI 建模器支持 NRZ 和 PAM4 調(diào)制,能夠快速生成 PCIe 系統(tǒng)分析所需的 AMI 模型。AMI 模型生成器為設(shè)計(jì)師提供了一套向?qū)降?AMI 模型生成工作流程,可快速創(chuàng)建發(fā)射器(Tx)和接收器(Rx)模型。

采用經(jīng)過簡(jiǎn)化的、由仿真驅(qū)動(dòng)的虛擬合規(guī)性測(cè)試,使得設(shè)計(jì)人員能夠確保設(shè)計(jì)的質(zhì)量。高度集成的、由仿真驅(qū)動(dòng)的 PCIe 合規(guī)性測(cè)試工作流程可最大限度地減少設(shè)計(jì)迭代,縮短產(chǎn)品上市時(shí)間,從而降低設(shè)計(jì)成本。

Chiplet PHY Designer 的增強(qiáng)功能

Chiplet PHY Designer 是 EDA 行業(yè)首款針對(duì)通用小芯片互聯(lián)技術(shù) (UCIe)標(biāo)準(zhǔn)的仿真解決方案,有助于評(píng)估和預(yù)測(cè)芯片到芯片的鏈路裕量、用于通道合規(guī)性分析的 VTF 以及前向時(shí)鐘的性能。Chiplet PHY Designer 具有全新的設(shè)計(jì)探索和報(bào)告生成能力,可加速信號(hào)完整性分析和合規(guī)性驗(yàn)證,從而提高設(shè)計(jì)人員的工作效率,縮短新產(chǎn)品的上市時(shí)間。

是德科技 EDA 事業(yè)部高速數(shù)字產(chǎn)品線總監(jiān) Hee-Soo Lee 表示:“我們將持續(xù)拓展由標(biāo)準(zhǔn)驅(qū)動(dòng)的工作流程解決方案,從而為客戶提供支持。與同類產(chǎn)品相比,我們的高速數(shù)字產(chǎn)品組合能夠?yàn)樾盘?hào)完整性分析和合規(guī)性測(cè)試驗(yàn)證提供更準(zhǔn)確、更先進(jìn)的仿真軟件,在 EDA 行業(yè)處于領(lǐng)先地位。PCIe 和 UCIe 等數(shù)字標(biāo)準(zhǔn)對(duì)于保障電子系統(tǒng)的性能而言至關(guān)重要。設(shè)計(jì)師在工作過程中使用是德科技的 PCIe 和 UCIe 仿真解決方案,可以縮短開發(fā)周期,節(jié)省大量時(shí)間和成本。”

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<