近日,3D NAND 閃存和 3D DRAM 創(chuàng)新技術(shù)的領(lǐng)先開(kāi)發(fā)商 NEO Semiconductor 宣布推出其 3D X-AI芯片技術(shù),旨在取代高帶寬內(nèi)存 (HBM) 內(nèi)部的現(xiàn)有 DRAM 芯片,通過(guò)在 3D DRAM 中實(shí)現(xiàn) AI 處理來(lái)解決數(shù)據(jù)總線帶寬瓶頸。

NEO Semiconductor 稱,3D X-AI 可以減少 AI 工作負(fù)載期間 HBM 和 GPU 之間傳輸?shù)拇罅繑?shù)據(jù),這將徹底改變 AI 芯片的性能、功耗和成本,助力各類生成式 AI應(yīng)用。具體來(lái)說(shuō),采用NEO Semiconductor的3D X-AI技術(shù)的AI芯片可以實(shí)現(xiàn):

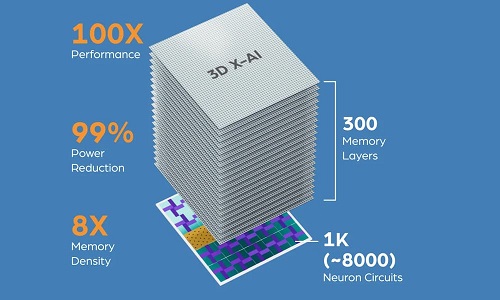

1、100 倍性能加速:包含 8,000 個(gè)神經(jīng)元電路,可在 3D 內(nèi)存中執(zhí)行 AI 處理;

2、功耗降低 99%:最大限度地減少將數(shù)據(jù)傳輸?shù)?GPU 進(jìn)行計(jì)算的需求,從而降低數(shù)據(jù)總線的功耗和發(fā)熱。

3、8 倍內(nèi)存密度:包含 300 個(gè)DRAM層,并允許通過(guò)類似 HBM 的堆疊,可以運(yùn)行更大的 AI 模型。

其實(shí)早在2023年5月,NEO Semiconductor就宣布將推出全球首款3D DRAM技術(shù),該技術(shù)的思路跟3D NAND Flash類似,都是通過(guò)堆棧層數(shù)來(lái)提高內(nèi)存容量,類似于3D NAND Flash芯片中的FBC浮柵極技術(shù),但增加一層Mask光罩就可以形成垂直結(jié)構(gòu),因此良率高,成本低,密度大幅提升。

NEO Semiconductor當(dāng)時(shí)就表示,其將推出的第一代3D X-DRAM就可以做到230層堆棧,核心容量128Gb,而當(dāng)前2D DRAM內(nèi)存的核心容量還在16Gb。

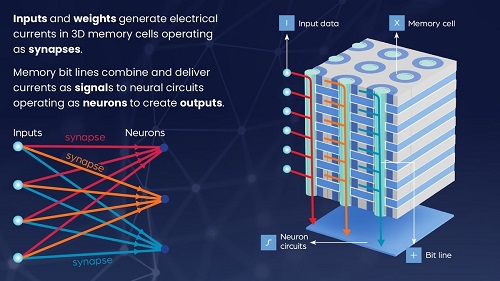

而此次NEO Semiconductor推出的 3D X-AI 芯片,就是在進(jìn)一步提升3D X-DRAM層數(shù)的基礎(chǔ)上加入了面向AI的神經(jīng)元電路。

具體來(lái)說(shuō),單個(gè) 3D X-AI 芯片包括 300 層容量為 128 Gb 的 3D DRAM 單元和一層具有 8,000 個(gè)神經(jīng)元的神經(jīng)回路。根據(jù)NEO Semiconductor公布的數(shù)據(jù),這可以支持每個(gè)芯片高達(dá) 10 TB/s 的 AI 處理吞吐量。如果使用 12 個(gè) 3D X-AI 芯片通過(guò)類似HBM的堆疊封裝, 則可以可實(shí)現(xiàn) 120 TB/s 的處理吞吐量,從而實(shí)現(xiàn) 100 倍的性能提升。

“由于架構(gòu)和技術(shù)效率低下,當(dāng)前的AI芯片浪費(fèi)了大量的性能和功率,”NEO Semiconductor的創(chuàng)始人兼首席執(zhí)行官Andy Hsu說(shuō)。“當(dāng)前的 AI 芯片架構(gòu)將數(shù)據(jù)存儲(chǔ)在 HBM 中,并依賴 GPU 執(zhí)行所有計(jì)算。這種分離的數(shù)據(jù)存儲(chǔ)和數(shù)據(jù)處理架構(gòu)使得數(shù)據(jù)總線成為不可避免的性能瓶頸。通過(guò)數(shù)據(jù)總線傳輸大量數(shù)據(jù)將會(huì)導(dǎo)致性能受限和非常高的功耗。3D X-AI 可以在每個(gè) HBM 芯片中執(zhí)行 AI 處理。這可以大大減少 HBM 和 GPU 之間傳輸?shù)臄?shù)據(jù),從而提高性能并顯著降低功耗。”

Network Storage Advisors總裁Jay Kramer表示:“3D X-AI技術(shù)的應(yīng)用可以加速新興AI用例的開(kāi)發(fā),并促進(jìn)新用例的創(chuàng)造。利用3D X-AI技術(shù)創(chuàng)建下一代優(yōu)化的AI芯片,將開(kāi)啟AI應(yīng)用創(chuàng)新的新時(shí)代。”