中文引用格式: 李祉怡,孫航,丁學偉,等. Virtuoso iQuantus Insight及Quantus Insight流程在FINFET先進工藝項目中加速后仿迭代的應用[J]. 電子技術應用,2024,50(8):26-31.

英文引用格式: Li Zhiyi,Sun Hang,Ding Xuewei,et al. Application of Virtuoso iQuantus Insight and Quantus Insight Flow on FINFET advance processes to accelerate post-simulation iteration[J]. Application of Electronic Technique,2024,50(8):26-31.

引言

半導體技術不斷發(fā)展,隨著集成度的提高,工藝節(jié)點不斷縮小,越來越多的設計進入了7 nm、5 nm甚至更低的節(jié)點,制造難度的成倍增長導致設計規(guī)則檢查(Design Rule Chek, DRC)越發(fā)復雜,寄生效應對集成電路設計性能的影響日益深遠。為考慮寄生效應對性能的影響,電路工程師會在設計中加上預設的寄生電阻電容進行前仿驗證。然而版圖中復雜的寄生通路使得從版圖設計提取得到的寄生網表中包含大量寄生RC參數,這些寄生RC與電路中預設的值往往存在不小的差距,復雜的寄生RC網絡使版圖設計后仿真的性能結果無法達到電路前仿預期的結果。

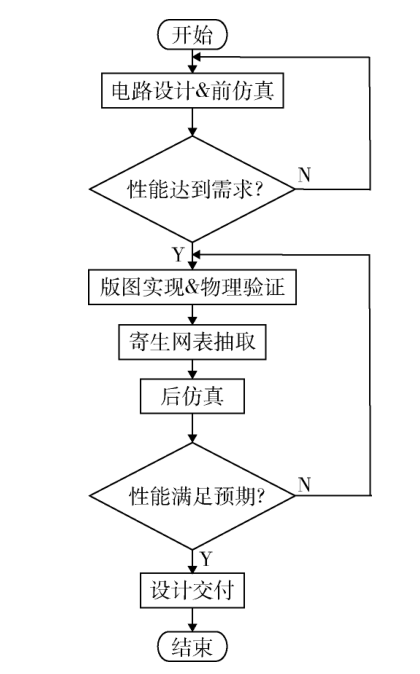

基于這一現狀,在從模擬電路設計到最終的設計交付過程中(如圖1所示),需要進行多次迭代,根據版圖設計后仿結果與電路設計前仿預期之間的差異,不斷修改電路設計、調整版圖并再次進行后仿,以逐步縮小前后仿差異,最終得到滿足性能要求的設計。

圖1 模擬電路設計流程圖

從圖1中可見,當后仿真得到的性能指標不滿足預期時,需要對版圖進行修改或者對電路設計進行修改,在這一步修改過程中,分析寄生網表中的寄生電阻電容數值能夠為修改提供指導,對寄生電阻電容的分析越清晰,電路及版圖設計的迭代修改就更加有的放矢,迭代效率更高。因此如何對版圖寄生網表進行分析以快速定位問題在集成電路設計迭代過程中至關重要。

本文將討論如何使用Cadence公司的Virtuoso iQuantus Insight (ViQI)/Quantus Insight (QI)工具對版圖寄生網表中的寄生電阻、寄生電容進行分析,直觀地查看關鍵信號路徑上的寄生數值是否滿足預期,了解寄生電阻、電容在各金屬層的分布情況并在版圖中對應位置上顯示,幫助設計師快速找到薄弱點,同時可通過寄生假設(What-if)功能對薄弱點寄生進行修改,確保電路設計及版圖設計可進行針對性的快速迭代。

本文詳細內容請下載:

http://forexkbc.com/resource/share/2000006117

作者信息:

李祉怡1,2,孫航1,2,丁學偉1,2,張慧麗3,曾義3

(1.深圳市中興微電子技術有限公司,廣東 深圳 518055;

2.移動網絡和移動多媒體技術國家重點實驗室,廣東 深圳 518055;

3.上海楷登電子科技有限公司,上海200120)