12 月 6 日消息,博通當(dāng)?shù)貢r間昨日宣布推出行業(yè)首個 3.5D F2F 封裝技術(shù) 3.5D XDSiP 平臺。3.5D XDSiP 可在單一封裝中集成超過 6000mm2 的硅芯片和多達(dá) 12 個 HBM 內(nèi)存堆棧,可滿足大型 AI 芯片對高性能低功耗的需求。

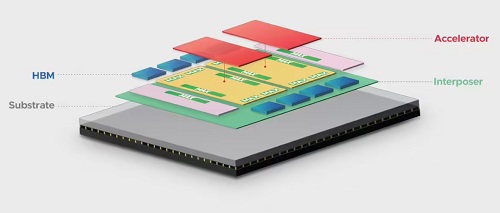

具體來看,博通的 3.5D XDSiP 在 2.5D 封裝之外還實現(xiàn)了上下兩層芯片頂部金屬層的直接連接(注:即 3D 混合銅鍵合),同時具有最小的電氣干擾和卓越的機械強度。

這一“面對面”的連接方式相比傳統(tǒng)“面對背”式芯片垂直堆疊擁有 7 倍的信號密度,最大限度減少了 3D 芯片堆棧中各組件間的延遲,相較平面芯片間 PHY 接口功耗大幅降低九成,實現(xiàn)了更小的中介層和封裝尺寸,從而在節(jié)省成本的同時還改善了大面積封裝的翹曲問題。

博通公司高級副總裁兼 ASIC 產(chǎn)品部總經(jīng)理 Frank Ostojic 表示:

先進(jìn)的封裝對于下一代 XPU 集群至關(guān)重要,因為我們已經(jīng)達(dá)到了摩爾定律的極限。

通過與客戶密切合作,我們在臺積電和 EDA 合作伙伴的技術(shù)和工具基礎(chǔ)上創(chuàng)建了 3.5D XDSiP 平臺。

通過垂直堆疊芯片元件,博通的 3.5D 平臺使芯片設(shè)計人員能夠為每個元件搭配合適的制造工藝,同時縮小中介層和封裝尺寸,從而顯著提高性能、效率和成本。

臺積電業(yè)務(wù)開發(fā)、全球業(yè)務(wù)資深副總經(jīng)理兼副共同營運長張曉強表示:

在過去幾年中,臺積電與博通緊密合作,將臺積電最先進(jìn)的邏輯制程和 3D 芯片堆疊技術(shù)與博通的設(shè)計專長相結(jié)合。

我們期待著將這一平臺產(chǎn)品化,以實現(xiàn) AI 創(chuàng)新和未來增長。

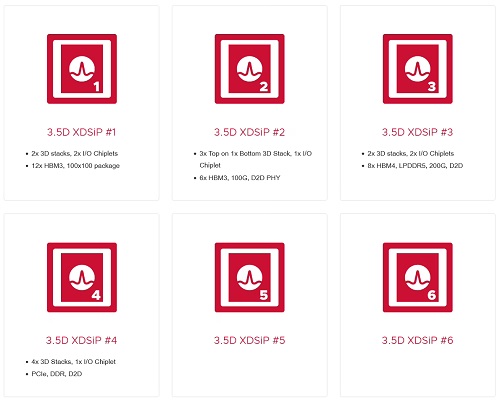

博通表示,其大多數(shù)“消費級 AI 客戶”已采用 3.5D XDSiP 平臺技術(shù),正在開發(fā)的 3.5D 產(chǎn)品已達(dá) 6 款,將于 2026 年 2 月開始生產(chǎn)出貨。其中富士通已明確將在其 2nm 制程 Arm 服務(wù)器處理器 FUJITSU-MONAKA 使用這一平臺。

▲ 博通官網(wǎng)展示的六個 3.5D XDSiP 案例富士通的 FUJITSU-MONAKA 應(yīng)該對應(yīng) #4