本文提供的解決方案可防止FPGA設(shè)計(jì)被拷貝,即使配置比特流被捕獲,也可以保證FPGA設(shè)計(jì)的安全性。這種安全性是通過在握手令牌由MAX II器件傳送給FPGA之前,禁止用戶設(shè)計(jì)功能來實(shí)現(xiàn)的。

基于SRAM的FPGA是易失器件,需要外部存儲(chǔ)器來存儲(chǔ)上電時(shí)發(fā)送給它們的配置數(shù)據(jù)。在傳送期間,配置比特流可能會(huì)被捕獲,用于配置其他FPGA。這種知識(shí)產(chǎn)權(quán)盜竊損害了設(shè)計(jì)人員的利益。

本文提供的解決方案可防止FPGA設(shè)計(jì)被拷貝,即使配置比特流被捕獲,也可以保證FPGA設(shè)計(jì)的安全性。通過在握手令牌由MAX II器件傳送給FPGA之前,禁止用戶設(shè)計(jì)功能來實(shí)現(xiàn)這種安全性。選用MAX II器件來產(chǎn)生握手令牌,這是因?yàn)樵撈骷哂蟹且资裕P(guān)電時(shí)可保持配置數(shù)據(jù)。而且,對(duì)于這種應(yīng)用,MAX II器件是最具成本效益的CPLD。本文還介紹了采用這種方案的一個(gè)參考設(shè)計(jì)。

硬件實(shí)現(xiàn)

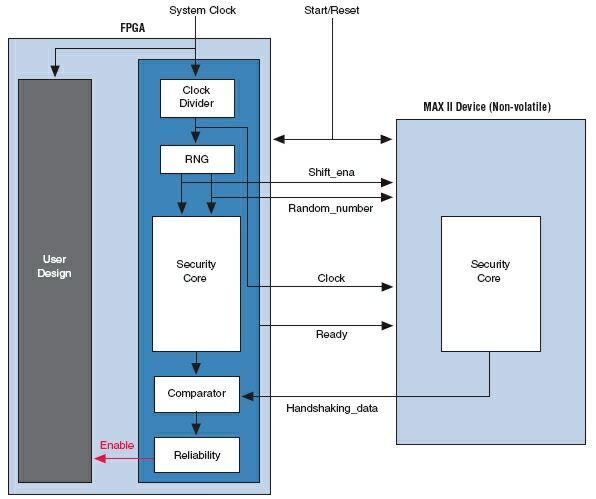

FPGA設(shè)計(jì)安全解決方案的硬件實(shí)現(xiàn)如圖1所示。MAX II器件產(chǎn)生連續(xù)的握手令牌,發(fā)送至FPGA,以使能用戶設(shè)計(jì)。FPGA和MAX II器件之間傳送5個(gè)信號(hào):clock、shift_ena、random_number、ready和handshaking_data。

一旦FPGA經(jīng)過配置后,它向MAX II器件提供連續(xù)時(shí)鐘。同時(shí)連接至FPGA和MAX II器件的啟動(dòng)/復(fù)位信號(hào)必須置位,以啟動(dòng)系統(tǒng)工作。FPGA中的隨機(jī)數(shù)發(fā)生器(RNG)開始為FPGA和MAX II器件產(chǎn)生初始計(jì)數(shù)值(每次上電或者啟動(dòng)/復(fù)位信號(hào)置位時(shí),僅向MAX II器件發(fā)送一次隨機(jī)數(shù))。隨機(jī)數(shù)準(zhǔn)備好后,shift_ena信號(hào)變?yōu)楦唠娖剑捎胷andom_number信號(hào),隨機(jī)數(shù)串行移位至MAX II器件。隨機(jī)數(shù)全部移位至MAX II器件后,ready信號(hào)置位,指示FPGA可以接收來自MAX II器件的握手令牌。

配置之后,由于Enable信號(hào)還是邏輯低電平,F(xiàn)PGA中的用戶設(shè)計(jì)功能被禁止。只有MAX II器件送出的握手令牌和FPGA內(nèi)部產(chǎn)生的數(shù)據(jù)相匹配,Enable信號(hào)才會(huì)置位,啟動(dòng)用戶設(shè)計(jì)功能。這兩個(gè)數(shù)據(jù)之間出現(xiàn)差異時(shí),Enable信號(hào)變?yōu)榈碗娖剑褂脩粼O(shè)計(jì)功能。MAX II器件中產(chǎn)生握手令牌和FPGA器件中產(chǎn)生數(shù)據(jù)的方法和過程相同。如果沒有正確的令牌,F(xiàn)PGA器件中的用戶設(shè)計(jì)功能被禁用。這樣,即使配置比特流被捕獲,也可以防止用戶設(shè)計(jì)被拷貝。

圖1:FPGA設(shè)計(jì)安全方案的硬件實(shí)現(xiàn)。

設(shè)計(jì)構(gòu)建模塊

FPGA的設(shè)計(jì)安全組成包括一個(gè)時(shí)鐘分頻器、隨機(jī)數(shù)發(fā)生器(RNG)、安全內(nèi)核、比較器和可靠性部分,而MAX II器件的設(shè)計(jì)安全組成只包括圖1所示的安全內(nèi)核。

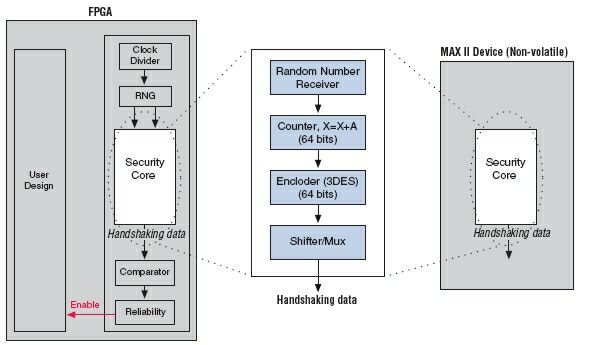

FPGA和MAX II器件使用的安全內(nèi)核相同,如圖2所示,由以下部分構(gòu)成:隨機(jī)數(shù)接收器、64位計(jì)數(shù)器、編碼器、移位器/復(fù)用器。

圖2:FPGA和MAX II器件的安全內(nèi)核。

1、時(shí)鐘分頻器FPGA中的時(shí)鐘分頻器用于從系統(tǒng)時(shí)鐘產(chǎn)生速率較低的時(shí)鐘,供給FPGA和MAX II器件的安全內(nèi)核使用。這是因?yàn)榘踩珒?nèi)核不需要運(yùn)行在非常高的頻率下。特別是當(dāng)系統(tǒng)運(yùn)行頻率非常高時(shí),時(shí)鐘分頻器的作用便比較顯著,否則,如果系統(tǒng)運(yùn)行頻率較低,可以不使用該分頻器。

2、隨機(jī)數(shù)發(fā)生器(RNG)每次啟動(dòng)/復(fù)位信號(hào)置位時(shí),RNG為64位計(jì)數(shù)器產(chǎn)生隨機(jī)初始值。然后,隨機(jī)數(shù)同時(shí)串行移位至FPGA和MAX II器件的安全內(nèi)核。參考設(shè)計(jì)采用32位RNG。

3、隨機(jī)數(shù)接收器隨機(jī)數(shù)接收器接收來自RNG的串行隨機(jī)數(shù),并按照正確的順序排列數(shù)據(jù),將其做為初始值送入64位計(jì)數(shù)器。

4、64位計(jì)數(shù)器64位計(jì)數(shù)器用于產(chǎn)生送入編碼器的64位數(shù)據(jù)。它是按照公式X=X+A進(jìn)行的一個(gè)簡(jiǎn)單加法器。X是一個(gè)64位初始值,而A是計(jì)數(shù)器遞增值,應(yīng)為質(zhì)數(shù)。初始值X來自RNG。參考設(shè)計(jì)中,32位來自RNG,其余32位由用戶在設(shè)計(jì)代碼中設(shè)置。A可以由用戶在設(shè)計(jì)代碼中設(shè)置。計(jì)數(shù)器輸出送入編碼器,對(duì)數(shù)據(jù)進(jìn)行加密。編碼器每次完成前一數(shù)據(jù)的加密后,計(jì)數(shù)器數(shù)值遞增。

5、編碼器編碼器可以采用任何難以破譯的加密標(biāo)準(zhǔn)。參考設(shè)計(jì)采用了三重?cái)?shù)據(jù)加密標(biāo)準(zhǔn)(3DES)。3DES編碼器的輸入和輸出是64位值,需要48個(gè)時(shí)鐘周期完成64位數(shù)據(jù)加密。

6、移位器/復(fù)用器移位器/復(fù)用器將編碼器輸出比特(16位)的一部分按照特定順序,存儲(chǔ)在寄存器中,編碼器準(zhǔn)備下一數(shù)值時(shí),將其串行移位至比較器。

7、比較器比較器將MAX II器件的編碼數(shù)據(jù)(握手令牌)與FPGA內(nèi)部產(chǎn)生的編碼數(shù)據(jù)逐位比較。如果MAX II器件和FPGA的數(shù)據(jù)相匹配,Enable信號(hào)置位,使能用戶設(shè)計(jì)功能。如果出現(xiàn)不匹配,請(qǐng)參見下面的可靠性保證一節(jié)。這種方式可以重復(fù)幾次,以產(chǎn)生更多的Enable信號(hào),使能用戶設(shè)計(jì)的不同部分。這種重復(fù)方式可以防止有人篡改FPGA比特流(這種可能性較低),致使Enable信號(hào)變?yōu)楦唠娖剑瑢?dǎo)致設(shè)計(jì)安全方案失效。

8、可靠性可靠性部分處理隨機(jī)比特錯(cuò)誤,這種錯(cuò)誤可能會(huì)導(dǎo)致系統(tǒng)停止工作。參考設(shè)計(jì)允許每10個(gè)時(shí)鐘周期中出現(xiàn)一次數(shù)據(jù)不匹配(這僅僅是一個(gè)例子,用戶可以根據(jù)實(shí)際應(yīng)用,修改該方法,達(dá)到最佳效果)。換句話說,如果10個(gè)時(shí)鐘周期中,數(shù)據(jù)不匹配不超過一次,Enable信號(hào)仍將保持高電平,系統(tǒng)繼續(xù)工作。如果10個(gè)時(shí)鐘周期中出現(xiàn)兩個(gè)錯(cuò)誤,那么,Enable信號(hào)變?yōu)榈碗娖剑褂脩粼O(shè)計(jì)功能。在啟動(dòng)/復(fù)位信號(hào)置位,復(fù)位系統(tǒng)前,系統(tǒng)停止工作。

圖3:不支持安全方案的FPGA設(shè)計(jì)。

用戶設(shè)計(jì)模塊

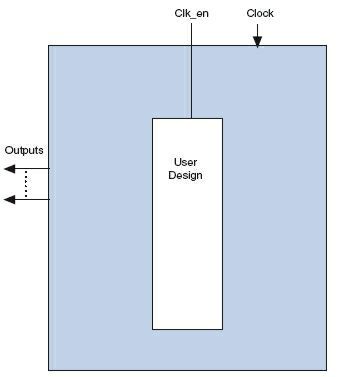

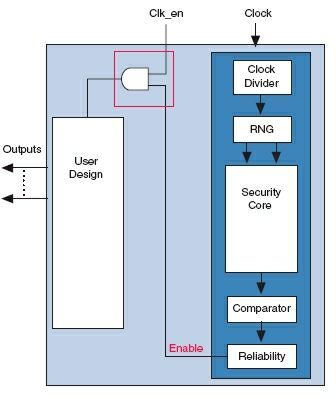

用戶設(shè)計(jì)模塊是真正的FPGA設(shè)計(jì)。來自安全模塊的Enable信號(hào)低電平時(shí)用于禁止用戶設(shè)計(jì)模塊。換言之,如果比較器發(fā)現(xiàn)MAX II器件和FPGA的數(shù)據(jù)不匹配,考慮到可靠性之后,將禁止用戶設(shè)計(jì)功能。

圖3是Enable信號(hào)低電平時(shí),禁止用戶設(shè)計(jì)功能的實(shí)例。圖3所示的FPGA用戶設(shè)計(jì)具有Clk_en輸入信號(hào),用于使能設(shè)計(jì)中的時(shí)鐘。只有Clk_en信號(hào)高電平時(shí),才啟動(dòng)設(shè)計(jì)功能。為實(shí)現(xiàn)設(shè)計(jì)安全方案,對(duì)用戶設(shè)計(jì)稍做修改(增加了一個(gè)AND邏輯門),這樣,當(dāng)來自安全模塊的Enable信號(hào)低電平時(shí),禁止用戶設(shè)計(jì),如圖4所示。

解決方案的安全性

上電時(shí),當(dāng)FPGA的配置比特流由外部存儲(chǔ)器傳送至FPGA時(shí),有可能被捕獲。使用捕獲的比特流來配置其他FPGA可以拷貝FPGA設(shè)計(jì)。

采用該解決方案,只有當(dāng)MAX II器件的握手令牌與FPGA內(nèi)部產(chǎn)生的數(shù)據(jù)相匹配時(shí),F(xiàn)PGA用戶設(shè)計(jì)才開始工作。由于被復(fù)制的設(shè)計(jì)在沒有握手令牌時(shí)無法工作,因此保證了FPGA設(shè)計(jì)的拷貝安全性。用于產(chǎn)生握手令牌的MAX II器件具有非易失特性,關(guān)電時(shí)可保持其配置。

解決方案的安全性依賴于MAX II器件產(chǎn)生的握手令牌。要破解該方案,需要拷貝MAX II器件產(chǎn)生的全部令牌比特流,或者計(jì)算出編碼器用于產(chǎn)生令牌的密鑰。由于每次上電時(shí),MAX II器件產(chǎn)生的握手令牌都不同,因此,拷貝全部比特流來破解該方案是不可能的。這在于采用了RNG,它在上電時(shí)產(chǎn)生不同的數(shù)值送給MAX II器件。

圖4:支持安全方案的FPGA設(shè)計(jì)。

如果采用了成熟的加密算法,那么破解編碼器使用的密鑰將非常困難。而且,無法從外部看到編碼器輸入數(shù)據(jù),只有一部分加密數(shù)據(jù)串行移出,更難實(shí)現(xiàn)純文本攻擊。純文本攻擊分析編碼器的輸入和輸出數(shù)據(jù),猜出密鑰,實(shí)施攻擊。因此,該解決方案保護(hù)了FPGA設(shè)計(jì)。

為保證該方案正常工作,安全模塊的時(shí)鐘應(yīng)和FPGA用戶設(shè)計(jì)的時(shí)鐘一致,如圖1所示。這樣可以防止有人在Enable信號(hào)高電平時(shí),禁用安全模塊時(shí)鐘。

本文小結(jié)

FPGA設(shè)計(jì)安全解決方案保護(hù)了Altera FPGA設(shè)計(jì)被拷貝(即使配置比特流被捕獲)。在MAX II器件通過握手令牌驗(yàn)證前,禁止FPGA用戶設(shè)計(jì),實(shí)現(xiàn)了該解決方案。只有握手令牌與FPGA內(nèi)部產(chǎn)生的數(shù)據(jù)匹配時(shí),F(xiàn)PGA用戶設(shè)計(jì)才被使能。該解決方案還保護(hù)了FPGA中的設(shè)計(jì)人員知識(shí)產(chǎn)權(quán)。