ARM7與FPGA相結(jié)合在工業(yè)控制和故障檢測(cè)中的應(yīng)用

工業(yè)控制中往往需要完成多通道故障檢測(cè)及多通道命令控制(這種多任務(wù)設(shè)置非常普遍),單獨(dú)的CPU芯片由于其外部控制接口數(shù)量有限而難以直接完成多路檢控任務(wù),故利用ARM芯片與FPGA相結(jié)合來擴(kuò)展檢控通道是一個(gè)非常好的選擇。這里介紹用Atmel公司ARM7處理器(AT91FR40162)和ALTERA公司的低成本FPGA芯片(CycloneII)結(jié)合使用完成多通道檢控任務(wù)的一種實(shí)現(xiàn)方法。

各部分功能簡(jiǎn)介

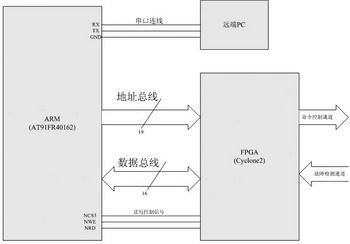

圖1為此系統(tǒng)的結(jié)構(gòu)連接框圖。如圖所示,ARM芯片與FPGA芯片之間通過數(shù)據(jù)總線、地址總線及讀寫控制線相連,而與終端PC則通過串口通信;FPGA與目標(biāo)設(shè)備通過命令控制總線和故障檢測(cè)總線相連。

圖1 系統(tǒng)結(jié)構(gòu)框圖

1 故障檢測(cè)和命令控制部分

故障檢測(cè):檢測(cè)通道的故障(正常)信號(hào)以高(低)電平方式指示,其一旦有故障產(chǎn)生就會(huì)保持高電平不變直到故障排除。針對(duì)這種特征,在ARM控制器端采用定時(shí)中斷循環(huán)查詢方式來判斷故障通道的狀態(tài)。定時(shí)中斷程序通過對(duì)ARM 地址總線在FPGA中進(jìn)行譯碼而順序鎖定被檢測(cè)通道的電平值,然后再經(jīng)數(shù)據(jù)總線傳回ARM進(jìn)行判斷,最后將判斷結(jié)果送至遠(yuǎn)程終端。采用主機(jī)查詢方式而不采用故障中斷方式出于兩個(gè)原因:一方面是通常控制芯片外部中斷源有限(多數(shù)為4個(gè)外部中斷源),對(duì)于多目標(biāo)中斷信號(hào)檢測(cè)顯然是困難的;另一方面,由于檢測(cè)通道或設(shè)備受到短時(shí)干擾而產(chǎn)生電平隨機(jī)反轉(zhuǎn),造成故障中斷觸發(fā),而中斷觸發(fā)后又無法在通道電平恢復(fù)正常時(shí)撤銷故障信號(hào),故而形成虛假報(bào)警。

命令控制:ARM芯片先判斷主控端發(fā)來的控制命令,然后通過地址總線和數(shù)據(jù)總線將命令狀態(tài)發(fā)送至經(jīng)FPGA地址譯碼鎖定的控制通道上。

2 ARM芯片與遠(yuǎn)程檢測(cè)控制終端通信

由于只存在命令和故障狀態(tài)信號(hào)的收發(fā),所以利用ARM的串口實(shí)現(xiàn)與遠(yuǎn)程PC的通信,通信標(biāo)準(zhǔn)選為RS232標(biāo)準(zhǔn)。不過,在ARM芯片上要先將TTL電平通過MAX232芯片轉(zhuǎn)換為RS232電平標(biāo)準(zhǔn),對(duì)于距離超過15m的全雙工通信,在發(fā)送接收兩端還要各加一對(duì)RS232轉(zhuǎn)RS422電平的轉(zhuǎn)換模塊,以增加通信距離。

3 FPGA內(nèi)部功能模塊說明

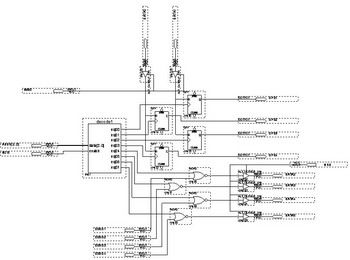

FPGA內(nèi)部檢測(cè)及控制電路結(jié)構(gòu)關(guān)系如圖2所示。

圖2 FPGA內(nèi)部邏輯結(jié)構(gòu)

ARM芯片的ADDR2~0位地址線和片選使能信號(hào)一同進(jìn)入譯碼器decode1進(jìn)行地址譯碼后產(chǎn)生8路輸出(FPGA內(nèi)部可設(shè)置一個(gè)最大輸出為256路的譯碼模塊,所以在實(shí)際應(yīng)用中可擴(kuò)展為更多通道),低4路用于命令發(fā)送通道,高4路用于故障檢測(cè)通道,讀寫使能信號(hào)控制數(shù)據(jù)總線。

ARM芯片接收到發(fā)送信號(hào)編碼命令時(shí),立即在串口接收中斷服務(wù)子程序中并送相應(yīng)地址(通道編號(hào))和數(shù)據(jù)(命令狀態(tài))到FPGA中。譯碼器有效輸出作為相應(yīng)通道D觸發(fā)器的鎖存時(shí)鐘,而數(shù)據(jù)狀態(tài)則被觸發(fā)器鎖定后作為所選通道的輸出完成相應(yīng)控制。

ARM芯片在定時(shí)中斷產(chǎn)生進(jìn)入服務(wù)程序后對(duì)所有檢測(cè)通道輪流查詢,查詢到有通道故障時(shí),故障信號(hào)結(jié)合選中通路信號(hào)經(jīng)與非運(yùn)算送往數(shù)據(jù)端口被讀取。

FPGA程序設(shè)計(jì)注意問題

1延時(shí)的配置

通過地址總線和數(shù)據(jù)總線進(jìn)行命令傳輸和故障檢測(cè)時(shí),F(xiàn)PGA是作為ARM芯片的普通外設(shè)來使用的。而ARM芯片對(duì)外設(shè)訪問的速度要遠(yuǎn)低于片內(nèi)存儲(chǔ)器,所以要在ARM中設(shè)置訪問的正確等待周期。ARM中提供的延時(shí)周期為0~7個(gè),通過調(diào)試即可找到外設(shè)合適的等待周期,此系統(tǒng)的等待周期根據(jù)實(shí)際測(cè)試設(shè)置為5個(gè),具體的配置方法見ARM程序說明。

2 讀寫使能信號(hào)的連接

從圖2中可以看出,寫使能信號(hào)NWE及讀使能信號(hào)NRD應(yīng)作為數(shù)據(jù)線(DATA0~5)的三態(tài)控制信號(hào)連接,即使在ARM芯片無其他外設(shè)時(shí)也不能缺省。因?yàn)锳RM的上電加載程序時(shí)間要長于同一系統(tǒng)上FPGA的程序配置時(shí)間,而FPGA的檢測(cè)及控制通道與ARM芯片的數(shù)據(jù)總線相連,F(xiàn)PGA加載完成后數(shù)據(jù)總線會(huì)存有相應(yīng)通道的邏輯電平值(不為三態(tài)),這就會(huì)導(dǎo)致ARM芯片在對(duì)片內(nèi)Flash芯片燒寫程序或上電加載程序時(shí)與FPGA沖突(數(shù)據(jù)被邏輯鎖定),造成無法正確定位操作對(duì)象而使讀寫失敗。

ARM配置及應(yīng)用程序說明

1 處理器的資源分配

● 存儲(chǔ)器

AT91FR40162內(nèi)嵌一個(gè)256KB的SRAM,1024K個(gè)16位字組成的Flash存儲(chǔ)器。SRAM通過內(nèi)部32位數(shù)據(jù)總線與ARM核相連,單周期訪問,F(xiàn)lash存儲(chǔ)器則通過外部總線訪問。

● 系統(tǒng)外圍

EBI:外部總線控制接口,EBI可尋址64MB的空間,通過8個(gè)片選線(NCS0~NCS3獨(dú)立)和24位地址線訪問外設(shè),地址線高4位與片選線(NCS4~7)復(fù)用,數(shù)據(jù)總線可配置成8/16位兩種模式與外設(shè)接口。

PIO:并口控制器,PIO控制32根I/O線,多數(shù)為復(fù)用引腳,可通過編程選擇為通用或?qū)S谩?/p>

AIC:先進(jìn)中斷控制器,實(shí)現(xiàn)片內(nèi)外圍中斷及4個(gè)外部中斷源中斷的管理,其外部中斷引腳與通用I/O復(fù)用。

● 用戶外圍

USART0~1:串口收發(fā)控制器,支持8個(gè)數(shù)據(jù)位的發(fā)送,可以進(jìn)行異步/同步傳輸選擇,其片外引腳與通用I/O復(fù)用。

TC:定時(shí)/計(jì)數(shù)器,可以產(chǎn)生定時(shí)中斷和計(jì)數(shù)功能,其片外引腳與通用I/O復(fù)用。

2 存儲(chǔ)器地址重映射后的空間分配

在CPU上電后,都會(huì)從地址0開始第一條指令代碼的執(zhí)行,而上電復(fù)位后0地址必須映射到NCS0片選所接的器件上,這里必須將NCS0連接到片內(nèi)Flash上以加載初始化程序和應(yīng)用程序。由于中斷和異常的入口地址是0~20H固定不變,它們的產(chǎn)生都是跳轉(zhuǎn)到0~20H之間相應(yīng)的地址取程序執(zhí)行,為了加快中斷響應(yīng),必須將0~20H地址映射到片內(nèi)RAM區(qū),所以在初始化的重映射命令執(zhí)行(EB1_RCR的RCB位置1)后,內(nèi)部RAM就映射到地址0,所有的中斷入口響應(yīng)和堆棧操作都被映射到在RAM區(qū)進(jìn)行。

由于重映射主要是用于Flash和片內(nèi)RAM的地址空間交換,所以片內(nèi)外圍接口(EBI、USART、TC)對(duì)應(yīng)的存儲(chǔ)器編程地址范圍在映射前后不發(fā)生改變,而訪問外設(shè)地址為重映射后所分配。重映射后地址分配如表1所示。

3 應(yīng)用接口的存儲(chǔ)器配置

EBI存儲(chǔ)器:在8個(gè)EBI片選存儲(chǔ)器(EBI_CSR0~EBI_CSR7)中設(shè)置外設(shè)訪問參數(shù)。其中,32位存儲(chǔ)器中包括數(shù)據(jù)總線寬度8(16)設(shè)置,等待狀態(tài)數(shù)目1~7個(gè)周期設(shè)置,等待使能(不是使能)設(shè)置,片選使能(不使能)設(shè)置。這里將FPGA作為外設(shè),使能NCS3(也可根據(jù)實(shí)際選擇其他空閑片選線),選擇總線寬度16,使能等待周期并設(shè)周期為5(根據(jù)調(diào)試選擇)。因默認(rèn)NCS0為加載Flash片選線,而Flash為16位信號(hào)、7個(gè)等待周期,故需在EBI_CSR0中選擇16位總線寬度、7個(gè)等待周期并使能NCS0。

AIC存儲(chǔ)器:AIC存儲(chǔ)器管理所有內(nèi)外部中斷,對(duì)此存儲(chǔ)器的正確初始化賦值才會(huì)打開相應(yīng)中斷。設(shè)定AIC工作參數(shù):應(yīng)用串口通信模式為異步模式,串口發(fā)送的數(shù)據(jù)位字符長度為8位,通信的波特率9600B/s,串口中斷優(yōu)先級(jí)為6(中斷優(yōu)先級(jí)由低到高0~7),接收發(fā)送通道使能。

TC存儲(chǔ)器:定時(shí)中斷存儲(chǔ)器需要設(shè)定定時(shí)長度為1s(每1s產(chǎn)生中斷進(jìn)行故障查詢),定時(shí)通道使能及軟件觸發(fā)模式,定時(shí)中斷優(yōu)先級(jí)設(shè)為1。

4 應(yīng)用程序說明

① 主程序

#define AT91C_BASE_EBI ((AT91PS_EBI) 0xFFE00000) //EBI基地址定義

int main()

{AT91F_EBI_OpenChipSelect (

AT91C_BASE_EBI, //地址指針

0x3, //片NCS3使能

0x30000000+0x3f39); //片選存儲(chǔ)器初始化

Usart_init();//初始化串口

timer_init();//初始化定時(shí)器

while(1){} //循環(huán)等待

}

ARM處理器在完成各寄存器初始化后進(jìn)入應(yīng)用主程序,在主程序中首先調(diào)用EBI接口使能函數(shù)來設(shè)置參數(shù):在程序中設(shè)置存儲(chǔ)器基地址值(0xFFE00000),片選設(shè)置0x3(NCS3使能),NCS3的存儲(chǔ)器初始化;調(diào)用USART控制器函數(shù)初始化串口:打開串口,串口收發(fā)通道初始化,設(shè)定串口通信速率;調(diào)用定時(shí)中斷函數(shù):打開定時(shí)中斷,設(shè)置定時(shí)中斷時(shí)間,設(shè)定觸發(fā)方式為軟件觸發(fā);最后進(jìn)入等待循環(huán)。

② 串口命令接收中斷服務(wù)程序

#define USART0_INTERRUPT_LEVEL 6//設(shè)置中斷優(yōu)先級(jí)為6

#define AT91C_US_USMODE_NORMAL AT91C_US_CHMODE_NORMAL//*設(shè)置通信模式(NORMAL定義為異步模式)*//

AT91PS_USART COM0=AT91C_BASE_US0;//設(shè)置COM0為收發(fā)口

char message[4];

// 控制端串口中斷通信程序 //

//*----------------------------------------------------------------------------*//

void Usart0_c_irq_handler(AT91PS_USART USART_pt)//串口中斷處理函數(shù)

{ volatile unsigned int *conp;unsigned int status;

int time;

volatile unsigned int i;

status = USART_pt->US_CSR &USART_pt->US_IMR;//給狀態(tài)寄存器賦初值

if ( status &AT91C_US_RXRDY)//接收通道寄存器判斷是否有數(shù)據(jù)

{

AT91F_US_DisableIt(USART_pt,AT91C_US_RXRDY);//關(guān)閉接收通道準(zhǔn)備好中斷

AT91F_US_EnableIt(USART_pt,AT91C_US_ENDRX);//打開接收結(jié)束中斷

AT91F_US_ReceiveFrame(USART_pt,(char*)(message),4);//調(diào)用接收數(shù)據(jù)數(shù)接收數(shù)據(jù)

}

if ( status &AT91C_US_ENDRX){

AT91F_US_DisableIt(USART_pt,AT91C_US_ENDRX); // 關(guān)閉接收器傳送結(jié)束中斷

{ if((message[0]^0xff)==message[1])//判斷接收代碼

{switch (message[0])

{case 0x31 : {conp=(volatile unsigned int*)(0x1+0x30000000);//OPE1使能

*conp=0x2;}; break;//0x31代碼送往OPE1端口

case 0x30 : {conp=(volatile unsigned int*)(0x2+0x30000000);//OPE2使能

*conp=0x1;}; break; // 0x30代碼送往OPE2端口

case 0x11 : {conp=(volatile unsigned int*)(0x3+0x30000000);//OPE3使能

*conp=0x2;};break;// 0x11代碼則往OPE3端口

case 0x10 : {conp=(volatile unsigned int*)(0x4+0x30000000);//OPE4使能

*conp=0x1;};break; //0x10代碼送往OPE4端口

default:break;}

}

}

以上程序?yàn)榇谥袛喾?wù)程序,各函數(shù)語句說明參見注釋。中斷級(jí)別設(shè)置為6(高于定時(shí)中斷),這樣使命令發(fā)送優(yōu)先于故障查詢(控制命令隨機(jī)出現(xiàn)而故障查詢總是循環(huán)進(jìn)行);接收緩沖區(qū)message[4]數(shù)組類型必須設(shè)為動(dòng)態(tài)分配,靜態(tài)數(shù)據(jù)分配會(huì)使處理器開辟數(shù)據(jù)緩沖區(qū)到Flash芯片中,從而引發(fā)在一個(gè)中斷處理程序中由于存取時(shí)間過長而導(dǎo)致串口收發(fā)超時(shí)的錯(cuò)誤。因?yàn)槠邢蓿渌绦虿辉僖灰粩⑹觥?/p>

在ARM應(yīng)用程序的編寫中,應(yīng)該盡量少的在主函數(shù)內(nèi)使用循環(huán)操作,主函數(shù)主要完成各接口控制器應(yīng)用初始化,因?yàn)橹骱瘮?shù)不間斷循環(huán)操作不但會(huì)增加功耗,而且長時(shí)間頻繁切換于中斷服務(wù)和主循環(huán)之間會(huì)造成程序運(yùn)行的不穩(wěn)定,所以能用定時(shí)中斷完成的循環(huán)操作盡量用中斷完成。

結(jié)語

ARM芯片控制功能結(jié)合FPGA靈活的多硬件接口模擬特性在工程上體現(xiàn)出的其獨(dú)特的優(yōu)勢(shì),已發(fā)展為一種流行的硬件架構(gòu)模式,隨著芯片功能的不斷強(qiáng)大,這種優(yōu)勢(shì)將使其用途更廣,對(duì)任務(wù)處理變得更加靈活高效。