CPU核心電壓Vcore波動(dòng)會(huì)影響CPU正常工作,Vcore過(guò)高,將導(dǎo)致CPU發(fā)熱量上升、壽命縮短甚至燒毀;反之,Vcore過(guò)低則可能引起數(shù)據(jù)損壞、死機(jī)、藍(lán)屏等故障。由于CPU集成度越來(lái)越高,制作工藝越來(lái)越精細(xì),CPU功耗越來(lái)越大,因此對(duì)供電系統(tǒng)提出了更高的要求。

一、自適應(yīng)電壓調(diào)節(jié)系統(tǒng)的結(jié)構(gòu)

早期主板普遍采用跳線或DIP開(kāi)關(guān)來(lái)設(shè)定CPU電壓,在安裝或更換CPU時(shí),需要根據(jù)CPU核心電壓對(duì)照主板說(shuō)明書,在主板上插拔挑線或撥動(dòng)DIP開(kāi)關(guān)進(jìn)行設(shè)置,稍有不慎就可能燒毀CPU和主板,十分危險(xiǎn)。為了解決這個(gè)問(wèn)題,Intel公司從Pentium Ⅱ開(kāi)始采用VID(Voltage Identification,電壓識(shí)別)技術(shù),VID技術(shù)是一種自適應(yīng)電壓調(diào)節(jié)技術(shù),采用這種技術(shù)后,主板供電電路可按CPU需要自動(dòng)設(shè)置供電電壓,不再需要進(jìn)行人工干預(yù)了。

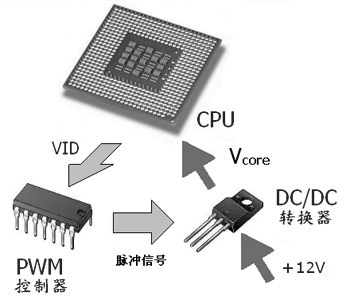

自適應(yīng)電壓調(diào)節(jié)技術(shù)的核心是在CPU上增加了若干個(gè)VID引腳,這些引腳輸出的編碼信號(hào)控制Vcore供電電路中的PWM(Pulse Width Modulation,脈寬調(diào)制)控制器。開(kāi)機(jī)后CPU將VID信號(hào)發(fā)送給PWM控制器,調(diào)整PWM控制器輸出脈沖信號(hào)的占空比,迫使DC/DC電路輸出的直流電壓與CPU的額定電壓相一致(圖1)。采用VID編碼后,VID的可編程特性使得用戶可以在BIOS中修改Vcore,一些主板制造商還編制了專門的工具軟件來(lái)顯示和修改Vcore值,給用戶帶來(lái)很大方便。

圖1 自動(dòng)設(shè)定原理

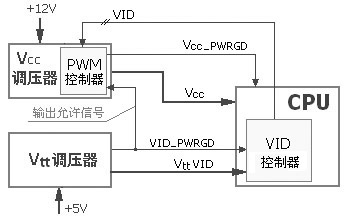

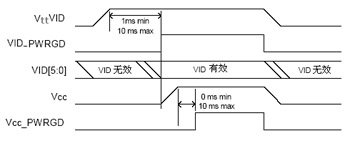

自適應(yīng)CPU供電電路的信號(hào)流程如圖2,電腦的主電源工作后,VttVR調(diào)壓器開(kāi)始工作,它一方面為CPU中的VID控制器提供電源,一方面輸出VID_PWRGD信號(hào)。VID_PWRGD信號(hào)同時(shí)送往CPU中的VID控制器和Vcc調(diào)壓器中的PWM控制芯片的對(duì)應(yīng)引腳,分別作為VID控制器和PWM芯片的輸出允許信號(hào)。VID控制器接收到VID_PWRGD信號(hào)這個(gè)信號(hào)后立即通過(guò)若干條信號(hào)線同時(shí)輸出各位VID信號(hào)。在VCC調(diào)壓器內(nèi),PWM控制器接收到VID信號(hào)后,向場(chǎng)效應(yīng)管驅(qū)動(dòng)器輸出脈沖信號(hào),啟動(dòng)DC/DC轉(zhuǎn)換功能,輸出Vcc電壓。待電壓穩(wěn)定后,PWM芯片向CPU提供VCC_PWRGD信號(hào),讓CPU開(kāi)始工作,如圖3。

圖2 供電系統(tǒng)原理框圖

圖3 自適應(yīng)電路時(shí)序圖

二、VID與Vcore的關(guān)系

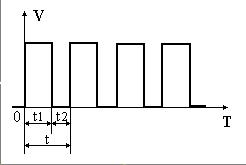

如前所述,CPU供給PWM控制器VID信號(hào),由PWM控制器控制DC/DC降壓電路,實(shí)現(xiàn)對(duì)輸出電壓的調(diào)整。實(shí)際上,PWM控制器輸出的脈沖信號(hào)的頻率(或周期t)通常維持不變,改變的只是脈沖的占空比t1/t的大小,如圖4。由于t不變,t1增大則輸出電壓高,t1減小則輸出電壓降低,t1不變則輸出電壓不變。電壓數(shù)值最終由MOSFET導(dǎo)通的時(shí)間所決定,輸出電壓V的大小與MOSFET的導(dǎo)通時(shí)間t1成正比。

圖4 PWM原理

在實(shí)際電路中,PWM采用移相式控制方式輸出脈沖信號(hào),控制MOSFET的導(dǎo)通和關(guān)斷。DC/DC電路輸出脈動(dòng)直流電,其紋波分量很大,須經(jīng)電容濾波后輸出平滑的直流電。當(dāng)濾波電容的容量足夠大時(shí),實(shí)際輸出的波形近似為一條直線。

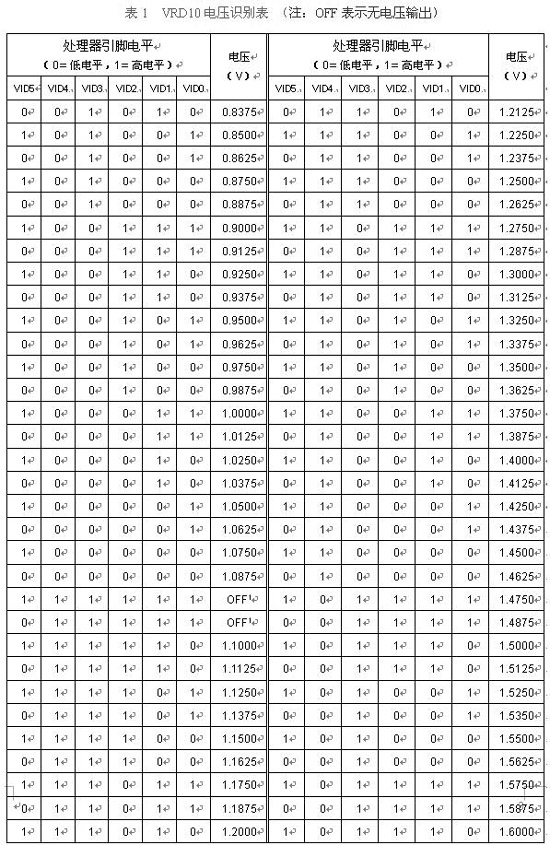

在自適應(yīng)供電系統(tǒng)中,t1是由CPU提供的VID編碼控制的。CPU的每個(gè)VID引腳有高電平和低電平兩種狀態(tài),分別代表“1”和“0”。“1”和“0”的不同組合構(gòu)成了VID編碼與輸出電壓之間的關(guān)系,見(jiàn)表1。由于VID編碼是不連續(xù)的,因此DC/DC轉(zhuǎn)換器實(shí)際上是一種階梯式降壓器(Step Down Regulator,簡(jiǎn)稱SDR)。

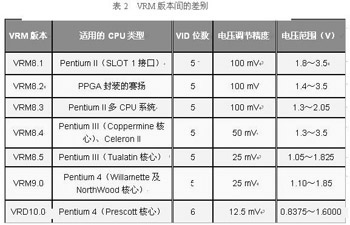

Intel為其各款處理器產(chǎn)品制定了相應(yīng)的電壓調(diào)節(jié)模塊(Voltage Regulation Model,VRM)設(shè)計(jì)規(guī)范,從Prescott核心微處理器開(kāi)始,電壓調(diào)節(jié)規(guī)范改用VRD(Voltage Regulation Down)來(lái)命名,各版本供電設(shè)計(jì)規(guī)范中VID位數(shù)、電壓調(diào)節(jié)精度和電壓調(diào)節(jié)范圍都各不相同,見(jiàn)表2。

VRD10.0將VID編碼從5位升級(jí)到6位,使得電壓調(diào)節(jié)精度從25mV提升到12.5mV,同時(shí)VRD10.0還提出了對(duì)VID進(jìn)行動(dòng)態(tài)調(diào)整的要求。

三、 動(dòng)態(tài)電壓調(diào)節(jié)技術(shù)

摩爾定律在芯片規(guī)模和性能方面的定義無(wú)比精確,但它卻忽視了芯片功耗帶來(lái)的制約:性能與功耗幾乎是同步提升,到2005年內(nèi)微處理器的最高功耗可能要攀升至150W,但目前采用的風(fēng)冷或水冷散熱技術(shù)所依托的熱傳導(dǎo)方式,都不可能將核心內(nèi)部的熱量迅速帶走,導(dǎo)致核心溫度過(guò)高,從而引發(fā)藍(lán)屏和死機(jī)故障。

動(dòng)態(tài)電壓調(diào)節(jié)(Dynamic Voltage adjusting,DVA)技術(shù)正是在這種背景下提出來(lái)的,其基本思想是根據(jù)CPU核心功率變化適時(shí)調(diào)節(jié)供電電壓值,最大限度地減少微處理器的發(fā)熱量。譬如,Prescott處理器的功率達(dá)到100W之多,這個(gè)功率是指CPU占用率100%時(shí)的情況,功耗大小隨CPU的忙碌程度的變化而變化,在系統(tǒng)空閑時(shí)CPU實(shí)際負(fù)荷要小很多。如果CPU輸出的VID維持不變,Vcore將超過(guò)CPU的實(shí)際需求,從而帶來(lái)不必要的電能浪費(fèi)。

另一方面,當(dāng)CPU處于十分忙碌的狀態(tài)時(shí),CPU和供電電路自身內(nèi)阻的電壓降會(huì)隨電流增加而增加,如果CPU輸出的VID維持不變,Vcore的實(shí)際數(shù)值將隨電流的增加而降低,電壓的降低勢(shì)必降低CPU的穩(wěn)定性,這是毋庸置疑的。

動(dòng)態(tài)自適應(yīng)電壓調(diào)節(jié)技術(shù)是一種智能供電技術(shù),與傳統(tǒng)的供電技術(shù)相比,動(dòng)態(tài)VID的優(yōu)勢(shì)體現(xiàn)在以下三個(gè)方面:

(1) 向CPU核心(die)提供穩(wěn)定的電壓,

提高了CPU工作穩(wěn)定性;

(2) 根據(jù)CPU工作情況,動(dòng)態(tài)地將供電電壓調(diào)節(jié)到某一時(shí)刻所需的最低水平,使供電電壓“恰好滿足需求”,實(shí)現(xiàn)最大限度的節(jié)能。

(3) 如果出現(xiàn)電流猛增的意外情況,VID控制器可以限制電流增加,保護(hù)CPU免于因發(fā)熱過(guò)多而燒毀。

為了配合CPU內(nèi)VID控制器實(shí)現(xiàn)CPU核心電壓的動(dòng)態(tài)調(diào)節(jié),Intel提出了柔性主板(Flexible Main Board,FMB)概念,并相繼推出了FMB 1.X和FMB2.X設(shè)計(jì)規(guī)范。為了能夠向CPU提供足夠的電力,降壓電路必須擁有功率足夠的MOSFET器件,同時(shí)在電流超標(biāo)時(shí)能及時(shí)采取措施讓電流降下來(lái),防止產(chǎn)生過(guò)多的熱量摧毀CPU和主板。

四、動(dòng)態(tài)電壓調(diào)節(jié)的實(shí)現(xiàn)

關(guān)于動(dòng)態(tài)電壓調(diào)整的策略,Intel在VRD10.0設(shè)計(jì)指南中說(shuō)得很明白:供電系統(tǒng)需要提供對(duì)動(dòng)態(tài)VID技術(shù)的支持,使得CPU中VID控制器通過(guò)VID總線每隔5ms對(duì)VID進(jìn)行一次調(diào)整,步長(zhǎng)(steps)為12.5mV,直到某一VID能夠滿足要求為止。那么,調(diào)整的根據(jù)是什么呢?

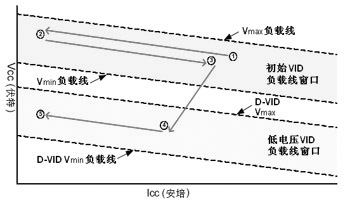

為了描述電壓調(diào)整的過(guò)程,首先定義下面3個(gè)負(fù)載曲線:

電壓最大值Vmax= VID – (RLL* ICC)

電壓典型值Vtype = VID – TOB – (RLL* ICC)

電壓最小值Vmin = VID – 2*TOB – (RLL* ICC)

式中RLL是傳輸線路等效電阻,這里是指電壓調(diào)整電路經(jīng)CPU插座(Socket)到CPU引腳之間的阻抗,包括導(dǎo)線電阻和CPU引腳與插座間的接觸電阻。由于RLL的存在,使得在主板輸出電壓與實(shí)際提供給CPU核心電壓之間存在一個(gè)落差。電壓跌落隨ICC的增加而線性增加,因此RLL是負(fù)載線的斜率。TOB是由制造誤差和溫度漂移等因素形成的誤差。

CPU中VID控制器采用“查表式”調(diào)節(jié)方式,圖5描述了處理器電壓調(diào)低的過(guò)程。處理器開(kāi)始時(shí)負(fù)荷比較高,隨著負(fù)荷的減輕,實(shí)際電壓隨ICC減少而升高,并停止執(zhí)行VID編碼(①→②);進(jìn)入狀態(tài)②之后,處理器經(jīng)過(guò)短暫延時(shí),以便為降低VID的操作做準(zhǔn)備,然后對(duì)VID編碼進(jìn)行初始化,導(dǎo)致電流拉回到狀態(tài)③;從狀態(tài)③到狀態(tài)④的變化,表示VID降低,從初始負(fù)載線窗口轉(zhuǎn)入較低的負(fù)載線窗口;從狀態(tài)④到狀態(tài)⑤表示在較低的VID負(fù)載窗口中,VCC隨ICC變化的瞬態(tài)過(guò)程。VID從低到高的調(diào)整過(guò)程與上述過(guò)程相反。

圖5 負(fù)載線

五、結(jié)語(yǔ)

供電系統(tǒng)的工作質(zhì)量關(guān)系到計(jì)算機(jī)系統(tǒng)的穩(wěn)定和安全,供電系統(tǒng)工作不好,就等于計(jì)算機(jī)患了心臟病。自適應(yīng)供電技術(shù)不僅方便了用戶,也增加了CPU供電的安全性;動(dòng)態(tài)供電使供電電壓恰好滿足CPU需求,不僅提高了系統(tǒng)穩(wěn)定性,還降低了CPU功耗。除此以外,作為一種智能化供電技術(shù),動(dòng)態(tài)供電技術(shù)對(duì)實(shí)現(xiàn)過(guò)流保護(hù)和過(guò)熱保護(hù)等保護(hù)功能也更加方便了。