兩個(gè)或多個(gè)微處理器一起工作來(lái)完成某個(gè)任務(wù)的系統(tǒng)稱為“多處理器系統(tǒng)”。傳統(tǒng)基于單片機(jī)的多處理器系統(tǒng)結(jié)構(gòu)復(fù)雜,可靠性差;而基于32位的嵌入式軟核處理器NiosII的SOPC(可編程片上系統(tǒng))多處理器系統(tǒng)解決方案,從根本上改變了多處理器系統(tǒng)的設(shè)計(jì)理念和方法。使用Altera公司的NiosII軟核處理器和SOPC Builder工具,可以快速地設(shè)計(jì)和建立共享資源的多處理器系統(tǒng)。多處理器系統(tǒng)一般用于工作站和使用分載(load-sharing)的復(fù)雜算法(稱為“對(duì)稱多處理器SMP”)的高端PC計(jì)算。對(duì)于大部分嵌入式系統(tǒng),當(dāng)SMP的開(kāi)銷太大時(shí),使用多個(gè)處理器執(zhí)行不同的任務(wù),實(shí)現(xiàn)不同的功能正引起越來(lái)越多的關(guān)注。Altera公司的FPGA為開(kāi)發(fā)非對(duì)稱的嵌入式多處理器系統(tǒng)提供了一個(gè)理想的平臺(tái)。為了提供理想的系統(tǒng)性能,使用SOPC Builder工具可以很容易地對(duì)硬件進(jìn)行修改和調(diào)整,從而很快完成不同配置系統(tǒng)的設(shè)計(jì)、編譯和評(píng)估[1]。

本文將對(duì)基于NiosII的SOPC多處理器系統(tǒng)的實(shí)現(xiàn)原理、設(shè)計(jì)流程和方法進(jìn)行詳細(xì)的討論。

1 NiosIl多處理器系統(tǒng)硬件設(shè)計(jì)

QuartusII 5.0及以上版本支持多處理器系統(tǒng)的創(chuàng)建和調(diào)試。多個(gè)NiosII處理器能夠有效地共享系統(tǒng)資源。由于SOPC Builder允許用戶輕松添加多個(gè)處理器到系統(tǒng)中,因此建立多處理器系統(tǒng)的難點(diǎn)已不再是硬件的排列和連接,而在于多個(gè)處理器的軟件設(shè)計(jì),使它們正常操作,相互之間不產(chǎn)生沖突。NiosII多處理器系統(tǒng)分為2類:一類是共享資源的多處理器系統(tǒng);另一類處理器相互獨(dú)立,之間不進(jìn)行信息交換。

2 Niosll多處理器系統(tǒng)的資源共享

資源共享是多處理器系統(tǒng)的強(qiáng)大功能,但必須仔細(xì)考慮所要共享的資源,以及不同處理器如何使用共享資源。

2.1 共享存儲(chǔ)器

在多處理器系統(tǒng)中最普遍的共享資源是存儲(chǔ)器。共享存儲(chǔ)器用于存放任何數(shù)據(jù),從指示處理器間通信狀態(tài)的簡(jiǎn)單標(biāo)志,到被多個(gè)處理器同時(shí)進(jìn)行計(jì)算的復(fù)雜數(shù)據(jù)結(jié)構(gòu)。

如果存儲(chǔ)器中包含不只一個(gè)處理器的程序代碼,那么每個(gè)處理器需要有不同的存儲(chǔ)地址。對(duì)于程序空間,處理器不能共享存儲(chǔ)器的同一區(qū)域。如果共享數(shù)據(jù)存儲(chǔ)器,則存儲(chǔ)器的數(shù)據(jù)需要從端口與共享存儲(chǔ)器的處理器的數(shù)據(jù)主端口連接。多處理器之間共享數(shù)據(jù)存儲(chǔ)器比共享指令存儲(chǔ)器困難,原因是數(shù)據(jù)存儲(chǔ)器可讀/寫(xiě)。如果某一處理器正在對(duì)共享存儲(chǔ)器的特定區(qū)域進(jìn)行寫(xiě)操作,而同時(shí)另一個(gè)處理器正在對(duì)同一區(qū)域進(jìn)行讀或?qū)懖僮鳎瑒t很可能出現(xiàn)數(shù)據(jù)錯(cuò)誤,至少使應(yīng)用程序出錯(cuò),甚至使系統(tǒng)崩潰。

共享存儲(chǔ)器的處理器需要一個(gè)機(jī)制來(lái)通知其他處理器何時(shí)正在使用共享資源,以便不受其他處理器的干擾。

2.2 硬件互斥核

NiosII處理器允許使用其硬件互斥核部件對(duì)共享資源進(jìn)行保護(hù)處理。這個(gè)硬件互斥核不是一個(gè)NioslI處理器內(nèi)部的部件,而是一個(gè)稱為Mutex的SOPC Builder組件。

互斥核也可看作一種共享資源,提供一個(gè)原子的“測(cè)試和置位”操作,處理器測(cè)試Mutex是否可行。如果可行,就在某個(gè)操作中獲取它。當(dāng)處理器結(jié)束與Mutex相關(guān)的共享資源使用時(shí),釋放該Mutex;此時(shí),另一個(gè)處理器可能獲取了Mutex,使用共享資源。互斥核在物理上并不能防止資源同時(shí)被多個(gè)處理器訪問(wèn)。運(yùn)行在處理器上的軟件必須被設(shè)計(jì)為在訪問(wèn)相關(guān)共享資源之前總是獲取Mutex的。

在大部分情況下,多個(gè)處理器之間應(yīng)該使用互斥核來(lái)保護(hù)共享資源。然而,也有一些不需要互斥核的,例如對(duì)于單方向或循環(huán)的消息緩沖隊(duì)列,此時(shí)只有一個(gè)處理器往存儲(chǔ)器的某個(gè)特殊位置寫(xiě)數(shù)據(jù)。

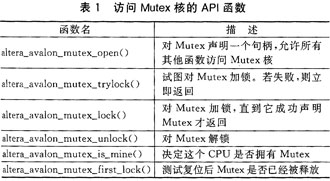

一般地,NiosII不支持多個(gè)處理器之間非存儲(chǔ)器外設(shè)的共享,NiosII硬件抽象層(HAL)庫(kù)也不支持。NiosIIHAL提供訪問(wèn)Mutex核的API函數(shù)如表1所列。

2.3 多處理器地址空間的重疊

在單處理器系統(tǒng)中,不允許多于一個(gè)的從外設(shè)具有相同的地址空間,原因是這將引起矛盾。然而,在多處理器系統(tǒng)中,只要外設(shè)被不同的處理器控制,那么不同的從外設(shè)就可以具有相同的基地址。

3 Niosll多處理器系統(tǒng)軟件設(shè)計(jì)

3.1 程序存儲(chǔ)器

在多處理器系統(tǒng)中,多個(gè)處理器可能使用同一個(gè)程序存儲(chǔ)器,每個(gè)處理器的程序必須存放在不同的位置。Ni-osII和SOPC Builder提供一個(gè)簡(jiǎn)單的存儲(chǔ)器分區(qū)模式,允許多個(gè)處理器在同一存儲(chǔ)器的不同區(qū)域運(yùn)行各自的軟件。分區(qū)模式使用處理器的異常地址,可以在SOPC Builder中進(jìn)行設(shè)置。NiosII IDE負(fù)責(zé)根據(jù)異常地址計(jì)算出不同代碼段鏈接的位置。如果2個(gè)不同的處理器被鏈接到同一存儲(chǔ)器,那么每個(gè)處理器的異常地址用來(lái)決定處理器軟件存放的基地址,其末地址由下一個(gè)異常地址或者存儲(chǔ)器的末地址決定。對(duì)于每個(gè)處理器,軟件有5個(gè)主要的代碼段需要被鏈接到存儲(chǔ)器中的固定地址,分別是:

·text 實(shí)際的可執(zhí)行代碼;

·rodata代碼段執(zhí)行時(shí)所使用的常量數(shù)據(jù);

·rwdata讀/寫(xiě)變量和指針;

·heap 動(dòng)態(tài)分配的存儲(chǔ)器;

·stack 函數(shù)調(diào)用參數(shù)和其他臨時(shí)數(shù)據(jù)。

在多處理器系統(tǒng)中,對(duì)于每個(gè)處理器,都希望使用連續(xù)的存儲(chǔ)區(qū)域存儲(chǔ)其所有的代碼段。在這種情況下,異常地址用來(lái)定義2個(gè)處理器之間代碼存放的分界。

值得注意的是,異常地址的低6位總是設(shè)置為0x20,因?yàn)槠屏?x0是NiosII的復(fù)位地址,所以異常地址必須位于其他位置。偏移量選擇為0x20,原因是它與一條指令的緩存行有關(guān)。0x20字節(jié)的復(fù)位代碼初始化指令緩存行,然后跳轉(zhuǎn)到系統(tǒng)的起始代碼處。

3.2 啟動(dòng)地址

在多處理器系統(tǒng)中,每個(gè)處理器必須從自己的存儲(chǔ)區(qū)域啟動(dòng)。為了從同一個(gè)非易失性存儲(chǔ)器中的不同區(qū)域啟動(dòng)多處理器,簡(jiǎn)單地設(shè)置每個(gè)處理器的復(fù)位地址為所期望的啟動(dòng)地址。在啟動(dòng)地址之間要留出足夠的空間存放啟動(dòng)代碼。

NiosII Flash Programmer能夠?qū)⒍鄠€(gè)處理器的啟動(dòng)代碼編程到一個(gè)Flash器件中。Flash Programmer根據(jù)每個(gè)處理器的復(fù)位地址計(jì)算Flash內(nèi)的編程地址。

3.3 NiosII IDE中多處理器系統(tǒng)的運(yùn)行和調(diào)試

NiosII IDE中包含許多幫助開(kāi)發(fā)多處理器系統(tǒng)軟件的工具,最重要的是具有對(duì)多處理器同時(shí)進(jìn)行在片涮試的能力。在多處理器系統(tǒng)上,多個(gè)debug(調(diào)試)可同時(shí)運(yùn)行;每個(gè)處理器可以單獨(dú)暫停和恢復(fù),也可以單獨(dú)設(shè)置每個(gè)處理器的斷點(diǎn)。某個(gè)處理器停在一個(gè)斷點(diǎn)處,并不影響其他處理器的操作。每個(gè)debug通道也可以單獨(dú)打開(kāi)和停止。在NiosII IDE中,利用一項(xiàng)稱為“處理器集合(mul-tiprocessor collections)”的功能,一個(gè)操作就可以打開(kāi)多個(gè)處理器的debug通道。multiprocessor collections是被連接在一個(gè)配置名字下的每個(gè)處理器的debug配置組。使用multiprocessol collections的好處是無(wú)論何時(shí)打開(kāi)collections,NiosII IDE都可以打開(kāi)每個(gè)debug通道,而不用手動(dòng)打開(kāi)。也可以用一個(gè)操作停止multiprocessor col-lections,但是同時(shí)暫停和恢復(fù)multiprocessor collections目前不支持。

multiprocessor collections的打開(kāi)和停止不是同時(shí)的,這意味著在collections中的處理器不能在同一個(gè)時(shí)鐘周期開(kāi)始執(zhí)行代碼。事實(shí)上,不同處理器的啟動(dòng)可能有幾秒的延遲。multiprocessor collections的目的是方便打開(kāi)多處理器系統(tǒng)的debug通道,而不是為了同步處理器。如果需要在較短的時(shí)間內(nèi)啟動(dòng)多個(gè)處理器,則需要構(gòu)建單獨(dú)的硬件和軟件機(jī)制。

4 NiosII多處理器系統(tǒng)設(shè)計(jì)實(shí)例

下面將利用SOPC Builder建立一個(gè)基于標(biāo)準(zhǔn)模板的3處理器、共享片上存儲(chǔ)器的NiosII系統(tǒng),之后在NiosII IDE中為每個(gè)處理器建立一個(gè)軟件工程。系統(tǒng)功能是:3個(gè)CPU的軟件將產(chǎn)生要顯示的消息。使用硬件牛互斥核將所產(chǎn)生的不同消息放在共享的消息緩沖區(qū)中。cpul將連續(xù)檢查緩沖區(qū)中的新消息,如果發(fā)現(xiàn)新消息,就通過(guò)jtag_uart顯示出來(lái)。

實(shí)例的開(kāi)發(fā)環(huán)境是QuartuslI 5.0或以上版本[2],開(kāi)發(fā)套件CycloneII Edition和nioslI_cycloneII_2c35開(kāi)發(fā)板。

4.1 創(chuàng)建硬件系統(tǒng)

在標(biāo)準(zhǔn)硬件實(shí)例standard.qp的設(shè)計(jì)基礎(chǔ)上,增加2個(gè)處理器、2個(gè)定時(shí)器和1個(gè)硬件互斥核組件;另外增加1個(gè)消息緩存區(qū)message_buffer_ram(片上RAM),用作3個(gè)處理器的消息緩存區(qū)。按如下步驟連接共享資源:

① 使用連接矩陣,將SDRAM連接到每個(gè)處理器的指令和數(shù)據(jù)主端口。允許3個(gè)處理器訪問(wèn)SDRAM。

② 將ext_ram_bus蓮接到每個(gè)處理器的指令和數(shù)據(jù)主端口。允許3個(gè)處理器訪問(wèn)外部RAM和Flash。

③ 將message_buffer_ram連接到每個(gè)處理器數(shù)據(jù)主端口。允許3個(gè)處理器訪問(wèn)該存儲(chǔ)器。

④ 去除在message_buffer_ram和cpul指令主端口之間的缺省連接。

⑤ 選擇System→Auto-Assign Base Addresses,為每個(gè)外設(shè)分配一個(gè)唯一的基地址。

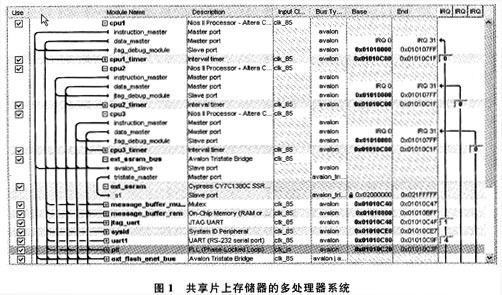

完成以上操作后,系統(tǒng)配置如圖1所示。3個(gè)處理器的數(shù)據(jù)主端口與共享存儲(chǔ)器的同一從端口連接。因?yàn)閏pul、cpu2和cpu3在物理上能夠同時(shí)將數(shù)據(jù)寫(xiě)到共享存儲(chǔ)器中,軟件必須仔細(xì)設(shè)計(jì)以保證存儲(chǔ)在共享存儲(chǔ)器上數(shù)據(jù)的完整性。注意:圖1所示的系統(tǒng)配置中,只有cpul的數(shù)據(jù)主端口與jtag_uart相連。

最后,為3個(gè)CPU設(shè)置復(fù)位和異常地址,創(chuàng)建和編譯系統(tǒng),并下載FPGA的設(shè)計(jì)文件.sof文件到開(kāi)發(fā)板。

4.2 為多處理器系統(tǒng)創(chuàng)建軟件

在NiosII IDE[3]環(huán)境下,為3個(gè)處理器系統(tǒng)分別創(chuàng)建6個(gè)軟件工程,為每個(gè)處理器創(chuàng)建一個(gè)應(yīng)用工程和一個(gè)系統(tǒng)庫(kù)工程。之后對(duì)軟件工程進(jìn)行編譯、運(yùn)行和調(diào)試。

軟件使用硬件Mutex共享一個(gè)消息緩存區(qū)。3個(gè)處理器分別寫(xiě)消息到消息緩存區(qū)(count)且循環(huán)加1。cpul讀消息且通過(guò)jtag_uart顯示消息。每個(gè)處理器運(yùn)行同樣的C文件,但處理器的操作稍有不同。這是通過(guò)使用Ni-osII的cpuid實(shí)現(xiàn)的。在NioslI處理器系統(tǒng)中,某個(gè)處理器通過(guò)寫(xiě)其cpuid控制寄存器的值到Mutex寄存器的OWNER域來(lái)對(duì)Mutex加鎖。cpuid寄存器保持一個(gè)靜態(tài)值,在多處理器系統(tǒng)中,該值唯一地識(shí)別一個(gè)處理器,且在系統(tǒng)創(chuàng)建時(shí)確定。軟件執(zhí)行某個(gè)處理器的函數(shù)時(shí),首先檢查處理器的cpuid,如果cpuid正確,則執(zhí)行相應(yīng)函數(shù)。工程中的文件為hello_world_multi.c,其中將信息寫(xiě)入緩沖區(qū)的功能由以下程序段實(shí)現(xiàn):

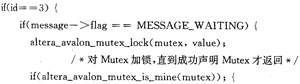

如果將信息從jtag_uart輸出,那么程序首先判斷id是否等于3。因?yàn)橛布O(shè)計(jì)時(shí),只有cpul與jtag_uart相連,而cpul的id的值為3(在系統(tǒng)創(chuàng)建時(shí)確定),cpu2、cpu3的id分別為1和2,且id的值等于cpuid控制寄存器的值加1,可在NiosII IDE環(huán)境下讀取cpuid控制寄存器的內(nèi)容。其信息輸出的程序如下:

在System Library屬性中,第1個(gè)工程選擇jtag_uart為stdin、stderr和stdout,選擇cpul_timer為the Systemclock timer;第2個(gè)工程選擇cpu2_timer為System clocktimer,驗(yàn)證stdin、stderr和stdout為null,因?yàn)檫@個(gè)處理器不與jtag_uart連接;第3個(gè)工程選擇cpu3_timer為Systemclock timer,其余同工程2。驗(yàn)證這3個(gè)工程的SDRAM被選擇為Program memory、Read-only data memory、Read/write data memory、Heap memory和Stack memory。

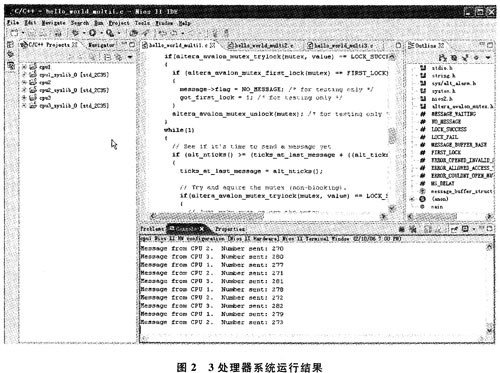

分別經(jīng)編譯、下載、運(yùn)行后,在終端上顯示這3個(gè)處理器產(chǎn)生的消息,如圖2所示。

結(jié) 語(yǔ)

結(jié)果表明,3處理器系統(tǒng)通過(guò)硬件互斥核,實(shí)現(xiàn)了存儲(chǔ)器的共享。在此實(shí)例的基礎(chǔ)上,按同樣的方法添加處理器及相應(yīng)的硬件組件,并開(kāi)發(fā)相關(guān)應(yīng)用軟件,即可實(shí)現(xiàn)滿足不同需求的多處理器系統(tǒng)。