在模擬/數(shù)字轉(zhuǎn)換中,最理想的是能夠利用最少導(dǎo)線便可將數(shù)字?jǐn)?shù)據(jù)進(jìn)行下傳。有時(shí)可以采用輸出串行數(shù)據(jù)的模擬/數(shù)字轉(zhuǎn)換器,這當(dāng)然是解決這個(gè)問(wèn)題的一個(gè)辦法。但這個(gè)解決方案本身存在問(wèn)題需要解決。可以輸出串行數(shù)據(jù)的模擬/數(shù)字轉(zhuǎn)換器往往受制于傳統(tǒng)串行總線的內(nèi)部結(jié)構(gòu),以至傳輸速度受到一定的限制。由于這類串行總線經(jīng)常進(jìn)行單端信號(hào)傳輸,因此很易產(chǎn)生電磁干擾,影響鄰近電路的穩(wěn)定性。鄰近電路產(chǎn)生的共模噪音也會(huì)影響串行總線的穩(wěn)定性,令數(shù)據(jù)傳輸出現(xiàn)誤碼。

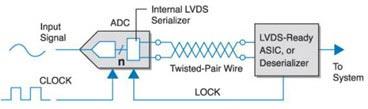

克服這些問(wèn)題的其中一個(gè)辦法是采用低電壓差分信號(hào) (LVDS) 數(shù)據(jù)總線。圖 1 是其中一種模擬/數(shù)字轉(zhuǎn)換器的結(jié)構(gòu)框圖,帶有LVDS 輸出信號(hào),驅(qū)動(dòng)專用集成電路或解串器。

圖 1:結(jié)構(gòu)框圖

圖中的模擬/數(shù)字轉(zhuǎn)換器按照 LVDS 信號(hào)格式輸出串行數(shù)據(jù)流。接收端則利用可支持 LVDS 的專用集成電路或解串器將 n 位的輸出復(fù)原。

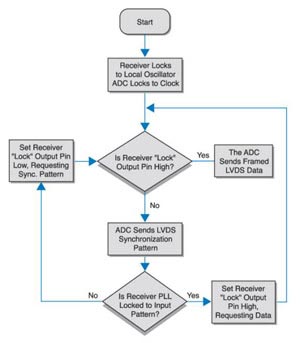

通電啟動(dòng)時(shí),模擬/數(shù)字轉(zhuǎn)換器與接收器會(huì)進(jìn)入一個(gè)兩步驟的啟動(dòng)過(guò)程。這個(gè)啟動(dòng)過(guò)程是指確保每一芯片內(nèi)不同鎖相環(huán)路都能實(shí)現(xiàn)同步操作的過(guò)程。首先,接收器根據(jù)振蕩器提供的脈沖頻率自行鎖定。模擬/數(shù)字轉(zhuǎn)換器的鎖相環(huán)路根據(jù) CLKIN 自行鎖定。然後,模擬/數(shù)字轉(zhuǎn)換器輸出一列數(shù)據(jù),這列數(shù)據(jù)的排列方式稱為 SYNC 模式,其排列模式如下:任何數(shù)目的 "1"之后必定有相同數(shù)目的 "0",并按數(shù)據(jù)輸出速度計(jì)時(shí)。接收器內(nèi)的鎖相環(huán)路按照這個(gè) SYNC 模式鎖定,并將 "LOCK"信號(hào)傳送回模擬/數(shù)字轉(zhuǎn)換器,通知模擬/數(shù)字轉(zhuǎn)換器接收器已鎖定,并隨時(shí)準(zhǔn)備接收任何傳來(lái)的數(shù)據(jù)。輸出數(shù)據(jù)由以下三個(gè)部分組成:數(shù)值永遠(yuǎn)是 "1"的 "起始位"、n 位的數(shù)據(jù)、以及數(shù)值永遠(yuǎn)是 "0"的 "終止位"。圖 2 顯示數(shù)據(jù)傳送的大概流程。

圖 2:流程

因此這個(gè)幀是由 n+2 位的數(shù)據(jù)所組成,而數(shù)據(jù)流頻率則是 (n+2) x fsample。接收器的鎖相環(huán)路只要一直處于鎖定狀態(tài),便可連續(xù)接收數(shù)據(jù)。若鎖相環(huán)路滑出鎖定范圍之外,LOCK 線路便會(huì)設(shè)定為低態(tài),而模擬/數(shù)字轉(zhuǎn)換器又會(huì)再次收到提供同步操作模式的請(qǐng)求。

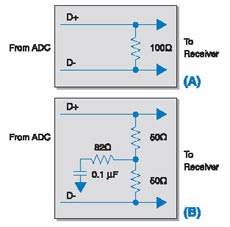

模擬/數(shù)字轉(zhuǎn)換器的輸出驅(qū)動(dòng)器可提供恒流源,驅(qū)動(dòng) 100W 終端的雙絞線、印刷電路上帶狀線或微帶線。圖 3 是兩種典型置于接收器附近的終端電路。

圖3:典型的終端電路

圖3 A 是一幅簡(jiǎn)單的終端配置。模擬/數(shù)字轉(zhuǎn)換器的線路終端設(shè)有電阻,有助減低任何可能產(chǎn)生的反射。這個(gè)電阻也是恒流源電流產(chǎn)生輸出信號(hào)所需的負(fù)載。圖 3B 是另一簡(jiǎn)單的終端配置,依據(jù)需要使用共模電阻,以減低電纜上的共模。這個(gè)方法較為少用。只要采用差分信號(hào)格式,模擬/數(shù)字轉(zhuǎn)換器及解串器之間的導(dǎo)線數(shù)便可減至最少,并確保產(chǎn)生的磁場(chǎng)緊密局限在傳輸線路的附近。這樣可減低這些線路的電磁干擾,以免影響鄰近的電路。

美國(guó)國(guó)家半導(dǎo)體推出可提供 LVDS 輸出的模擬/數(shù)字轉(zhuǎn)換器,方便精簡(jiǎn)系統(tǒng)設(shè)計(jì),滿足數(shù)據(jù)總線的嚴(yán)格要求。