時(shí)分同步碼分多址(Time Division-Synchronous Code Division Multiple Access)是中國(guó)自主研發(fā)的第三代蜂窩通信標(biāo)準(zhǔn),也是兩個(gè)3GPP" title="3GPP">3GPP時(shí)分蜂窩標(biāo)準(zhǔn)之一(另一個(gè)是TD-CDMA)。TD-SCDMA" title="TD-SCDMA">TD-SCDMA與同類標(biāo)準(zhǔn)不同之處在于碼片速率低,并且上行鏈路" title="鏈路">鏈路提供時(shí)間同步傳輸能力。中國(guó)目前在這一標(biāo)準(zhǔn)的研發(fā)方面已經(jīng)進(jìn)行了大量投資,到目前為止已經(jīng)成功建設(shè)了多個(gè)測(cè)試和試驗(yàn)網(wǎng)絡(luò)。一旦中國(guó)頒發(fā)3G牌照,相信TD-SCDMA網(wǎng)絡(luò)會(huì)很快實(shí)現(xiàn)部署。?

TD-SCDMA的突出系統(tǒng)特點(diǎn)

TD-SCDMA系統(tǒng)有兩大突出特點(diǎn):首先,考慮到其上行傳輸(手機(jī)到基站)的時(shí)間同步特點(diǎn),被稱為聯(lián)合檢測(cè)(joint-detection)的高級(jí)信號(hào)處理技巧在基站恢復(fù)每個(gè)用戶的傳輸。在理想情況下,利用聯(lián)合檢測(cè)可以完全消除同一小區(qū)內(nèi)來(lái)自其它用戶的干擾,因此與其它異步匹配檢測(cè)技術(shù)相比,可以提高系統(tǒng)容量。第二個(gè)突出特點(diǎn)是使用自適應(yīng)波束成形(beam forming)來(lái)提高信噪比并減輕干擾。?

利用賽靈思 FPGA 可以高效實(shí)現(xiàn)聯(lián)合檢測(cè)功能,但本文的重點(diǎn)基于FPGA的成本經(jīng)濟(jì)的TD-SCDMA數(shù)字前端(DFE)解決方案。波束成形需要在基站使用多個(gè)天線(通常為六至八個(gè)天線)。在下行鏈路,一個(gè)小區(qū)中的每個(gè)載波在經(jīng)過(guò)適當(dāng)?shù)南辔缓头燃訖?quán)以及上轉(zhuǎn)換以后,傳輸?shù)綄?duì)應(yīng)的天線。在上行鏈路,每個(gè)天線接收到的信號(hào)需要下變頻轉(zhuǎn)換到基帶。上變頻和下變頻功能分為模擬和數(shù)字兩個(gè)部分。在數(shù)字部分,這些功能采用數(shù)字上變頻器(Digital Up Conversion)和數(shù)字下變頻器(Digital Down Conversion)完成,兩者共同構(gòu)成數(shù)字前端(DFE)。圖1是一個(gè)基站模擬和數(shù)字前端的通用示意圖。?

?

?

對(duì)于每個(gè)小區(qū)使用六個(gè)天線和六個(gè)載波的情況,共需要 36個(gè)通道,通常這意味著需要大量專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)芯片。無(wú)論是從功耗方面,還是從PCB面積方面,這都意味著昂貴的成本,更不用提還有可靠性問(wèn)題。本文描述了一種基于FPGA的DFE解決方案。該方案使用了Multiple Access Communications (MAC)Limited公司為賽靈思公司開發(fā)的經(jīng)過(guò)預(yù)先驗(yàn)證和優(yōu)化的Xilinx? System Generator for DSP TD-SCDMA DFE IP庫(kù)。MAC公司是一家咨詢公司,位于英國(guó)南安普敦市 (Southampton)。?

TD-SCDMA DFE解決方案

使用賽靈思芯片器件(FPGA)能夠以極高的資源利用率實(shí)現(xiàn)一個(gè)符合采樣速率和調(diào)節(jié)范圍要求、同時(shí)包括DUC和DDC模塊的數(shù)字前端(DFE)解決方案。基于Xilinx System Generator for DSP工具的DFE庫(kù)支持針對(duì)不同天線和載波配置實(shí)現(xiàn)快速方便的重新配置、實(shí)現(xiàn)和驗(yàn)證,不需要重新設(shè)計(jì)或修改DUC和DDC鏈路上的基本模塊,因此用戶可以從容應(yīng)對(duì)基站DFE設(shè)計(jì)的復(fù)雜性。?

TD-SCDMA DFE庫(kù)中包含了創(chuàng)建DUC和DDC鏈路所需要的所有System Generator IP塊,包括濾波器、本地振蕩器和混頻模塊以及不同的輸入和輸出格式模塊。DFE庫(kù)是參考設(shè)計(jì)包的一部分。該參考設(shè)計(jì)包還包括一個(gè)用于硬件協(xié)同仿真的18通道設(shè)計(jì)實(shí)例、用于實(shí)現(xiàn)3GPP兼容性測(cè)試的MatLab測(cè)試腳本以及一個(gè)運(yùn)行在Nallatech V4 XtremeDSP套件上的全速演示解決方案。根據(jù)客戶要求,賽靈思公司可向客戶提供這一參考設(shè)計(jì)包(請(qǐng)參閱網(wǎng)址http://china.xilinx.com/esp/wireless/index.htm)。?

圖2和圖3給出了利用TD-SCDMA DFE庫(kù)中的IP模塊實(shí)現(xiàn)的DUC和DDC信號(hào)路徑細(xì)節(jié)。庫(kù)中的基本模塊是優(yōu)化的六通道" title="六通道">六通道DUC和DDC模塊,調(diào)諧范圍均為9.6 MHz,中頻(IF)采用速率為76.8 Msps,即TD-SCDMA 1.28 Mcps碼片速率的60倍。基帶數(shù)據(jù)以碼片速率輸入和輸出。信號(hào)路徑經(jīng)過(guò)仔細(xì)設(shè)計(jì),可實(shí)現(xiàn)最優(yōu)的資源效率,并使用307.2 MHz系統(tǒng)時(shí)鐘。這一高性能是充分發(fā)揮V4 SX FPGA中集成的DSP48功能的結(jié)果。?

?

?

?

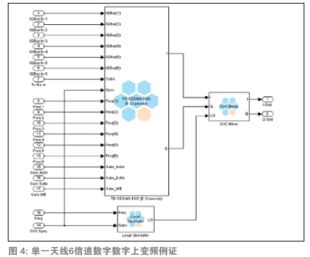

圖4所示為使用DFE資料庫(kù)模塊構(gòu)建的六通道DUC。信號(hào)處理的大多數(shù)操作都是在六通道“TD-SCDMA DUC”模塊中完成的。添加“本地振蕩器”和“DUC混頻器”資料庫(kù)模塊是為了將DUC的復(fù)合輸出從零轉(zhuǎn)換成一個(gè)更為實(shí)用的中頻。這一子系統(tǒng)生成是針對(duì)單天線" title="單天線">單天線輸出的。只需簡(jiǎn)單地復(fù)制這一子系統(tǒng),就可以支持多單元天線系統(tǒng)。?

?

?

這樣,支持任意數(shù)量的天線就變得相對(duì)簡(jiǎn)單了。那么,對(duì)于需要的載波器少于六個(gè)時(shí),又該怎么設(shè)計(jì)呢?在這種情況下,如果使用“完整的”六載波器設(shè)計(jì),盡管也不失為完全可行的解決方案,但會(huì)導(dǎo)致過(guò)大的FPGA設(shè)計(jì)。最壞的情況下,可能導(dǎo)致難以使用較小的器件,因而大大增加解決方案的成本。?

如果解決方案要求用戶手動(dòng)刪除任何不需要的邏輯,或涉及實(shí)現(xiàn)和提供一整套預(yù)定義的變量,這無(wú)疑與“讓用戶不必掌握設(shè)計(jì)的復(fù)雜細(xì)節(jié)”這一使用資料庫(kù)的初衷背道而馳。相反,DFE庫(kù)提供了一些精巧的附加邏輯,可幫助下游設(shè)計(jì)工具在構(gòu)建時(shí)將未使用的邏輯優(yōu)化掉。這樣,用戶只需要使用適當(dāng)?shù)膸?kù)模塊,并終止未使用的輸入就可以了。三通道DUC設(shè)計(jì)的例子如圖5所示。其中,利用“未使用的BB輸入”模塊將通道3到6阻斷,同時(shí)這些通道的控制輸入也被固定了恒定值。現(xiàn)在,盡管此設(shè)計(jì)使用的是六通道DUC子系統(tǒng)構(gòu)造,但那些專為未使用通道預(yù)備的所有邏輯、Block RAM 和 DSP48 都會(huì)在構(gòu)建時(shí)被刪除。

?

?

DDC的情況與此類似。圖6是六通道單天線設(shè)計(jì)的例子,而圖7是其三通道的變型。對(duì)于DDC,使用標(biāo)準(zhǔn)的Simulink Terminator模塊終止未使用的輸出,并將未使用的控制端口固定為定值,就可以將未使用的通道優(yōu)化掉。對(duì)于DUC,只需要簡(jiǎn)單地復(fù)制單天線設(shè)計(jì),就可以支持多個(gè)天線。?

?

?

?

?

前面假設(shè)9.6 MHz的調(diào)諧范圍是足夠的,對(duì)于需要大于9.6 MHz調(diào)諧范圍的應(yīng)用,可以通過(guò)級(jí)聯(lián)兩個(gè)同樣DUC或DDC模塊的方式擴(kuò)展調(diào)諧范圍,例如,調(diào)整到15 MHz的范圍。?

3GPP兼容性測(cè)試和性能驗(yàn)證

如上所述,TD-SCDMA DFE庫(kù)模塊組中的IP模塊設(shè)計(jì)滿足TS25.105中的3GPP要求。因此,可以確保對(duì)于任何基于該IP庫(kù)的系統(tǒng)都可以滿足相關(guān)的3GPP要求,如頻譜屏蔽和鄰近信道泄露比(ACLR),并且有足夠的余量來(lái)彌補(bǔ)模擬器件的失真效應(yīng)。?

表1給出了與3GPP要求相關(guān)的性能總結(jié),包括每個(gè)參數(shù)提供的余量。針對(duì)DUC和DDC功能的3GPP兼容性測(cè)試以MatLab腳本的方式實(shí)現(xiàn),腳本使用了硬件協(xié)同仿真(運(yùn)行在Nallatech V4 XtremeDSP套件之上)。表1給出的性能數(shù)據(jù)就是由這些測(cè)試給出的。圖8至圖10顯示出Matlab測(cè)試腳本得到的一些測(cè)試圖,包括DUC頻譜屏蔽、DDS性能以及DDC鄰近信道選擇性和阻塞測(cè)試。

?

?

?

?

?

?

?

?

?

采用運(yùn)行全速12通道設(shè)計(jì)的V4 XtremeDSP套件還進(jìn)行了進(jìn)一步的實(shí)際測(cè)試。利用V4開發(fā)板上的14位數(shù)模轉(zhuǎn)換器生成19.2 MHz的IF輸出信號(hào)。DAC輸出被饋送到安捷倫(Agilent)頻譜分析儀中,如圖11所示。?

?

?

如圖12所示,這一12通道設(shè)計(jì)帶有一個(gè)圖形用戶界面(GUI)。該界面能夠支持多種功能。例如,DUC輸出可以通過(guò)DAC-ADC路徑或內(nèi)部反饋到DDC,經(jīng)過(guò)下轉(zhuǎn)換并顯示在某個(gè)圖形用戶界面窗口中。?

?

?

實(shí)施結(jié)果

綜上所述,利用TD-SCDMA DFE IP庫(kù)可以實(shí)現(xiàn)和配置從單載波、單天線,直到六載波、多天線的各種不同DFE配置,唯一的限制就是可用的FPGA資源。表2和表3分別給出了實(shí)現(xiàn)一個(gè)六載波、三天線配置的半?yún)^(qū)方案,和一個(gè)三載波、四天線配置的半?yún)^(qū)方案所需要的FPGA資源。換句話說(shuō),兩種情況下實(shí)現(xiàn)全區(qū)設(shè)計(jì)也只需要兩片SX25器件。兩個(gè)例子的中頻帶寬為9.6 MHz。?

?

?

?

結(jié)論

由于TD-SCDMA標(biāo)準(zhǔn)的波束成形(beam forming)要求,因此基站需要大量上變頻/下變頻(DUC/DDC)通道。本文表明利用賽靈思 V4 SX FPGA和賽靈思 TD-SCDMA DFE 庫(kù)可以實(shí)現(xiàn)高效快速的符合3GPP標(biāo)準(zhǔn)的TD-SCDMA數(shù)字前端(DFE)解決方案,從而使設(shè)備供應(yīng)商能夠集中更多精力來(lái)實(shí)現(xiàn)產(chǎn)品差異化并加快產(chǎn)品的上市時(shí)間。?