0 引言

近年來,由于半導(dǎo)體技術(shù)、數(shù)字信號(hào)處理技術(shù)及通信技術(shù)的飛速發(fā)展,A/D、D/A轉(zhuǎn)換器近年也呈現(xiàn)高速發(fā)展的趨勢(shì)。隨著數(shù)字信號(hào)處理技術(shù)在高分辨率圖像、視頻處理及無線通信等領(lǐng)域的廣泛應(yīng)用,對(duì)高速、高精度、基于標(biāo)準(zhǔn)COMS工藝的可嵌入式ADC的需求日益迫切。此外對(duì)于正在興起的基于IP庫設(shè)計(jì)和片上系統(tǒng)(SOC)集成研究來說,對(duì)低功耗、小面積、低電壓以及可嵌入設(shè)計(jì)的ADC核心模塊需求更甚。

由于高速、高精度A/D轉(zhuǎn)換器(ADC)的發(fā)展,尤其是能直接進(jìn)行中頻采樣的高分辨率數(shù)據(jù)轉(zhuǎn)換器的上市,對(duì)穩(wěn)定的采樣時(shí)鐘的需求越來越迫切。隨著通信系統(tǒng)中的時(shí)鐘速度邁人吉赫茲級(jí),相位噪聲和時(shí)鐘抖動(dòng)成為模擬設(shè)計(jì)中十分關(guān)鍵的因素。

為了保證電子系統(tǒng)的數(shù)據(jù)采集、控制反饋和數(shù)字處理的能力和性能,現(xiàn)代軍用電子系統(tǒng)對(duì)A/D轉(zhuǎn)換器的要求也越來越高。尤其是軍事數(shù)據(jù)通信系統(tǒng)、數(shù)據(jù)采集系統(tǒng)對(duì)高速、高分辨率A/D轉(zhuǎn)換器的需求在不斷增加,時(shí)鐘占空比穩(wěn)定電路作為高速、高精度A/D轉(zhuǎn)換器的核心單元,對(duì)轉(zhuǎn)換器的信噪比(RSN)和有效位(ENOB)等性能起至關(guān)重要的作用,要保證高速、高精度A/D轉(zhuǎn)換器的性能,必須首先保證采樣編碼時(shí)鐘具有合適的占空比和很小的抖動(dòng)。

1 時(shí)鐘穩(wěn)定電路

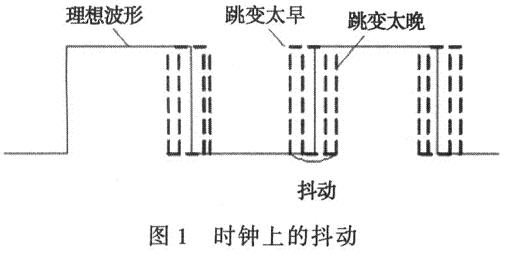

相位噪聲和抖動(dòng)是對(duì)同一種現(xiàn)象的兩種不同的定量方式。在理想情況下,一個(gè)頻率固定的完美的脈沖信號(hào)(以1 MHz為例)的持續(xù)時(shí)間應(yīng)該恰好是1μs,每500 ns有一個(gè)跳變沿,但這種信號(hào)并不存在。如圖1所示,信號(hào)周期的長度總會(huì)有一定變化,從而導(dǎo)致下一個(gè)沿的到來時(shí)間不確定。這種不確定就是相位噪聲,或者說是抖動(dòng)。

抖動(dòng)是對(duì)信號(hào)時(shí)域變化的測(cè)量結(jié)果,它從本質(zhì)上描述了信號(hào)周期距離其理想值偏離了多少。通常,10 MHz以下信號(hào)的周期變動(dòng)并不歸入抖動(dòng)一類,而是歸入偏移或者漂移。數(shù)據(jù)轉(zhuǎn)換器的主要目的要么是由定期的時(shí)間采樣產(chǎn)生模擬波形,要么是由一個(gè)模擬信號(hào)產(chǎn)生一系列定期的時(shí)間采樣。因此,采樣時(shí)鐘的穩(wěn)定性是十分重要的。從數(shù)據(jù)轉(zhuǎn)換器的角度來看,這種不穩(wěn)定性,亦即隨機(jī)的時(shí)鐘抖動(dòng),會(huì)在模數(shù)轉(zhuǎn)換器何時(shí)對(duì)輸入信號(hào)進(jìn)行采樣方面產(chǎn)生不確定性。

從數(shù)據(jù)轉(zhuǎn)換器的角度來看,編碼帶寬可擴(kuò)展到數(shù)百兆赫。在考慮構(gòu)成數(shù)據(jù)轉(zhuǎn)換器時(shí)鐘抖動(dòng)噪聲的帶寬時(shí),其范圍是從直流到編碼的帶寬,這遠(yuǎn)遠(yuǎn)超過制造商常常當(dāng)作標(biāo)準(zhǔn)時(shí)鐘抖動(dòng)測(cè)量值引用的12kHz~20 MHz典型值。由于與抖動(dòng)有關(guān)的是寬帶轉(zhuǎn)換器噪聲增大,所以只要觀察數(shù)據(jù)轉(zhuǎn)換器噪聲性能的下降,就可很方便地評(píng)估時(shí)鐘抖動(dòng)。式(1)可確定由于時(shí)鐘抖動(dòng)而產(chǎn)生的信噪比(RSN)極限

![]()

式中:f為模擬輸入頻率;t為抖動(dòng)。求解t則式(1)變?yōu)槭?2)。如果已知工作頻率和RSN要求,則式(2)就可確定時(shí)鐘抖動(dòng)要求

只要在模擬輸入頻率增大時(shí)觀察到信噪比下降,就可以很方便地使用數(shù)據(jù)轉(zhuǎn)換器(特別是模數(shù)轉(zhuǎn)換器ADC),通過快速傅里葉變換(FFT)技術(shù)計(jì)算出信噪比。從總噪聲中減去ADC產(chǎn)生的噪聲,就可以估算出時(shí)鐘抖動(dòng)產(chǎn)生的噪聲,一旦知道噪聲系數(shù),就可以計(jì)算出時(shí)間抖動(dòng)。

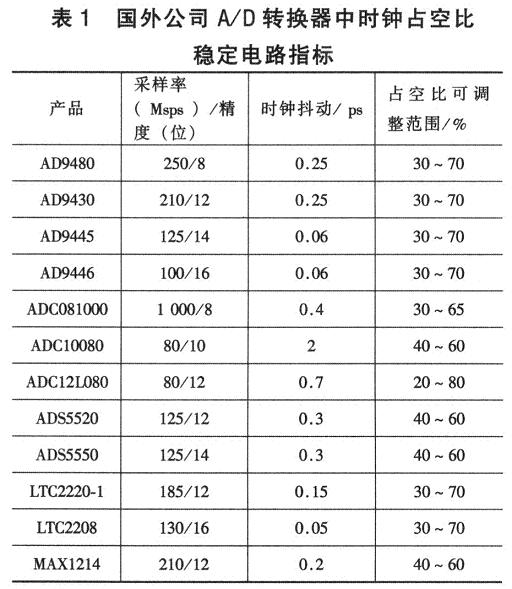

ADI產(chǎn)品與其他公司產(chǎn)品相比之所以能提高采樣性能,主要得益于對(duì)DCS電路的改進(jìn)。DCS電路擔(dān)負(fù)著減小時(shí)鐘信號(hào)抖動(dòng)的作用,而采樣時(shí)序就取決于時(shí)鐘信號(hào)。各家公司過去的DCS電路只能將抖動(dòng)控制在0.25 ps左右,而高性能新產(chǎn)品AD9446和LTC2208則將抖動(dòng)降低到50 fs左右。通常降低抖動(dòng)就能夠改善信噪比,這樣便提高了有效分辨率(ENOB:有效比特?cái)?shù)),從而在達(dá)到16 bit量子化位數(shù)的同時(shí),實(shí)現(xiàn)100 Msps以上的采樣速率。如果不控制抖動(dòng)就提高采樣速率的話,將降低ENOB,無法獲得希望的分辨率,也無法提高量子化位數(shù)。隨著高性能A/D轉(zhuǎn)換器的發(fā)展,DCS電路向更高速度、更小抖動(dòng)和穩(wěn)定方向發(fā)展。

目前,國外幾個(gè)大公司所設(shè)計(jì)的A/D轉(zhuǎn)換器中時(shí)鐘占空比穩(wěn)定電路的指標(biāo)如表1所示。由于國內(nèi)高速、高精度A/D轉(zhuǎn)換器的設(shè)計(jì)技術(shù)、工藝技術(shù)和測(cè)試技術(shù)與國外先進(jìn)水平還有一定的差距,同時(shí)研制的時(shí)鐘穩(wěn)定電路性能指標(biāo)還不理想,目前正在研制的時(shí)鐘占空比穩(wěn)定電路頻率為65 Msps,抖動(dòng)為2 ps。

時(shí)鐘占空比穩(wěn)定電路框圖如圖2虛框所示,它由輸入緩沖放大器A,開關(guān)Kl、K2和DLL組成。

緩沖放大器A實(shí)際上只是對(duì)時(shí)鐘信號(hào)進(jìn)行緩沖。當(dāng)采樣時(shí)鐘頻率低于DLL工作下限時(shí),開關(guān)K1、K2向上閉合,DLL被旁路;開關(guān)K1、K2向下閉合,DLL開始作用,調(diào)節(jié)輸入時(shí)鐘信號(hào)相位。由于DLL具有延遲鎖相的功能,因此能很好地控制時(shí)鐘占空比,本設(shè)計(jì)中通過下文的具體電路能使輸入時(shí)鐘的占空比接近50%,抖動(dòng)小于0.5 ps。

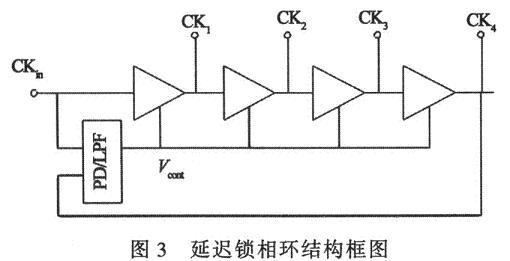

延遲鎖相環(huán)在普通鎖相環(huán)(PLL)的基礎(chǔ)上,用電壓控制延遲線代替了壓控振蕩器,其結(jié)構(gòu)框圖如圖3所示。其中CKin和CK4之間的相位差用一個(gè)鑒相器來檢測(cè),產(chǎn)生成比例的平均電壓Vcont,通過這個(gè)電壓的負(fù)反饋來調(diào)節(jié)每一級(jí)的延時(shí)。對(duì)于大的環(huán)路增益,CKin和CK4之間的相位差很小,即這四級(jí)電路將時(shí)鐘幾乎準(zhǔn)確地延時(shí)了一個(gè)周期,從而建立了準(zhǔn)確的時(shí)鐘沿間隔。這種電路結(jié)構(gòu)被稱為延遲鎖相環(huán),是為了強(qiáng)調(diào)它采用了一個(gè)電壓控制延遲線電路而不是VCO。實(shí)際上,為獲得無窮大的環(huán)路增益,需要在PD和LPF之間插入電荷泵。

延遲線與振蕩器相比受噪聲較小,這是因?yàn)椴ㄐ沃斜粨p壞的過零點(diǎn)在延遲線的末端就消失了,而在振蕩器電路中又會(huì)再循環(huán),因而產(chǎn)生更多的損壞;其次,DLL中控制電壓的變化能迅速改變延遲時(shí)間。總之,PLL中用到的振蕩器存在不穩(wěn)定性和相位偏移的積累,因而在補(bǔ)償時(shí)鐘分別造成的時(shí)間延遲時(shí),會(huì)降低PLL的性能。因此DLL的穩(wěn)定性和穩(wěn)定速度等問題比PLL要好。

2 電路設(shè)計(jì)

2.1 電路原理圖

圖4中,虛框a中的電路為鑒相器(PD),S為鑒相器的控制端,只有為低電平時(shí),鑒相器才起作用。壓控延遲線的輸出端VCDLout為鑒相器的輸入端,這個(gè)信號(hào)與時(shí)鐘信號(hào)CLK進(jìn)行比較,得出輸出信號(hào)A。由于S端低電平有效,CLK信號(hào)就是與它的反相延遲信號(hào)與非進(jìn)入后面的鎖存結(jié)構(gòu)。其實(shí)就是檢測(cè)下沿與另一個(gè)下沿組成一個(gè)占空比接近50%的時(shí)鐘信號(hào)。A信號(hào)經(jīng)過一個(gè)電阻R傳入電荷泵中(其實(shí)在鑒相器的輸出端可以加一個(gè)反相器再加一個(gè)電容濾波)。虛框b為電荷泵,由一個(gè)運(yùn)算放大器組成。其中F端接一個(gè)電壓值為基準(zhǔn)的一半的電壓,即為1.65 V。

由m0、ml、m2、m3組成的鏡像是運(yùn)算放大器的啟動(dòng)電路,在運(yùn)算放大器不工作時(shí)對(duì)電容C1充電。電阻R1和電容C1構(gòu)成一個(gè)RC濾波器,對(duì)信號(hào)起到濾波的作用。m4、m5、m6三個(gè)晶體管構(gòu)成DLL的延遲線(VCDL)。在這個(gè)電路中只需要一級(jí)延遲就足夠了。在這個(gè)延遲線旁邊的電容C2的值越大,則延遲越多。C2旁邊三個(gè)反相器構(gòu)成一個(gè)鎖存結(jié)構(gòu),它的主要作用就是輸出一個(gè)比較理想的方波。

2. 2電路仿真與分析

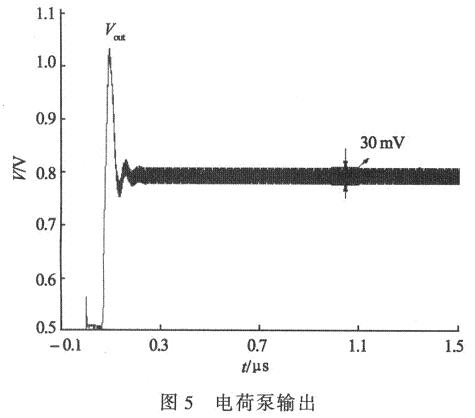

對(duì)圖4的電路,在Cadence spectre環(huán)境下進(jìn)行了仿真。輸入電平的周期為4 ns,時(shí)鐘占空比為45%,基準(zhǔn)電壓為3.3 V。運(yùn)算放大器與電容c.組成電荷泵。電荷泵的輸出見圖5。時(shí)鐘穩(wěn)定電路穩(wěn)定工作,Vout有30 mV的波動(dòng),Vout波動(dòng)越小表示壓控延遲線時(shí)鐘輸出的抖動(dòng)越小。

此外,還可以得到,運(yùn)算放大器的閉環(huán)增益為75.074 9 dB。0 dB對(duì)應(yīng)的相位為一109.818°,所以它的相位裕度為70.182°。顯然,該運(yùn)算放大器的參數(shù)是比較好的。

圖6為時(shí)鐘占空比調(diào)整情況。從圖中可以看出該DLL能調(diào)整占空比到49.4%(1.977 4/4≈49.5%)。實(shí)際上該時(shí)鐘穩(wěn)定電路在時(shí)鐘周期4 ns時(shí),能調(diào)節(jié)25%~75%的占空比接近于50%左右;而在時(shí)鐘周期10 ns時(shí),可調(diào)節(jié)的范圍達(dá)到10%~90%。

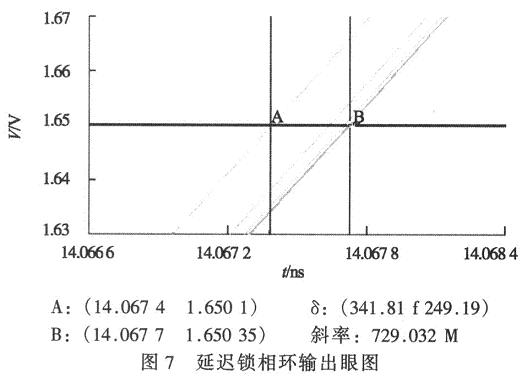

圖7為延遲鎖相環(huán)的輸出眼圖。其實(shí)在A、B之間有幾百條上升沿。從圖中可以看出,峰.峰值抖動(dòng)為341.8l fs。對(duì)于250 M這個(gè)抖動(dòng)值已經(jīng)相當(dāng)小了。

3 版圖設(shè)計(jì)

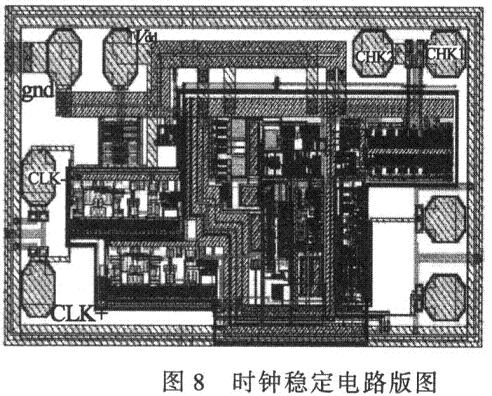

利用JAZZ提供的PDK進(jìn)行工藝接口,版圖設(shè)計(jì)由該公司提供相應(yīng)規(guī)則,具體針對(duì)線寬、接觸孔、通孔、線距等作了相關(guān)規(guī)定,并且設(shè)計(jì)過程中充分利用該公司提供的Pcell作相應(yīng)的版圖設(shè)計(jì),這樣相應(yīng)工作得到了很多的簡(jiǎn)化。具體的設(shè)計(jì)規(guī)則涉及IP問題,故略去。本文給出時(shí)鐘穩(wěn)定電路的整個(gè)版圖,如圖8所示。

該芯片總面積為0.74 mm×1.44 mm。其中,最左邊的CLK一,CLK+為輸入端,本文只用到CLK一一端作為輸入端就足夠了;右上角的CHKl、CHK2為輸出的大管子;最中間為運(yùn)算放大器。

4 結(jié)語

本文介紹了用一個(gè)簡(jiǎn)單的延遲鎖相環(huán)來實(shí)現(xiàn)高速A/D轉(zhuǎn)換器中的時(shí)鐘穩(wěn)定電路。該延遲鎖相環(huán)具有兩個(gè)作用:(1)調(diào)節(jié)采樣時(shí)鐘占空比;(2)控制采樣時(shí)鐘的抖動(dòng)。本文以一些典型的基奉模擬IC為設(shè)計(jì)基礎(chǔ),著重對(duì)延遲鎖相環(huán)電路的各個(gè)單元電路設(shè)計(jì)逐一進(jìn)行了分析和研究,并對(duì)總體電路進(jìn)行了功能和參數(shù)的模擬分析,其結(jié)果較為滿意。在此基礎(chǔ)上進(jìn)行了工藝及版圖設(shè)計(jì)和分析,在完成工藝版圖設(shè)計(jì)后,采用DRC、ERC、Calibre、Extract和LVS等CAD工具對(duì)版圖進(jìn)行了參數(shù)提取及驗(yàn)證工作,保證了電路和版圖的一致性。