0 引言

過采樣∑-△A/D轉(zhuǎn)換器以其高精度和易于用標準數(shù)字CMOS工藝實現(xiàn)的特點而被廣泛應用,并越來越多地集成到片上系統(tǒng)(SOC)中。∑-△ADC采用的是過采樣和低位量化結(jié)合的方法,能夠避免使用高精度模擬電路,將噪聲推向高頻,具有分辨率高、量化結(jié)構(gòu)簡單等優(yōu)點。降采樣濾波器作為過采樣∑-△A/D轉(zhuǎn)換器的重要組成部分,用于濾除基帶信號帶外噪聲和降低抽樣頻率至臨界抽樣頻率。目前國內(nèi)∑-△ADC的研究主要集中在音頻領(lǐng)域,帶寬20 kHz。本文介紹了一種帶寬150 kHz、16 bit∑-△模數(shù)轉(zhuǎn)換器中的降采樣濾波器的設(shè)計與實現(xiàn)。

1 ∑-△ADC的主要性能指標

信號與噪聲加失真比(SINAD)是直流到奈奎斯特頻段內(nèi),正弦波的RMS(均方根,表示交流信號的有效值或有效直流值)值與轉(zhuǎn)換器噪聲的RMS值之比,包括諧波成分。

信噪比(RSN)是直流到奈奎斯特頻段內(nèi),正弦波的RMS值與轉(zhuǎn)換器噪聲的RMS值之比。

無雜散動態(tài)范圍(SFDR)是RMS信號幅度與最大雜散頻譜分量RMS值的比率。

總諧波失真(THD)是出現(xiàn)在輸入頻率整數(shù)倍頻點(諧波)失真的RMS值與輸入(或輸出)正弦波的RMS值之比。

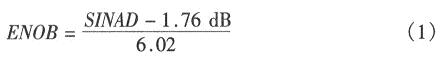

有效位數(shù)(ENOB)與SINAD的關(guān)系為

本設(shè)計要達到的性能指標是ENOB≥14 bit;SINAI)≥86 dB;SFDR≥92 dB;THD≤一90 dB;信號帶寬為150 kHz;精度為16 bit。

2 調(diào)制器的系統(tǒng)設(shè)計

2.1 低階∑-△調(diào)制器

調(diào)制器中的階數(shù)即積分器的個數(shù),一階∑-△調(diào)制器的信噪比

RSN=6.02N+1.76—5.17+301g(OSR) (2)

式中:N為模擬調(diào)制器中量化器的位數(shù);OSR為過采樣比。式(2)表明,當OSR足夠大時,在理論上也可獲得相當好的量化信噪比。

2.2 高階∑一△調(diào)制器

高階∑-△調(diào)制器理想信噪比

式中n為調(diào)制器階數(shù)。

但是在使用一位量化器情況下,環(huán)內(nèi)濾波器增加到三階以上時,工作情況會變得不穩(wěn)定。

2.3 本設(shè)計中的∑一△調(diào)制器

本設(shè)計采用三階∑-△調(diào)制器(n=3),OSR為128,調(diào)制器的量化器用1 bit進行量化(N=1,降低模擬電路設(shè)計的難度)。由式(3)可得RSN=133.9 dB,滿足16 bit精度要求。

設(shè)計要求帶寬為150 kHz,而過采樣率設(shè)為128,則理想情況下為

fs=150 kHz×2×128=38.4 MHz

考慮到系統(tǒng)設(shè)計和實現(xiàn)的非理想特性,本設(shè)計的采樣頻率定為50 MHz,經(jīng)過128倍降采樣后ADC的輸出數(shù)據(jù)速率為390.625 kHz。

本系統(tǒng)設(shè)計在Matlab 7.0環(huán)境下采用Mathworks公司的Delta-Sigma Toolbox中提供的迭代逼近法實現(xiàn)滿足要求的噪聲傳輸函數(shù),得到初始結(jié)構(gòu)參數(shù)。并根據(jù)文獻得到∑-△調(diào)制器的三階CRFB系統(tǒng)實現(xiàn)模型,對該模型的性能分析可得其峰值信噪比達到113.2 dB,滿足16 bit精度要求。

3 降采樣濾波器的設(shè)計和系統(tǒng)仿真

本設(shè)計中的降采樣濾波器由級聯(lián)積分梳狀濾波器、頻率補償濾波器和FIR半帶濾波器級聯(lián)組成。其中級聯(lián)積分梳狀濾波器實現(xiàn)多倍降采樣,頻率補償濾波器針對多倍降采樣后的通帶下降進行補償,而FIR型半帶濾波器硬件結(jié)構(gòu)非常簡單并且適合實現(xiàn)D=2倍降采樣,因此作為本降采樣系統(tǒng)中的最后一級。

3.1 級聯(lián)積分梳狀濾波器

CIC濾波器是由積分模塊與梳狀濾波器模塊組成的一種濾波器。Hogenauer提供了輸入、輸出比特數(shù)之間的關(guān)系,它們之間滿足

![]()

本設(shè)計中CIC濾波器的降頻倍數(shù)R為16,調(diào)制器輸出一位量化的數(shù)據(jù),Bin=1。而參考文獻指出,CIC的級數(shù)要求大于調(diào)制器的階數(shù),因此本設(shè)計的級數(shù)N=4。由式(4)得Bout=17,滿足精度要求。CIC濾波器的結(jié)構(gòu)用Matlab 7.0中Simulink Library搭建,實現(xiàn)如圖1所示。

3.2 頻率補償濾波器

CIC存在著通帶下降的問題。觀察CIC濾波器的幅頻響應圖發(fā)現(xiàn)f=150 kHz時,Magnitude=O.996 l,而本設(shè)計的ENOB要求達到14 bit,即誤差應小于2-14,無法滿足。因此,本設(shè)計引入了Sharpened CIC和ISOP兩種補償技術(shù)對CIC的通帶下降進行補償。

3.2.1 Sharpened CIC濾波器

參考文獻提出的一種新的CIC結(jié)構(gòu)是基于由J.Kaiser和R.Hamming提出對濾波器響應進行銳化的技術(shù)。這項新的技術(shù)嘗試通過復用相同的濾波器來同時減小通帶下降和提高阻帶衰減。Sharpened CIC的結(jié)構(gòu)框圖如圖2所示。

而本設(shè)計中CIC濾波器的群延時為30,其中的H(z)為CIC濾波器的傳輸函數(shù)。

3.2.2 ISOP濾波器

CIC抽取濾波器通帶下降這一問題還可以通過級聯(lián)內(nèi)插二階多項式獲得部分解決。ISOP濾波器的系統(tǒng)函數(shù)為

式中:I為正整數(shù);c為實數(shù)。

如果CIC濾波器已經(jīng)確定,則最佳ISOP濾波器可以采用切比雪夫逼近法設(shè)計。對所有滿足 的整數(shù)k,解如下方程

的整數(shù)k,解如下方程

可得到使δ最小的一組(k,c)對。

本設(shè)計中,k=4,c=1 617.19,f=166 kHz時Magnitude=0.999 947,滿足ENOB為14 bit的要求,并為后面的設(shè)計留下16 kHz的冗余空間。

3.3 FIR半帶濾波器

FIR型半帶濾波器是一種特別適合實現(xiàn)D=2倍降采樣的線性相位濾波器,其硬件結(jié)構(gòu)非常簡單,因此在降采樣系統(tǒng)中的最后一級一般都采用半帶濾波器。

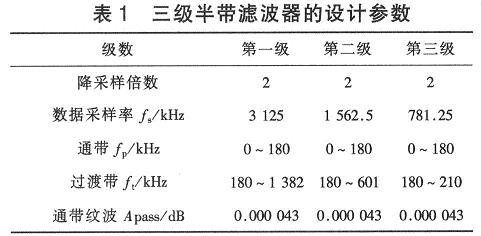

根據(jù)∑一△ADC的技術(shù)指標,可以得到三級半帶濾波器的設(shè)計參數(shù),如表1所示。

通帶設(shè)為O~180 kHz,是為了保證0~150 kHz帶寬內(nèi)均能滿足指標要求。通帶紋波取0.000 005(0.000 043 dB),是為了滿足設(shè)計的有效位數(shù)為14 bit,并且考慮到尾數(shù)舍入等非理想因素的存在。

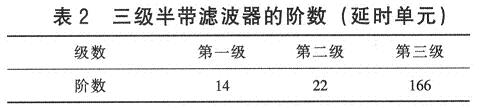

根據(jù)表1,調(diào)用Matlab 7.O中的工具箱組件filter design,得到三級半帶濾波器的系數(shù)。表2分別列出了三級半帶濾波器的階數(shù)(延時單元)。

3.4 系統(tǒng)仿真與驗證

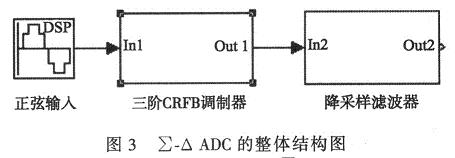

實現(xiàn)∑-△ADC的整體結(jié)構(gòu)如圖3所示,抽取濾波器由Sharpened CIC濾波器、ISOP濾波器和三級半帶濾波器組成。Sharpened CIC實現(xiàn)16倍抽取,三級半帶濾波器實現(xiàn)8倍抽取。

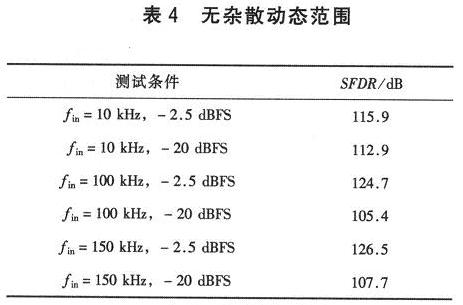

圖4為150 kHz輸入信號(一2.5 dBFS)仿真輸出數(shù)據(jù)的FFT圖。表3、4、5分別為SINAD、SFDR和THD的仿真數(shù)據(jù)。

4 降采樣濾波器的ASIC設(shè)計

4.1 電路設(shè)計

本設(shè)計用Verilog硬件描述語言描述電路,采用Synopsys的Design Compiler進行綜合。

4.1.1 濾波器系數(shù)優(yōu)化

本設(shè)計采用CSD碼(canonical signed-digit)來表示量化后的系數(shù)。和二進制代碼相比CSD碼采用0、l和一1來表示一個數(shù),具有非零位的個數(shù)最少、每一個非零位的相鄰位必為零的特點。

4.1.2 乘法器設(shè)計

本設(shè)計中乘法器單元的上限定為16×16,本文采用了Synopsys提供的DesignWare庫中的16×16乘法器單元,該單元的設(shè)計和綜合都比較成熟,通過Design Compiler綜合后面積和速度的優(yōu)化都比較理想。對于位數(shù)高于16 x 16的乘法器,本文以16×16乘法器單元先進行低位乘法運算,再進行高位乘法運算,最后再將高低位結(jié)果移位相加得到最終的乘法結(jié)果。

4.1.3 各級間輸入輸出位數(shù)的確定

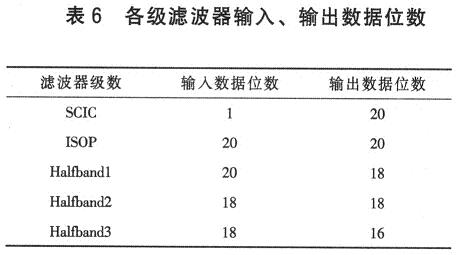

本文設(shè)計了一個濾波器各級位數(shù)動態(tài)可調(diào)的方法,對降采樣濾波器各級輸入、輸出位數(shù)各種可能的情況進行分析,得到最終的各級濾波器的輸入輸出數(shù)據(jù)位數(shù)如表6所示。

4.1.4 時鐘的處理

系統(tǒng)用到了多個分頻時鐘,為了方便后面布局布線做時鐘樹,本設(shè)計采用計數(shù)器產(chǎn)生使能信號進行分頻。

4.1.5 Design Compiler綜合

本設(shè)計采用SMIC 0.18μm CMOS工藝庫,將編寫的Verilog代碼用Synopsy的Design Compiler綜合,通過加上適當?shù)募s束條件反復優(yōu)化,最終得到綜合結(jié)果。綜合結(jié)果通過Synopsys VCS仿真驗證。

4.2 版圖設(shè)計

本設(shè)計采用Cadence Encounter對綜合后的濾波器的門級網(wǎng)表進行布局布線,圖5是完成布局布線后的版圖。芯片主要參數(shù)如表7所示。

5 芯片測試

在模擬三階CRFB結(jié)構(gòu)的∑-△調(diào)制器輸入的情況下,通過邏輯分析儀采集輸入為150 kHz正弦信號的輸出數(shù)據(jù),并由計算得到的頻譜如圖6所示,信號與噪聲加失真比(SINAD)大于86 dB,滿足性能指標要求。

6 結(jié)論

本文介紹了一個用于帶寬150 kHz、精度16 bit的高精度、寬帶∑-△模數(shù)轉(zhuǎn)換器中的降采樣低通濾波器。本設(shè)計可以集成在SOC芯片中,主要應用于醫(yī)療儀器、移動通信、過程控制和PDA等領(lǐng)域。濾波器通過級聯(lián)Sharpened CIC濾波器、ISOP濾波器和半帶濾波器實現(xiàn)。并通過Synopsy的Design Compiler進行電路綜合和Cadence Encounter進行布局布線,采用SMIC 0.18μm CMOS工藝實現(xiàn)。系統(tǒng)仿真和芯片測試結(jié)果表明,性能滿足設(shè)計指標要求。