1 引言

在科研和工程中,數(shù)據(jù)采集系統(tǒng)具有很廣泛的應(yīng)用,針對各類電壓型傳感器輸出的信號伏值不同這種情況,本文提出了一種能夠控制增益的數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)以FPGA 作為邏輯控制核心,選用儀表運算放大器AD623 作放大電路,ADG704 作為模擬開關(guān),通過對FPGA 進行編程配置,控制模擬開關(guān)選通不同的電阻,選通電阻配合AD623 實現(xiàn)放大。同時該系統(tǒng)可以對多通道配置不同的增益,從而可以采集不同傳感器輸出的信號。實現(xiàn)了采集范圍寬的采集要求。

2 系統(tǒng)設(shè)計方案

本設(shè)計采用現(xiàn)場可編程門陣列(FPGA)作為主控單元,實現(xiàn)整個系統(tǒng)的邏輯控制。整個系統(tǒng)的原理框圖如圖1 所示。從整個流程來看,系統(tǒng)主要由以下幾個模塊組成:運算放大模塊、AD 轉(zhuǎn)換模塊、可編程邏輯器件控制模塊。

圖1 系統(tǒng)設(shè)計原理框圖

整個系統(tǒng)的工作流程為:首先確定各通道輸入信號范圍,從而確定各通道的增益,對FPGA 進行編程配置,使ADG704 選中增益配置電阻,經(jīng)AD623 放大后通過精密運放OP113 跟隨輸出,通過多路選擇器切換將模擬信號輸出至AD轉(zhuǎn)換器,將轉(zhuǎn)換完成的數(shù)據(jù)通過FPGA 存儲在FLASH。完成整個系統(tǒng)的數(shù)據(jù)采集。

3 典型電路設(shè)計

下圖2 為運算放大模塊電路圖。

圖2 儀表運算放大電路圖

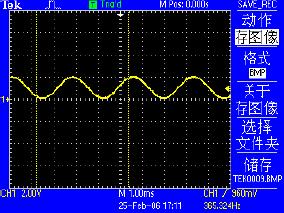

該模塊的核心為儀表運放AD623,AD623 是一個集成單電源儀表放大器,它能在單電源(+3V~+12V)下提供滿電源幅度的輸出,其增益設(shè)置范圍為1~1000。AD623 通過提供極好的隨增益增大而增大的交流共模抑制比(ACCMRR)而保持最小的誤差,線路噪聲及諧波將由于共模抑制比在高達200Hz 時仍保持恒定而受到抑制。增益可通過1 腳和8 腳之間的電阻設(shè)置,其公式如下:

G 為放大倍數(shù)。X R 為調(diào)節(jié)電阻。

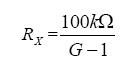

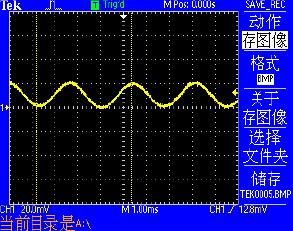

圖中輸入信號前加一階無源低通濾波器,濾除混疊在信號中的高頻成分,信號截至頻率可以通過f=1/2ΠRC 求得,同時在AD623 輸出端又加一級分壓濾波器,它與前一級濾波器構(gòu)成二階無源低通濾波器。對濾波后的信號進行放大,對于AD623,如果信號不加共模信號直接放大,輸出信號最大將會被限制在1.25V。如圖輸入信號為0~20mv 正弦波,通過調(diào)節(jié)電阻使其增益設(shè)置為100,此時輸出應(yīng)為0~2V 的正弦波,但實際波形如下:

信號輸入波形

信號輸出波形

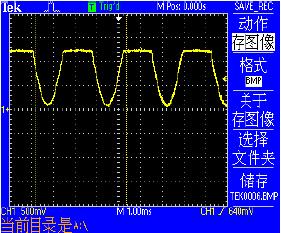

如果在輸入端加2.5V 共模電壓,電路圖連接如圖2,同樣在輸入端加0~20mv 正弦波,增益設(shè)置為100,輸出波形如下:

信號輸出波形

為了提高驅(qū)動能力,如圖2 中在AD623 輸出端加一級跟隨器OP113 作為驅(qū)動,因為AD623 設(shè)計為驅(qū)動10K 歐或以上的負載,如果負載小于10KΩ時,需要用一個精密運放作為緩沖提高驅(qū)動能力,接OP113 作為跟隨驅(qū)動器,當負載小到600Ω時,也可以在負載上得到0~4V 的輸出擺幅。

在圖2 中ADG704 作為模擬開關(guān),主要用來切換S1~S4 中的某一通道與D 導(dǎo)通,該選中通道與AD623 配合實現(xiàn)增益控制。對于ADG704 的控制,用可編程邏輯器件編程實現(xiàn)。控制使能和選擇信號A1、A0、EN 通過真值表1 實現(xiàn)切換。

表1 ADG704 真值表

4 結(jié)束語

本文提出的由可編程邏輯器件控制系統(tǒng)的放大倍數(shù),充分利用了儀表運算放大器AD623 的增益可調(diào)功能及其優(yōu)越性。每一路熱電偶輸入信號可以有多個不同的放大倍數(shù),使得各種幅值不同的輸入信號采集的實現(xiàn)更加方便、可靠、快捷。選用的16 位AD 轉(zhuǎn)換器,以采集精度高、控制方便、轉(zhuǎn)換速度快等優(yōu)點,更大程度地優(yōu)化了該系統(tǒng)。

參考文獻

[1] 陳慧華. 共模抑制和儀表放大器. 武漢力源電子股份有限公司2005.7

[2] 時雨、趙正予. 可變增益放大器AD623 在雷達系統(tǒng)中的應(yīng)用.電子設(shè)計應(yīng)用.2004.5

[3] 趙雅興. FPGA 原理、設(shè)計與應(yīng)用. 天津:天津大學(xué)出版社. 1998

[4] 劉樹棠、朱茂林、榮玫 譯. 基于運算放大器和模擬集成電路的電路設(shè)計.西安交通大學(xué)出版社. 2004.8

[5] 雷印勝,孫同景. 基于DSP 的動態(tài)心電記錄儀.微計算機信息.2002 年第3期:39~40。