1 DAC8420的主要特點(diǎn)

DAC8420是AD公司生產(chǎn)的四路輸出12位DAC。該DAC具有高速串行接口,而且功耗很低,能廣泛應(yīng)用于伺服系統(tǒng)控制、過程自動(dòng)化控制及ATE中。其主要特點(diǎn)如下:

●可選擇單極或雙極模式;

●復(fù)位后,輸出置0或置中間值;

●電源選擇廣泛,單+5V~±15V均可;

●采用16腳PDIP、CERDIP或SOIC封裝。

2 DAC8420的引腳功能

DAC8420的引腳排列如圖1所示,各引腳功能及使用說明如下:

VDD:正電源,范圍為+5V~+15V;

VSS:負(fù)電源,范圍為0~15V;

GND:數(shù)字地。

CLK:系統(tǒng)串行時(shí)鐘輸入,邏輯上與CS信號(hào)相或。在時(shí)鐘上升沿,由SDI輸入的串行數(shù)據(jù)將進(jìn)入DAC內(nèi)部的串/并轉(zhuǎn)換寄存器。

CLR:異步清除,低有效。可用于將內(nèi)部寄存器A到D置0或者置為中間值(具體由CLSEL決定)。但數(shù)據(jù)在轉(zhuǎn)換寄存器時(shí)不受該控制信號(hào)的影響。

CLSEL:該端為低時(shí),CLR將寄存器A到D置0;為高時(shí),CLR將其置為中間值;

CS:片選信號(hào),低有效。與CLK信號(hào)相或。

LD:異步DAC寄存器載入控制,低有效。在LD的下降沿,串行輸入寄存器里面的數(shù)據(jù)將移到寄存器A~D。當(dāng)LD為低時(shí),輸入數(shù)據(jù)必須保持穩(wěn)定。

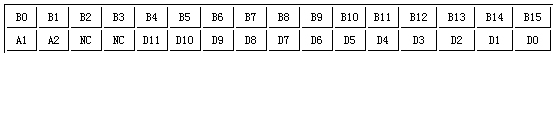

SDI:串行數(shù)據(jù)輸入。在輸入的16位數(shù)據(jù)中,頭兩位A1、A2用于選擇寄存器A~D,后12位D11~D0是具體數(shù)值,輸入的數(shù)據(jù)先進(jìn)入DAC內(nèi)部的串/并轉(zhuǎn)換寄存器。注意,當(dāng)CS為高時(shí),該數(shù)據(jù)無效。具體的數(shù)據(jù)輸入格式如下:

VREFHI:參考電壓高值端,取值范圍是VDD-2.5V~VREFLO+2.5V;

VREFLO:參考電壓低值端,當(dāng)輸入為0時(shí),輸出為VREFLO,取值范圍為VSS~VREFHI-2.5V。

VOUTA~VOUTD:電壓輸出端。

3 多路輸出D/A轉(zhuǎn)換電路

DAC8420能廣泛應(yīng)用于各種伺服控制和工業(yè)過程控制系統(tǒng)中,特別是在目前日益先進(jìn)的智能化儀表中(如總線儀表、轉(zhuǎn)換器等),其應(yīng)用將更加廣泛。

圖2是采用Motorola公司的16位微處理器MC68HC912作為主控芯片,通過DAC8420對(duì)CPU輸出的數(shù)字信號(hào)進(jìn)行模數(shù)和V/I轉(zhuǎn)換的接口電路。

由于本設(shè)計(jì)要求輸出4~20mA電流,而DAC的電壓輸出范圍選在1~5V,故參考電壓的選擇分別是:VREFLO=0VREFHI=+5V。REF02用于提供+5V基準(zhǔn)電壓。由于DAC的輸出范圍是VREFHI~VREFLO,因此,DAC輸出的最小值需利用軟件來進(jìn)行校正,以便充分發(fā)揮軟件優(yōu)勢,降低硬件成本。

由于MC68HC912的串行通信接口(SCI)可以方便的與DAC接口,因此,DAC和MC68HC912之間采用光電隔離來實(shí)現(xiàn)數(shù)模隔離。

MC68HC912向DAC寫數(shù)據(jù)時(shí),先將CS信號(hào)置0,并將LD信號(hào)置1,然后由MOSI引腳將符合DAC8420格式的數(shù)據(jù)分為兩個(gè)字節(jié)輸出。當(dāng)數(shù)據(jù)輸出完畢以后,再將LD置0,并在LD的下降沿將數(shù)據(jù)移入寄存器A~D,最后將LD置1、CS置1,以完成一次轉(zhuǎn)換。圖3是DAC8420的數(shù)據(jù)載入時(shí)序。