1 引言

傳統(tǒng)測(cè)試測(cè)量" title="測(cè)試測(cè)量">測(cè)試測(cè)量儀存在價(jià)格昂貴、體積龐大、數(shù)據(jù)傳輸速率低、存儲(chǔ)顯示困難等問題,本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛擬測(cè)試系統(tǒng)具有較強(qiáng)的競(jìng)爭(zhēng)力。本系統(tǒng)在FPGA單板單片主控器件控制下,實(shí)現(xiàn)兩路獨(dú)立、幅值可控的信號(hào)發(fā)生器,一路虛擬存儲(chǔ)示波器" title="示波器">示波器,具有外部觸發(fā)信號(hào)和采樣時(shí)鐘的16路高速邏輯分析儀。

2硬件設(shè)計(jì)

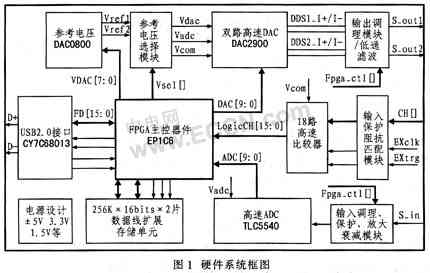

2.1硬件系統(tǒng)框圖

硬件系統(tǒng)設(shè)計(jì)是以并行處理能力強(qiáng)、可重配置的低端FPGA單片EP1C6為主控器件。圖1所示為硬件系統(tǒng)框圖,是由參考電壓及選擇模塊、USB2.0接口模塊、電源設(shè)計(jì)模塊、高速存儲(chǔ)模塊、示波器調(diào)理輸入A/D轉(zhuǎn)換模塊、邏輯分析儀匹配輸入比較模塊和信號(hào)源輸出濾波模塊組成。

USB2.0接口模塊用于配合應(yīng)用軟件接受上位機(jī)命令及返回采集數(shù)據(jù)。采用Cypress公司的CY7C68013 USB2.0設(shè)備器件,該器件內(nèi)部增強(qiáng)型8051控制數(shù)據(jù)傳輸。通過下載固件代碼配置8051,使設(shè)備器件對(duì)主控FPGA動(dòng)作模擬為片外從屬FI-FO,減少FPGA設(shè)計(jì)難度。電壓參考選擇模塊可為信號(hào)源D/A、比較器和示波器A/D提供參考電壓。考慮到多種測(cè)量功能間的切換及同時(shí)工作的可能,采用兩路參考電壓輸出和參考電壓通路選擇模塊實(shí)現(xiàn)雙路信號(hào)源獨(dú)立工作、單路信號(hào)源協(xié)同示波器工作、單路信號(hào)源協(xié)同邏輯分析儀工作等模式。

2.2雙路信號(hào)源設(shè)計(jì)

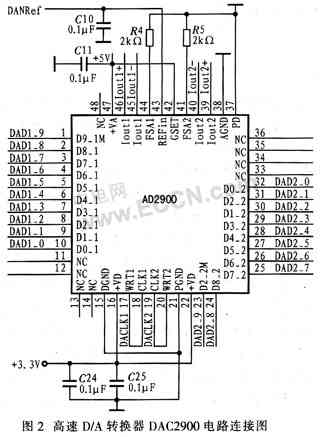

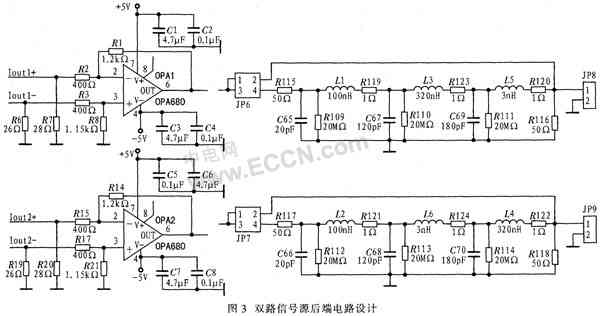

利用FPGA內(nèi)部M4K存儲(chǔ)模塊、邏輯資源和高頻時(shí)鐘,以DDS/控制模塊+高速D/A實(shí)現(xiàn)雙路信號(hào)源,避免采用專用DDS器件,從而節(jié)省成本,提高功能的多樣性。雙路信號(hào)源電路設(shè)計(jì)的前端模塊包括DDS方式實(shí)現(xiàn)的可變幅度、相位的正弦波以及硬件語言表述的占空比可調(diào)的方波、三角波、調(diào)制波形等數(shù)據(jù)輸出;后端包括有高速D/A轉(zhuǎn)換器DAC2900 (如圖2所示)和信號(hào)調(diào)理電路組成的模數(shù)轉(zhuǎn)換模塊(如圖3所示),其中調(diào)理模塊主要由強(qiáng)驅(qū)動(dòng)模塊和35 MHz截止頻率的3階π型低通網(wǎng)絡(luò)組成。

2.3高速邏輯分析儀及存儲(chǔ)示波器設(shè)計(jì)

高速邏輯分析儀的采樣率為150 MHz,對(duì)于16路采樣來說,數(shù)據(jù)量達(dá)到150 M×16 bit。采用兩片10 ns級(jí)的256 K×16 bit RAM擴(kuò)展數(shù)據(jù)位,實(shí)現(xiàn)降速存儲(chǔ)。位數(shù)擴(kuò)展1倍,存儲(chǔ)速率降低1倍,對(duì)于75 MHz的存儲(chǔ)速度,選用Cypress公司的CY7C-1041-8ns。RAM數(shù)據(jù)地址線和邏輯分析儀比較器接口與FPGA相連,RAM接口和存儲(chǔ)示波器相復(fù)用。

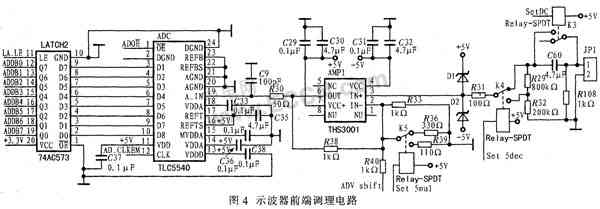

虛擬存儲(chǔ)示波器的設(shè)計(jì)采用前端調(diào)理和高速A/D采樣器件TLC5540實(shí)現(xiàn)。圖4為示波器前端調(diào)理電路,包括箝位電路、放大衰減網(wǎng)絡(luò)和功率放大3部分。箝位電路主要是將輸入電壓箝位于后端A/D的輸入范圍,防止電路損壞。通過示波器觀察箝位波形,打開衰減網(wǎng)絡(luò),反之,信號(hào)過小,打開放大網(wǎng)絡(luò)以實(shí)現(xiàn)高幅值帶寬。功率放大電路的目的在于提高信號(hào)的驅(qū)動(dòng)能力和測(cè)量精度。

板卡邏輯設(shè)計(jì)

3.1控制邏輯實(shí)現(xiàn)

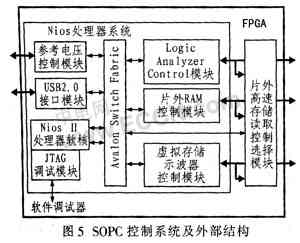

SOPC(System on Programmable Chip)技術(shù)是Altera公司于2000年最早提出的,提供了使用大規(guī)模可編程器件FPGA實(shí)現(xiàn)SOC功能。SOPC的引進(jìn)對(duì)僅為小批量應(yīng)用或處于開發(fā)階段SOC帶來有效解決方法。配合Altera公司提供的NIOS II軟核處理器生成高效的SOPC系統(tǒng)從而實(shí)現(xiàn)板卡控制設(shè)計(jì),簡化了數(shù)據(jù)通訊和模塊間的協(xié)調(diào)。圖5詳細(xì)介紹了SOPC系統(tǒng)組成。

由圖中可以看出,Avalon總線是整個(gè)系統(tǒng)的橋梁。Avalon接口規(guī)范是為可編程片上系統(tǒng)SOPC環(huán)境下外設(shè)的開發(fā)而設(shè)計(jì)的,為外設(shè)的設(shè)計(jì)者提供表述主外設(shè)和從外設(shè)中基于地址讀/寫接口的基礎(chǔ),是SOPC硬件系統(tǒng)的重要部分。

Nios II處理器軟核支持中斷異常和用戶自定義指令集等,完全支持C語言,并且可編寫用戶邏輯接口實(shí)現(xiàn)一個(gè)簡化的、無冗余的專用Nios II處理器系統(tǒng)。上位機(jī)指令可以完全以字符串的方式通過USB接口模塊發(fā)送給軟處理器,Nios軟核通過編程實(shí)現(xiàn)命令解析,并同時(shí)響應(yīng)輸出,配置各外設(shè),按命令完成指定作業(yè),返回?cái)?shù)據(jù)。FPGA內(nèi)部軟核通過GPIO和片外器件相連組成整個(gè)系統(tǒng)。 Nios II軟核處理器的優(yōu)點(diǎn)在于命令解析和Avalon外設(shè)總線位寬匹配,SOPC系統(tǒng)能高效完成邏輯分析儀和示波器的控制傳輸。然而,其數(shù)據(jù)傳輸在高速情況下略顯不足成為系統(tǒng)瓶頸,主要在于C語言指令集。而作為高速采集和存儲(chǔ)的邏輯分析儀、示波器和RAM之間接口的讀寫速率高于100M,實(shí)現(xiàn)高速采集通道,并對(duì)總線提供簡單的開始采集、采集結(jié)束、數(shù)據(jù)滿等信號(hào)作為外設(shè)掛接在Nios軟核上,是提高測(cè)量系統(tǒng)參數(shù)的關(guān)鍵。本系統(tǒng)在Nios軟核的基礎(chǔ)上,高速接口模塊采用Verilog HDL語言和FPGA內(nèi)部資源來實(shí)現(xiàn),即就是片外高速讀取控制模塊。

3.2改進(jìn)型低資源消耗率DDS的FPGA實(shí)現(xiàn)

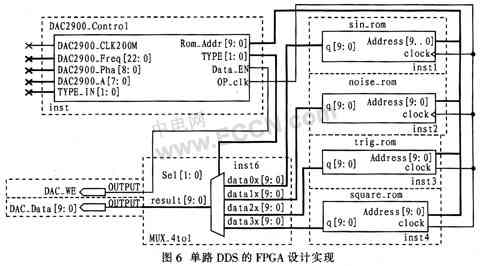

本系統(tǒng)基于FPGA實(shí)現(xiàn)雙路完全獨(dú)立的DDS信號(hào)源,硬件設(shè)計(jì)構(gòu)成了DDS技術(shù)實(shí)現(xiàn)的第三部分,前面兩部分相位累加器和查找表ROM設(shè)計(jì)細(xì)節(jié)介紹如圖6所示。

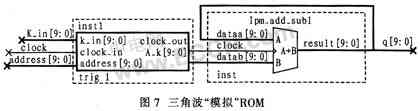

單路DDS的FPGA設(shè)計(jì)實(shí)現(xiàn)主要包括相位累加器地址產(chǎn)生及控制模塊、波形存儲(chǔ)及類型選擇模塊。相位累加器地址產(chǎn)生及控制模塊對(duì)接收到的控制指令實(shí)施執(zhí)行,并產(chǎn)生相應(yīng)的控制信號(hào)、尋址后端LUT ROM,實(shí)現(xiàn)DDS信號(hào)源。其翻譯及執(zhí)行的信號(hào)包括信號(hào)類型TYPE_IN、輸出信號(hào)相位DAC2900_Pha、輸出信號(hào)頻率DAC2900_Freq和輸出信號(hào)幅度DAC2900_A等。相位累加模塊根據(jù)輸入信號(hào)參數(shù),計(jì)算并產(chǎn)生地址,用以LUT ROM查找幅度值,輸出相位。而波形存儲(chǔ)模塊分為周期信號(hào)產(chǎn)生的正弦信號(hào)、鋸齒波信號(hào)以及方波信號(hào)和非周期的高斯噪聲信號(hào)。其中:sin_rom存儲(chǔ)的數(shù)據(jù)為量化的一個(gè)周期的正弦波數(shù)據(jù)。trig_rom塊并不是一個(gè)ROM模塊,而是一個(gè)三角波計(jì)算生成模塊。為了節(jié)省FPGA片內(nèi)RAM模塊,結(jié)合三角波的線性特性,利用地址產(chǎn)生三角波幅度值,實(shí)現(xiàn)如圖7所示,其中K_in[9:0]為產(chǎn)生的三角波波形設(shè)定斜率,clock、address和q[9:0]實(shí)現(xiàn)與sin_rom接口兼容。square_rom和trig_rom一樣,采用Verilog HDL模擬的查找表ROM,可有效減少對(duì)FPGA資源的占用,本設(shè)計(jì)的trig_rom僅占用一個(gè)10位加法器。noise_rom為改進(jìn)型加法同余偽隨機(jī)序列。數(shù)字隨機(jī)噪聲的設(shè)計(jì)也就是偽隨機(jī)序列設(shè)計(jì),其具有良好的隨機(jī)性,它的相關(guān)函數(shù)接近白噪聲的相關(guān)函數(shù)。偽隨機(jī)序列算法包括:平方取中算法、同余算法、小數(shù)開方法、Tausworthe序列。而同余算法包括加法同余數(shù)列、線性同余數(shù)列和乘進(jìn)位算法。結(jié)合各種算法及其在FPGA上的實(shí)現(xiàn)復(fù)雜度和資源重用率,設(shè)計(jì)了易于FPGA實(shí)現(xiàn)的改進(jìn)型加法同余偽隨機(jī)序列。

結(jié)束語

綜合考慮成本、性能和應(yīng)用等因素,充分利用FPGA的邏輯資源,實(shí)現(xiàn)了中低檔測(cè)量系統(tǒng)。雙路信號(hào)源獨(dú)立工作可產(chǎn)生最大2 MHz的無失真三角波、正弦波、方波及調(diào)制波形等;示波器可虛擬存儲(chǔ)采樣速率為40 MS/s;邏輯分析儀最高采樣頻率150 MHz,存儲(chǔ)深度256 K×32 bit。適用于教學(xué)試驗(yàn)。并協(xié)同上位機(jī)軟件和USB2.0接口實(shí)現(xiàn)便攜、即插即用。系統(tǒng)預(yù)留以太網(wǎng)接口,可實(shí)現(xiàn)測(cè)量設(shè)備網(wǎng)絡(luò)共享。同時(shí)還需進(jìn)一步提高系統(tǒng)復(fù)雜度,充分利用FPGA特點(diǎn),由上位機(jī)動(dòng)態(tài)配置板卡功能。