|

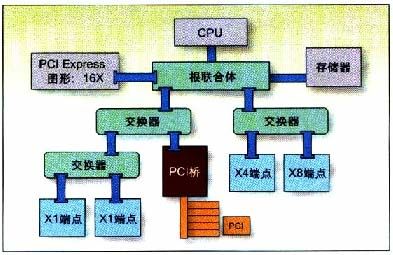

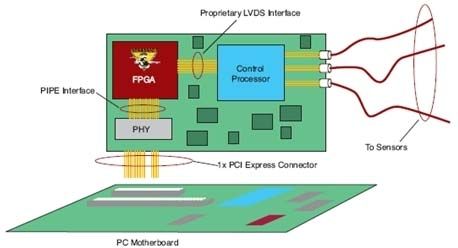

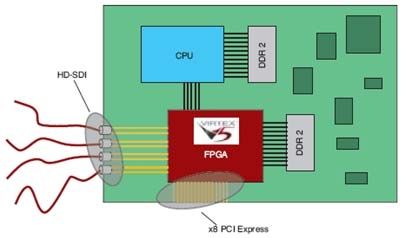

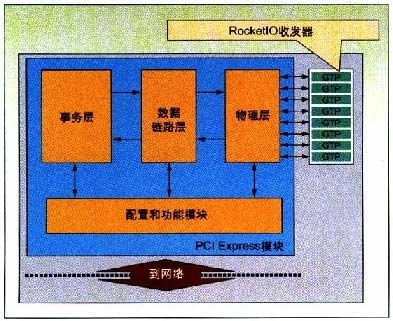

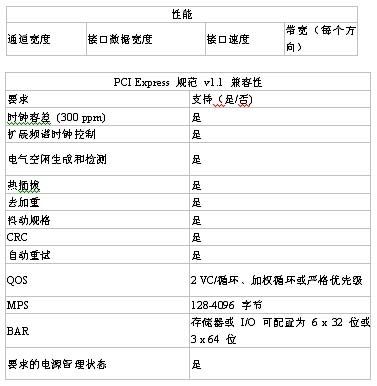

PCI Express是一種使用時(shí)鐘數(shù)據(jù)恢復(fù)(CDR)技術(shù)的高速串行I/O互連機(jī)制。PCI Express Gen1規(guī)范規(guī)定的線速率為每通道2.5Gbps,可以讓您建立具備單通道(x1)鏈路2Gbps(經(jīng)8B/10B編碼)直至32通道64Gbps吞吐量的應(yīng)用。這樣,就能在保持或改進(jìn)吞吐量的同時(shí),顯著減少引腳數(shù)量。另外,還可以減小PCB的尺寸、降低跡線和層的數(shù)量并簡化布局和設(shè)計(jì)。引腳數(shù)量減少,也就意味著噪聲和電磁干擾(EMI)降低。CDR消除了寬并行總線中普遍存在的時(shí)鐘-數(shù)據(jù)歪斜問題,簡化了互連實(shí)現(xiàn)。 PCI Express互連架構(gòu)主要針對基于臺式/膝上(PC)的系統(tǒng)。但就像PCI一樣,PCI Express也很快轉(zhuǎn)移到其他系統(tǒng)類型,如嵌入式系統(tǒng)。它規(guī)定了三種類型器件:根聯(lián)合體(root complex)、交換器件和端點(diǎn)(圖1)。根聯(lián)合體大致等同于PCI主機(jī),CPU、系統(tǒng)存儲器和圖形控制器與之相連接。由于PCI Express的點(diǎn)對點(diǎn)特性,必須使用交換器件來增加系統(tǒng)功能的數(shù)量。PCI Express交換器件將上游端的根聯(lián)合體器件連接到下游端的端點(diǎn)。  圖1:PCI Express拓?fù)洹?br /> 端點(diǎn)功能類似于PCI/PCI-X器件。最常用的端點(diǎn)器件有以太網(wǎng)控制器或存儲HBA(主機(jī)總線適配器)。FPGA最常用于數(shù)據(jù)處理和橋接功能,所以其最大目標(biāo)功能就是端點(diǎn)。FPGA實(shí)現(xiàn)非常適合于視頻、醫(yī)療影像、工業(yè)、測試和測量、數(shù)據(jù)采集和存儲應(yīng)用。  圖2:基于Spartan-3 FPGA的數(shù)據(jù)采集卡。 PCI特別興趣小組(PCI-SIG)采用的PCI Express規(guī)范規(guī)定每個(gè)PCI Express器件使用三個(gè)不同的協(xié)議層:物理層、數(shù)據(jù)鏈路層和事務(wù)層。您可以使用單芯片或雙芯片解決方案來構(gòu)建PCI Express端點(diǎn)。例如,使用Xilinx Spartan-3器件之類的低成本FPGA,您可以用商用離散PCI Express PHY(圖2)來構(gòu)建數(shù)據(jù)鏈路和事務(wù)層。此選項(xiàng)最適合于x1通道應(yīng)用,如:總線控制器、數(shù)據(jù)采集卡和提高性能的PCI 32/33器件。或者,您可以使用類似Virtex-5 LXT或SXT FPGA的單芯片解決方案,它們具備集成的PCI Express PHY。此選項(xiàng)最適合于通訊或高清晰度音頻/視頻端點(diǎn)器件(圖3),它們對性能的要求更高:x4(8Gbps吞吐量)鏈路或x8(16Gbps吞吐量)鏈路。  圖3:基于Virtex-5 LXT FPGA的視頻應(yīng)用。 在選擇一種技術(shù)來實(shí)現(xiàn)PCI Express設(shè)計(jì)之前,必須仔細(xì)考慮應(yīng)用的IP選擇、鏈路效率、兼容性測試及資源可用性。本文中,我們將簡要介紹使用最新的FPGA技術(shù)構(gòu)建單芯片x4和x8通道PCI Express設(shè)計(jì)的一些因素。 IP的選擇 作為設(shè)計(jì)人員,您可以選擇構(gòu)建自己的軟IP或者向第三方或FPGA供應(yīng)商購買IP。構(gòu)建自己的IP的難題在于,您不光得從零開始創(chuàng)建設(shè)計(jì),還得擔(dān)心驗(yàn)證、批準(zhǔn)、兼容性和硬件評估等環(huán)節(jié)。向第三方或FPGA供應(yīng)商購買的IP,已經(jīng)過所有嚴(yán)格的兼容性測試和硬件評估,可以即插即用。如果使用商用的、已驗(yàn)證的兼容性PCI Express接口,您可以把精力集中在設(shè)計(jì)中最有附加值的部分:用戶應(yīng)用。使用軟IP的難題在于應(yīng)用的資源可用性。軟IP核的PCI Express MAC層、數(shù)據(jù)鏈路層和事務(wù)層通過可編程架構(gòu)實(shí)現(xiàn),因此您必須特別注意剩余Block RAM、查找表和架構(gòu)資源的數(shù)量。 另一選擇是使用最新技術(shù)的FPGA。Virtex-5 LXT和SXT的專用門電路(圖4)中實(shí)現(xiàn)了集成x8通道PCI Express控制器。這種實(shí)現(xiàn)極具優(yōu)勢,因?yàn)樵O(shè)計(jì)是在硬硅片中實(shí)現(xiàn)的,所以需要的FPGA邏輯資源數(shù)量達(dá)到了最小。例如,在Virtex-5 LXT FPGA中,一個(gè)x8通道軟IP核可占用多達(dá)10,000個(gè)邏輯單元,而硬實(shí)現(xiàn)只需要大約500個(gè)邏輯單元,多數(shù)用于接口。這樣的資源節(jié)省有時(shí)候能允許您選擇更小的器件,而器件越小通常就會越便宜。集成實(shí)現(xiàn)通常具有更高的性能、更寬的數(shù)據(jù)通路,并且可通過軟件配置。  圖4:Virtex-5 LXT FPGA PCI Express端點(diǎn)框圖。 軟IP實(shí)現(xiàn)的另一難題是功能的數(shù)量。通常,此類核僅實(shí)現(xiàn)滿足性能或兼容性目標(biāo)規(guī)范所要求的最少功能。相反,硬IP可以支持基于客戶要求的全面功能列表,并提供完全的兼容性(表1),且不存在嚴(yán)重的性能或資源相關(guān)的問題。  表1:Virtex-5 LXT FPGA PCI Express功能。 |

延遲

盡管PCI Express控制器的延遲不會對總體系統(tǒng)延遲有很大的影響,但卻會影響接口的性能。使用較窄的數(shù)據(jù)通路有助于減少延遲。

對PCI Express來說,延遲就是發(fā)送包并穿過物理層、邏輯層和事務(wù)層接收包所需的周期數(shù)。典型的x8通道PCI Express端點(diǎn)的延遲為20~25周期。250MHz下,轉(zhuǎn)換為80~100ns。如果使用128位的數(shù)據(jù)通路實(shí)現(xiàn)接口來簡化時(shí)序(如125MHz),延遲會加倍為160~200ns。在最新的Virtex-5 LXT和SXT器件中,無論是軟IP實(shí)現(xiàn)還是硬IP實(shí)現(xiàn),都采用250MHz下的64位數(shù)據(jù)通路進(jìn)行x8實(shí)現(xiàn)。

鏈路效率

鏈路效率是延遲、用戶應(yīng)用設(shè)計(jì)、有效載荷大小和額外開銷的函數(shù)。隨著有效載荷大小(通常稱為最大有效載荷)的增加,有效鏈路效率也會增加。這是由包的額外開銷固定不變這一事實(shí)造成的;如果有效載荷大,效率就提高。一般情況下,256字節(jié)的有效載荷可提供93%的理論效率(256有效載荷字節(jié)+12頭字節(jié)+8幀字節(jié))。盡管PCI Express允許的包大小可達(dá)4KB,但如果有效載荷大小大于256或512字節(jié),大多數(shù)系統(tǒng)的性能都無法提高。由于鏈路協(xié)議額外開銷(ACK/NAK、重新發(fā)送包)和流程控制協(xié)議(授權(quán)報(bào)告),在Virtex-5 LXT FPGA中實(shí)現(xiàn)x4或x8 PCI Express的鏈路效率為88~89%。

利用FPGA實(shí)現(xiàn)可以更好地控制鏈路效率,因?yàn)樗试S您選擇與端點(diǎn)實(shí)現(xiàn)對應(yīng)的接收緩沖器尺寸。如果鏈接雙方不是采用相同的方式實(shí)現(xiàn)數(shù)據(jù)通路,則二者的內(nèi)部延遲會不同。例如,如果一號鏈接方使用64位、250MHz實(shí)現(xiàn),延遲為80ns,而二號鏈接方使用128位、125MHz實(shí)現(xiàn),延遲為160ns,該鏈路的組合延遲即為240ns。現(xiàn)在,如果一號鏈接方的接收緩沖器設(shè)計(jì)成160ns的延遲(即期待其鏈接對方也是64位、250MHz實(shí)現(xiàn)),那么鏈路效率就會降低。如果采用ASIC實(shí)現(xiàn),就不可能改變接收緩沖器的尺寸,效率損失將是實(shí)實(shí)在在的,而且是永久性的。

用戶應(yīng)用設(shè)計(jì)也會對鏈路效率有所影響。用戶應(yīng)用必須設(shè)計(jì)成定期排空PCI Express接口的接收緩沖器,并保持發(fā)送緩沖器時(shí)刻充滿。如果用戶應(yīng)用不立即使用接收的包(或者不立即響應(yīng)發(fā)送請求),無論接口的性能如何,總鏈路效率都會受到影響。

使用某些處理器設(shè)計(jì)時(shí),如果處理器不能執(zhí)行大于1DWORD的突發(fā),則需要實(shí)現(xiàn)一個(gè)DMA控制器。這將造成鏈路利用不充分,效率不佳。大多數(shù)嵌入式CPU可以發(fā)送長于1DWORD的突發(fā),所以通過良好的FIFO設(shè)計(jì)就可以有效地管理這些設(shè)計(jì)的鏈路效率。

PCI Express兼容性

兼容性是經(jīng)常被遺漏和低估的重要細(xì)節(jié)。如果要構(gòu)建必須與其他器件和應(yīng)用結(jié)合使用的PCI Express應(yīng)用,則必須確保設(shè)計(jì)的兼容性。

兼容性不只針對IP,而是針對整個(gè)解決方案,包括IP、用戶應(yīng)用、硅片器件和硬件板。如果整個(gè)解決方案已經(jīng)過PCI-SIG PCI Express兼容性研討會(別號“plug fest”)驗(yàn)證,就基本保證了您設(shè)計(jì)的PCI Express部分會一直有效。

本文小結(jié)

PCI Express已替代PCI成為事實(shí)上的系統(tǒng)互連標(biāo)準(zhǔn),并且已從PC轉(zhuǎn)移到其他系統(tǒng)市場,包括嵌入式系統(tǒng)設(shè)計(jì)。

FPGA非常適合于構(gòu)建PCI Express端點(diǎn)器件,因?yàn)樗试S您創(chuàng)建帶有用戶所需的附加定制功能的兼容性PCI Express器件。

類似Virtex-5 LXT和SXT系列的新65nm FPGA完全符合PCI Express規(guī)范v1.1,并為用戶應(yīng)用提供廣泛的邏輯和器件資源。使用外部PHY的Spartan-3系列FPGA提供了低成本解決方案。這些因素,加上內(nèi)在的可編程邏輯優(yōu)勢(靈活性、可再編程性和低風(fēng)險(xiǎn))使FPGA成為PCI Express的最佳平臺。