引言

傳統(tǒng)的邏輯分析儀體積龐大、價(jià)格昂貴、通道數(shù)目有限,并且在數(shù)據(jù)采集、傳輸、存儲(chǔ)、顯示等方面存在諸多限制,在很大程度上影響了其在實(shí)際中的應(yīng)用。選用高性能的FPGA芯片進(jìn)行數(shù)據(jù)處理,充分利用PC的強(qiáng)大處理功能,配合LabView圖形化語言開發(fā)的虛擬邏輯分析儀,其數(shù)據(jù)處理和傳輸速率大大提高,適用性極大增強(qiáng),其顯示、操作界面和低廉的成本較之傳統(tǒng)的邏輯分析儀具有極大的優(yōu)勢(shì)和發(fā)展前景。

工作原理

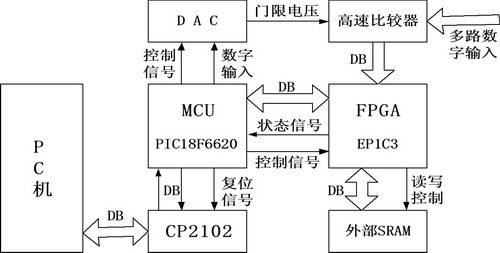

本設(shè)計(jì)選用Altera公司的Cyclone系列FPGA器件EP1C3進(jìn)行數(shù)據(jù)采集和處理,外接SRAM,用于數(shù)據(jù)的存儲(chǔ)。系統(tǒng)通過高性能的PIC單片機(jī)PIC18F6620完成與PC的通信,接收PC發(fā)出的觸發(fā)、配置信息并控制系統(tǒng)將采集處理后的數(shù)據(jù)上傳至PC顯示。單片機(jī)與PC的接口利用符合USB2.0規(guī)范的接口芯片CP2102實(shí)現(xiàn)。

首先,PC向FPGA發(fā)送觸發(fā)字信息、數(shù)據(jù)采集控制信息和開啟數(shù)據(jù)采集信號(hào);單片機(jī)發(fā)送數(shù)據(jù)至外接DAC產(chǎn)生門限電壓;采集到的輸入信號(hào)通過高速比較器與此門限電壓進(jìn)行比較,以確定其值為0或1。接收到PC發(fā)出的開啟數(shù)據(jù)采集信號(hào)后,F(xiàn)PGA按設(shè)定的工作方式采集數(shù)據(jù),各通道數(shù)據(jù)移位輸入FPGA內(nèi)部緩存并存入外部SRAM。FPGA將緩存中存儲(chǔ)的采集數(shù)據(jù)與設(shè)定的觸發(fā)字、觸發(fā)方式和屏蔽位進(jìn)行比較。一旦符合觸發(fā)條件,則設(shè)置觸發(fā)標(biāo)志,記錄觸發(fā)位置。當(dāng)數(shù)據(jù)采集至設(shè)定的點(diǎn)數(shù)后,F(xiàn)PGA向PC發(fā)送采集完成信號(hào)。上位機(jī)接收到此信號(hào)后,發(fā)送讀取數(shù)據(jù)命令,系統(tǒng)讀回采集數(shù)據(jù)并在PC屏上顯示。系統(tǒng)功能框圖如圖1所示。

圖1 系統(tǒng)功能框圖

系統(tǒng)觸發(fā)模塊設(shè)計(jì)

觸發(fā)模塊是整個(gè)系統(tǒng)的核心部分,主要包括采樣時(shí)鐘選擇模塊、觸發(fā)電平設(shè)置和觸發(fā)電路三個(gè)部分。

采樣時(shí)鐘選擇模塊

時(shí)鐘選擇模塊用于選擇采樣頻率。可供選擇的時(shí)鐘源包括:外部時(shí)鐘(由有源晶振提供)、單片機(jī)PWM模塊產(chǎn)生的PWM時(shí)鐘、外部時(shí)鐘輸入(由額外的設(shè)備提供)、以第N路數(shù)字信號(hào)輸入作為采樣時(shí)鐘。

觸發(fā)電平設(shè)置

觸發(fā)電平用來確定系統(tǒng)正確識(shí)別采樣信號(hào)的高低電平。該模塊由串行數(shù)模轉(zhuǎn)換器TLC5615和高速比較器LT1721構(gòu)成。采樣開始前,單片機(jī)向DAC發(fā)送觸發(fā)電平數(shù)據(jù),轉(zhuǎn)換后的電平信號(hào)(范圍從0~+5V)送入高速比較器。

觸發(fā)電路

觸發(fā)電路的作用是判斷采樣信號(hào)是否滿足觸發(fā)條件,并分別產(chǎn)生觸發(fā)動(dòng)作。當(dāng)采集的信號(hào)滿足用戶設(shè)置的觸發(fā)條件時(shí),系統(tǒng)記錄觸發(fā)位置并產(chǎn)生觸發(fā)信號(hào)通知上位機(jī)讀取、顯示采樣數(shù)據(jù)。本次設(shè)計(jì)的觸發(fā)電路具有三種可選的觸發(fā)模式:立即觸發(fā)、順序觸發(fā)和并行觸發(fā)。

立即觸發(fā)

當(dāng)上位機(jī)向FPGA發(fā)出立即觸發(fā)觸發(fā)字和開始采樣指令后,F(xiàn)PGA開始采樣并立即產(chǎn)生觸發(fā)信號(hào)。采樣電路將采集到的信號(hào)存入外部的SRAM中,直至采集到規(guī)定的點(diǎn)數(shù)后停止采樣,向上位機(jī)發(fā)出采樣結(jié)束信號(hào),通知其讀取采樣數(shù)據(jù)。此方式下讀回的觸發(fā)點(diǎn)位置為0。

順序觸發(fā)

該方式設(shè)置了一個(gè)8位的序列觸發(fā),只有當(dāng)被測(cè)通道的信號(hào)按依次滿足觸發(fā)字所設(shè)定的8位序列時(shí),才產(chǎn)生觸發(fā)信號(hào)。同時(shí),為了操作的靈活性,還加入了屏蔽位。若對(duì)某一位的數(shù)據(jù)不敏感,可以將其對(duì)應(yīng)的屏蔽位設(shè)置為0,在判斷觸發(fā)條件時(shí)不對(duì)該位進(jìn)行檢測(cè)。

使用順序觸發(fā)方式,可以對(duì)任意一個(gè)通道選擇最多8位長度的序列進(jìn)行觸發(fā)。在進(jìn)行觸發(fā)設(shè)置時(shí),除設(shè)置觸發(fā)方式(選擇順序觸發(fā))和進(jìn)行采樣頻率選擇以外,還需要進(jìn)行通道選擇、觸發(fā)字和屏蔽位設(shè)置。其Verilog HDL算法源程序如下:

if(((dbuf^{TrigWord[1],TrigWord[ 0]})&{enbit[1],enbit[0]}) == 8'h00)

begin

TrigFlag=2'b01; Trigpoint[6:0] <= MemABus_Wr[6:0];

end

其中:dbuf為所測(cè)采樣通道的數(shù)據(jù)緩存;TrigWord[0]、TrigWord[1]為觸發(fā)字;enbit[0]、enbit[1]為屏蔽字;Trigpoint為觸發(fā)位置寄存器。

并行觸發(fā)

該方式設(shè)置了一個(gè)八級(jí)深度的并行觸發(fā),將每次采樣得到的4個(gè)通道的數(shù)據(jù)組合為一個(gè)十六進(jìn)制數(shù),對(duì)應(yīng)于一個(gè)4位的觸發(fā)字,當(dāng)4個(gè)通道的數(shù)據(jù)在時(shí)間上依次滿足8個(gè)4位的觸發(fā)字時(shí)(并非要求連續(xù)),產(chǎn)生觸發(fā)信號(hào)。同樣,可以使用屏蔽位對(duì)某一通道的數(shù)據(jù)進(jìn)行屏蔽,即在進(jìn)行并行觸發(fā)檢測(cè)時(shí),不對(duì)該路通道進(jìn)行檢測(cè)。

使用并行觸發(fā)方式,可以選擇最多八級(jí)的并行觸發(fā)。在進(jìn)行觸發(fā)設(shè)置時(shí),除設(shè)置觸發(fā)方式(選擇并行觸發(fā))和進(jìn)行頻率選擇以外,還需要進(jìn)行觸發(fā)字、屏蔽位和并行深度的設(shè)置。其Verilog HDL算法源程序如下:

if ((({dbuf4[0],dbuf3[0], dbuf2[0],dbuf1[0]}^ TrigWord [dcount] )&enbit[0] ) == 4'h0)

begin

if(dcount[2:0]==control[4:2])

begin

TrigFlag=2'b01; Trigpoint[6:0] <= MemABus_Wr[6:0];

dcount=3'b000; end

dcount = dcount+3'b001;

end

其中,dbuf4、dbuf3、dbuf2、dbuf1分別為采樣通道4、3、2、1的數(shù)據(jù)緩存;TrigWord[dcount]為觸發(fā)字;dcount為觸發(fā)深度計(jì)數(shù)器;control[4:2]為設(shè)定的觸發(fā)深度;enbit[0]為屏敝字;Trigpoint為觸發(fā)位置寄存器。

USB2.0接口設(shè)計(jì)

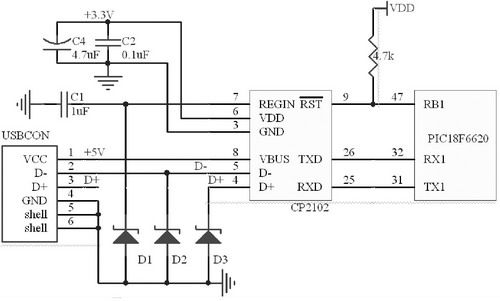

本設(shè)計(jì)選用符合USB2.0規(guī)范的CP2102芯片構(gòu)建系統(tǒng)與PC的通信接口。

CP2102是USB-UART橋接芯片。該電路內(nèi)置USB2.0全速功能控制器、USB收發(fā)器、晶體振蕩器、EEPROM及異步串行數(shù)據(jù)總線,支持調(diào)制解調(diào)器全功能信號(hào),無需任何外部的USB器件。其功能強(qiáng)大,采用MLP-28封裝,尺寸僅為5mm×5mm,占用空間非常小,非常適合大數(shù)據(jù)量處理與傳輸電路系統(tǒng)的設(shè)計(jì)與應(yīng)用。

實(shí)際應(yīng)用中,系統(tǒng)只需使用CP2102基本的輸入/輸出數(shù)據(jù)線與復(fù)位信號(hào)線。其接口原理如圖2所示。

系統(tǒng)啟動(dòng)時(shí), 單片機(jī)RB1端口發(fā)送一低電平至CP2102復(fù)位端,芯片復(fù)位,然后保持復(fù)位端高電平,CP2102正常工作。

圖2 USB2.0接口電路圖

由于CP2102內(nèi)部的透明設(shè)計(jì),數(shù)據(jù)通信時(shí),可以不必構(gòu)建CP2102與單片機(jī)的握手信號(hào);CP2102數(shù)據(jù)線直接與單片機(jī)1#USART模塊的接收移位寄存器(RSR)和發(fā)送移位寄存器(TSR)相連。CP2102數(shù)據(jù)線上一旦出現(xiàn)待發(fā)送的數(shù)據(jù),該數(shù)據(jù)會(huì)自動(dòng)移入單片機(jī)接收移位寄存器;同樣,單片機(jī)發(fā)送數(shù)據(jù)時(shí),發(fā)送移位寄存器中的數(shù)據(jù)直接移至CP2102的數(shù)據(jù)線(即USB接口數(shù)據(jù)線)上。

程序設(shè)計(jì)中,系統(tǒng)不斷檢測(cè)單片機(jī)接收中斷標(biāo)志位RCIF1,一旦USART異步接收器的移位寄存器RSR接收到CP2102數(shù)據(jù)線上發(fā)送的停止位,RSR寄存器就將已接收的8位數(shù)據(jù)裝載到接收寄存器(RCREG1)中。系統(tǒng)發(fā)送數(shù)據(jù)時(shí),前次裝入發(fā)送緩沖器(TXREG1)的數(shù)據(jù)的停止位P發(fā)送出去后,TXREG1緩沖器中的數(shù)據(jù)(軟件裝入)就被載入TSR寄存器中,TXREG1緩沖器就為空狀態(tài),同時(shí)發(fā)送中斷標(biāo)志位TXIF被置1。TSR將待發(fā)送數(shù)據(jù)逐位移至CP2102數(shù)據(jù)線,完成系統(tǒng)與CP2102 USB模塊的數(shù)據(jù)傳輸。

軟件設(shè)計(jì)

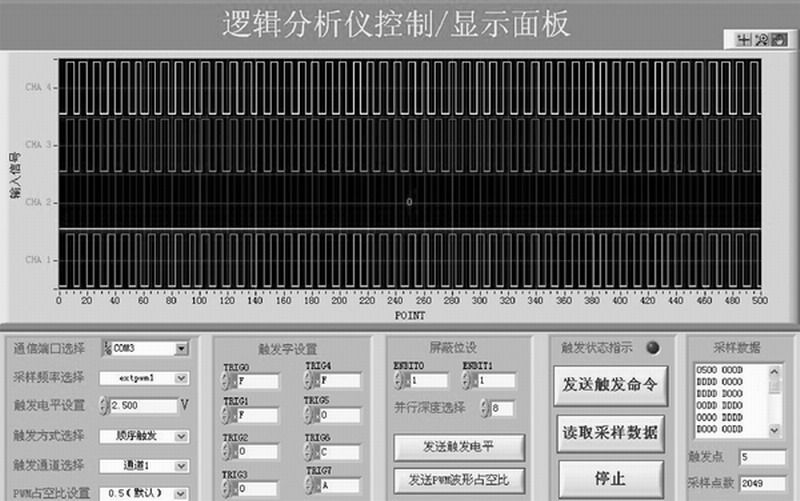

FPGA功能實(shí)現(xiàn)程序運(yùn)用硬件描述語言Verilog HDL編寫;PIC單片機(jī)程序用C語言編寫,并采用第三方C語言工具HITECH公司PICC—18編譯器編譯實(shí)現(xiàn)。PC顯示和操作部分運(yùn)用圖形化語言LabView7.1編寫,其前面板如圖3所示。

圖3 系統(tǒng)面板

實(shí)驗(yàn)操作

采用LabView7.1開發(fā)的虛擬操作平臺(tái),可以方便實(shí)現(xiàn)儀器的操作控制。實(shí)驗(yàn)開始前,首先選擇通信端口,建立PC與本系統(tǒng)的通信;設(shè)置觸發(fā)電平,設(shè)置采樣頻率(外部、內(nèi)部或其他)、觸發(fā)方式、觸發(fā)字、屏蔽字并點(diǎn)擊“發(fā)送觸發(fā)命令”按鈕,完成相關(guān)設(shè)置,開啟數(shù)據(jù)采集和觸發(fā)進(jìn)程。點(diǎn)擊“讀取采樣數(shù)據(jù)”可讀出采集到的數(shù)據(jù),并在PC上顯示。

結(jié)語

在綜合考慮應(yīng)用需要和成本的前提下,本設(shè)計(jì)采用4個(gè)高速采樣通道,最高可達(dá)75MHz采樣率,存儲(chǔ)深度達(dá)512KB,最多可采集220個(gè)測(cè)試點(diǎn)。觸發(fā)電平由10位串行數(shù)模轉(zhuǎn)換器TLC5615產(chǎn)生,電平誤差小于5mV。高速USB2.0通信接口配合LabView7.1開發(fā)的虛擬操作平臺(tái),可實(shí)現(xiàn)數(shù)據(jù)在PC上的實(shí)時(shí)顯示。本設(shè)計(jì)的成本還不到市場(chǎng)上同性能產(chǎn)品的1/2,更適用于教學(xué)等對(duì)產(chǎn)品數(shù)量要求較多,性能要求中等的單位采用。

參考文獻(xiàn)

1.鄧火炎,王磊,等編著.Labview 7.1測(cè)試技術(shù)與儀器應(yīng)用[M].機(jī)械工業(yè)出版社,2004.7

2. Silicon Laboratories.CP2102 DataSheet. Rev. 1.0 2004.4.

3. 劉和平 等編著.PIC18Fxxx單片機(jī)程序設(shè)計(jì)及應(yīng)用[M].北京航空航天大學(xué)出版社, 2005.2