電磁干擾(EMI)是一種會(huì)通過(guò)導(dǎo)致意外響應(yīng)或完全工作實(shí)效從而影響電氣/電子設(shè)備性能的能量。

EMI是由輻射電磁場(chǎng)或者感應(yīng)電壓和電流產(chǎn)生的。當(dāng)前高速數(shù)字系統(tǒng)中的高時(shí)鐘頻率和短邊率也會(huì)導(dǎo)致EMI問(wèn)題。

傳導(dǎo)和發(fā)射EMI的一個(gè)重要產(chǎn)生源是連接交流電源線的電氣設(shè)備,例如電腦和開關(guān)電源,以及帶有電動(dòng)馬達(dá)的電氣設(shè)備,例如冰箱、空調(diào)和電單車等。

一旦電氣設(shè)備的EMI傳導(dǎo)到一個(gè)電路里,里面的線纜就會(huì)像一根天線一樣,將傳導(dǎo)EMI以RFI(無(wú)線電干擾)的形式“廣播”到整個(gè)電路中。

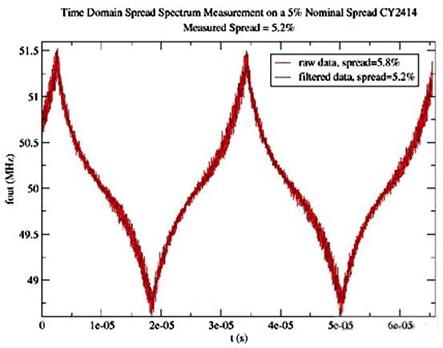

圖1:時(shí)鐘域里的Hershey Kiss展頻時(shí)鐘頻率概圖。

EMI可能影響不大,也可能導(dǎo)致災(zāi)難性的故障,所以對(duì)EMI的有效控制是非常重要的。電磁兼容性(EMC)是指系統(tǒng)能在指定環(huán)境下運(yùn)行而不會(huì)傳導(dǎo)或發(fā)射過(guò)量電池干擾的能力。

EMI標(biāo)準(zhǔn)和相關(guān)成本

EMC標(biāo)準(zhǔn)的宗旨是為了確保電子設(shè)備不會(huì)影響其它電子設(shè)備的運(yùn)行甚至導(dǎo)致設(shè)備的故障。

各國(guó)針對(duì)“電視、廣播、便攜式娛樂(lè)設(shè)備、電子游戲和互聯(lián)網(wǎng)設(shè)備”等消費(fèi)電子設(shè)備的EMI屏蔽功能的要求各有不同。

目前為止已經(jīng)有各種各樣的組織發(fā)布了EMI規(guī)范。在美國(guó),F(xiàn)CC發(fā)布了針對(duì)A?級(jí)和B級(jí)電子設(shè)備的第15部分J章規(guī)范。A?級(jí)和A層規(guī)范針對(duì)的是工業(yè)設(shè)備,而B級(jí)和B層規(guī)范則適用于消費(fèi)電子產(chǎn)品。EMI規(guī)則減少了電子設(shè)備之間的干擾,解決了健康和安全方面的問(wèn)題。

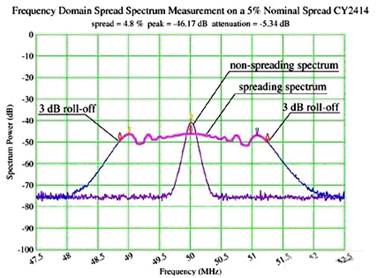

圖2:頻率域里的展頻時(shí)鐘頻率概圖。

如何控制EMI,一般要考慮以下幾個(gè)因素:

1) PCB設(shè)計(jì)-“靈敏元件、電源和地面層的隔離”

2) 電路電流-“EMI輻射會(huì)隨電流增大而增加”

3) 頻率,包括回轉(zhuǎn)率-“EMI輻射會(huì)導(dǎo)致頻率升高”

4) 帶寬

5) 電路回路區(qū)域-“保持在最小”

6) 屏蔽/過(guò)濾-“結(jié)合合理的設(shè)計(jì)、過(guò)濾、屏蔽和其它技巧,來(lái)以最低成本的方法將EMI控制在所需等級(jí)”

7) 展頻時(shí)鐘-“合適的展頻數(shù)量和調(diào)制頻率”

8) 抖動(dòng)應(yīng)用系統(tǒng)中時(shí)鐘的中心頻率,以便將輻射能量擴(kuò)展到多個(gè)頻段,而不是讓所有能量輻射到一個(gè)頻率。

控制和降低EMI的方法

控制和降低EMI有兩個(gè)基本方法:抑制和吸收。最常用的降噪方法包括合理的設(shè)備電路設(shè)計(jì)、屏蔽、接地、過(guò)濾、隔離、分隔和定向、電路阻抗級(jí)控制、線纜設(shè)計(jì)和噪音消除等。

這些方法要求使用無(wú)源和有源元件,例如濾波器、扼流器、鐵氧體磁珠、箔片和??件,并結(jié)合PCB設(shè)計(jì)規(guī)則和展頻時(shí)鐘生成器(SSCG)。

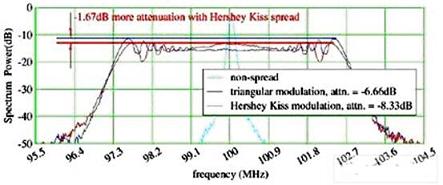

圖3:Hershey Kiss展頻概圖的優(yōu)勢(shì)。

在源頭處解決EMI問(wèn)題

EMC設(shè)計(jì)的一個(gè)基本原則是在PCB的源頭處減弱EMI。展頻法是指有意將特別帶寬中產(chǎn)生的輻射能量擴(kuò)展到頻率域,產(chǎn)生一個(gè)帶寬更大的信號(hào)。展品時(shí)鐘生成器(SSCG)就可以執(zhí)行這一功能。

在選擇展頻時(shí)鐘來(lái)減弱消費(fèi)電子產(chǎn)品的EMI時(shí),開發(fā)人員必須確保以下幾點(diǎn):

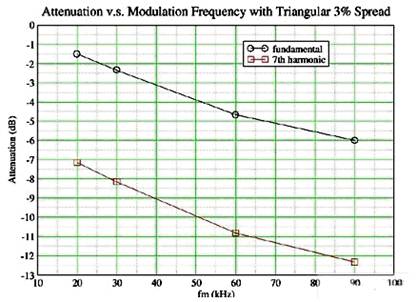

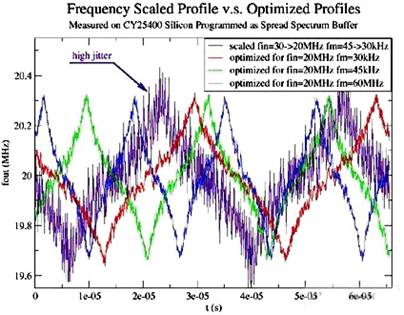

1) 系統(tǒng)必須通過(guò)EMI型式測(cè)試。良好的頻率概圖和調(diào)制頻率是最重要的。高質(zhì)量的Hershey Kiss頻率概圖在降低EMI上是性能最好的;與之相比,三角頻率概圖需要更大的擴(kuò)展量才能將EMI降低到同樣等級(jí)(見(jiàn)圖1至圖3)。調(diào)制頻率越高,就能將EMI降到更低的程度(如圖4)。

2)即便展頻有副作用,也要保持系統(tǒng)性能。首先,PLL必須運(yùn)行于一個(gè)理想狀態(tài),例如較高的PFD和VCO頻率和適當(dāng)?shù)膸挼鹊取5诙l率擴(kuò)展量必須盡可能小,以便保持較高的系統(tǒng)時(shí)序余度和較低的周期間抖動(dòng)。頻率擴(kuò)展量更小,系統(tǒng)的平均頻率就不會(huì)降低太多,因而系統(tǒng)的運(yùn)行速度也就不會(huì)那么慢。

3)要將對(duì)系統(tǒng)總成本的影響最小化。在消費(fèi)電子產(chǎn)品中,展頻時(shí)鐘芯片的價(jià)格向來(lái)是一個(gè)主要的價(jià)格問(wèn)題。但是,在最近幾年消費(fèi)電子產(chǎn)品復(fù)雜性越來(lái)越高的同時(shí),開發(fā)人員也要慎重考慮開發(fā)成本和風(fēng)險(xiǎn)。

比如,在抑制EMI和抖動(dòng)中即便只有一項(xiàng)要求沒(méi)有達(dá)到,消費(fèi)電子產(chǎn)品的系統(tǒng)時(shí)鐘需要調(diào)整的可能性就更大。可編程型抑制EMI的方法的靈活性,可以大大降低開發(fā)成本和風(fēng)險(xiǎn),從而確保滿足所有要求。

圖4:通過(guò)調(diào)制頻率降低EMI。

展頻時(shí)鐘生成器

展頻時(shí)鐘生成器(SSCG)可分成可編程和不可編程兩種,也可以根據(jù)其是否有Hershey Kiss頻率還是三角展頻來(lái)分類。不同消費(fèi)電子產(chǎn)品的展頻時(shí)鐘對(duì)于頻率、中心或向下擴(kuò)展、擴(kuò)展量、調(diào)制頻率、Hershey Kiss或三角展頻等的要求是不同的。

由于非可編程式展頻時(shí)鐘芯片是為特殊應(yīng)用定制的,頻率范圍和擴(kuò)展量只有幾個(gè)固定的可選項(xiàng),要在最大化成本/性能的同時(shí)滿足最優(yōu)展頻要求,就變得非常困難。

市場(chǎng)上大部分固定功能的時(shí)鐘芯片都有多個(gè)固定的可選擇輸入頻率范圍(如20-40MHz, 40-80MHz和80-160MHz)以及擴(kuò)展率(如0.5%, 1%, 2%和3%)。要實(shí)現(xiàn)優(yōu)化,就需要兩套PLL參數(shù),一套針對(duì)EMI抑制性能,另一套面向PLL性能。

圖5:GP SSCG緩沖器芯片中的頻率調(diào)整。

當(dāng)實(shí)際配置和這些理想設(shè)置有偏差時(shí),各種副作用就會(huì)產(chǎn)生。比如,如果輸入頻率不在所選范圍的正中,VCO和調(diào)制頻率就會(huì)被直線調(diào)整(下圖6)。

如果PLL帶寬太低(一般是由于控制周期間抖動(dòng),如圖6所示),那么頻率概圖就會(huì)變形,從而影響EMI性能。

當(dāng)輸入頻率最低時(shí),結(jié)果是最糟糕的:因?yàn)镻DF和VCO頻率都很低,周期間抖動(dòng)大大增加,并且由于調(diào)制頻率低而頻率概圖可能變形,EMI抑制性能就會(huì)大大降低。

圖6:頻率調(diào)整和理想概圖比較。

當(dāng)擴(kuò)展量的選擇受到限制時(shí),開發(fā)人員就必須選擇一個(gè)超出需要的更大擴(kuò)展量。這常常會(huì)增加周期間抖動(dòng),并降低系統(tǒng)時(shí)序預(yù)算。

如果沒(méi)有一個(gè)擴(kuò)展率可以滿足系統(tǒng)要求,開發(fā)人員就必須要求時(shí)鐘供應(yīng)商對(duì)設(shè)計(jì)作出改動(dòng)并提供一款新的芯片,而這個(gè)過(guò)程中,哪怕僅僅是改變一個(gè)金屬層那么簡(jiǎn)單,也最少需要數(shù)周的時(shí)間,并且成本一般都非常高。

與之相比,一個(gè)可編程的展頻時(shí)鐘生成器則能夠提供支持可現(xiàn)場(chǎng)編程性的通用時(shí)鐘,并結(jié)合片上非易失性存儲(chǔ)器,實(shí)現(xiàn)動(dòng)態(tài)的展頻參數(shù)重置,從而不需要讓廠家花大量時(shí)間和成本對(duì)芯片進(jìn)行改動(dòng)。

可編程性還讓展頻時(shí)鐘性能能夠針對(duì)所要求的規(guī)格進(jìn)行優(yōu)化。比如,開發(fā)人員可以規(guī)定2.1%的精確擴(kuò)展率(而不是固定選擇的3%),或者為實(shí)現(xiàn)所需的頻率設(shè)置而優(yōu)化調(diào)制模式。

上面的圖4展示了如何利用一個(gè)帶有2個(gè)展頻PLL的4PLL型時(shí)鐘芯片,通過(guò)調(diào)制頻率優(yōu)化來(lái)輕松將EMI降低3 ~4 dB的。這些擴(kuò)展的PLL都有兩個(gè)獨(dú)立擴(kuò)展模式可供選擇。

大部分開發(fā)人員都更喜歡使用Hershey Kiss展頻時(shí)鐘來(lái)實(shí)現(xiàn)更好的EMI抑制性能,但很多時(shí)鐘供應(yīng)商都只提供線性展頻時(shí)鐘。在理想情況下,一個(gè)SSCG必須同時(shí)提供Hershey Kiss和線性展頻時(shí)鐘。圖3展示出Hershey Kiss展頻時(shí)鐘在上面所示的4PLL時(shí)鐘芯片測(cè)試條件下一次性EMI降低了1.67dB。

另外,重要的時(shí)鐘參數(shù),例如PLL電荷泵電流、VCO增益和輸出驅(qū)動(dòng)強(qiáng)度,都是必須能夠編程設(shè)置的。這樣的靈活性能夠大大提高系統(tǒng)性能,減少系統(tǒng)開發(fā)時(shí)間,將改動(dòng)限制到最小并降低風(fēng)險(xiǎn)。