0 引 言

VDMOS與雙極晶體管相比,它的開關速度快,開關損耗小,輸入電阻高,驅動電流小,頻率特性好,跨導高度線性等優(yōu)點。特別值得指出的是,它具有負溫度系數,沒有雙極功率管的二次擊穿問題,安全工作區(qū)大。因此,不論是開關應用還是線性應用,VDMOS都是理想的功率器件。VDMOS的開關速度是在高頻應用時的一個重要的參數,因此提出一種減小寄生電容的新型VDMOS結構。

1 基本原理

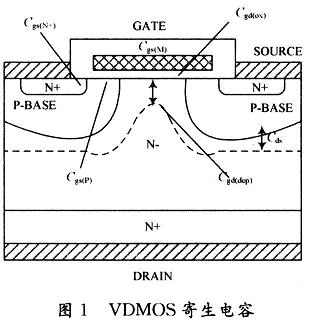

功率VDMOS的開關特性是由其本征電容和寄生電容來決定的。VDMOS的電容主要由三個部分柵源電容Cgs柵漏電容Cgd以及源漏電容Cds組成,如圖1所示。電容的充放電是限制其開關速度的主要因素。柵源之間的電容是由三個部分組成,即:

Cgs=Cgs(N+)+Cgs(P)+Cgs(M)

Cgs(N+)是柵源交疊電容;Cgs(M)是柵與源金屬間的電容;Cgs(P)是柵與P-base之間的電容。這三個電容的大小都是由VDMOS本身設計上的參數決定的,最主要取決于介質層的厚度。

柵漏之間的電容Cgd是兩個電容的串聯(lián):

![]()

當柵壓未達到閾值電壓時,漂移區(qū)與P-base形成的耗盡層結合在一起,形成面積很大的耗盡層電容,柵下漂移區(qū)空間電荷耗盡區(qū)電容Cgd(dep)只是其中一部分,此時耗盡層寬度最大,耗盡電容最小。當柵壓達到閾值電壓后,器件開啟時,漏區(qū)電勢降低,耗盡層寬度減小,Cgd(dep)迅速增大。

漏源之間的電容Cds是一個PN結電容,它的大小是由器件在源漏之間所加的電壓VDS所決定的。

一般VDMOS都包含了Cgs,Cgd和Cds,但是功率VDMOS都不是采用這三個電容作參考,而是采用Ciss,Coss和Crss作為評估VDMOS器件的電容性能,Ciss,Coss和Crss參數分別定義為:輸入電容:Ciss=Cgs+Cgd輸出電容:Coss=Cds+Cgd;反饋電容:Crss=Cgd。實際中采用Ciss,Coss和Crss作為衡量VDMOS器件頻率特性的參數,它們并不是定值,而是隨著其外部施加給器件本身的電壓變化的。

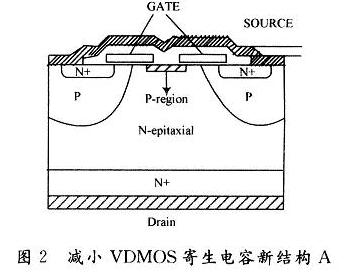

VDMOS的開啟延遲時間td(on)、上升時間tr、關斷延遲時間td(off)、下降時間tf的關系式可分別表達為:

式中:Rg為開關測試電路中器件外接柵電阻;Vth為閾值電壓;Vgs是外加柵源電壓;vgs是使器件漏源電壓下降到外加值10%時的柵源電壓;Ciss*是器件的輸入電容;在td(on)和td(off)式中:Ciss*=Cgs+Cgd;在tr和tf式中:Ciss*=Cgs+(1+k)Cgd(考慮密勒效應)。由上述關系式可見,Cgd直接影響器件的輸入電容和開關時間,Cgd通過密勒效應使輸入電容增大,從而使器件上升時間tr和下降tf時間變大,因此減小柵漏電容Cgd尤為重要。

2 新結構的提出

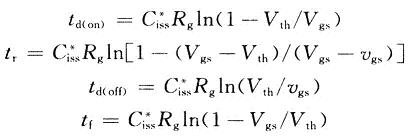

根據上面對VDMOS電容的分析,提出一種新的結構以減少器件的寄生電容。由分析可得出,柵下耗盡層的形狀對VDMOS電容有較大影響,最主要影響Cgd。

圖2中給出了新的VDMOS單元A,在VDMOSneck區(qū)域斷開多晶硅條,同時在斷開處注入一定的P型區(qū),改變VDMOS柵下耗盡區(qū)的形狀。這種新結構,在一定程度上加大耗盡區(qū)的寬度,從而減小Cgd。如圖2結構中Pody下P-區(qū)注入區(qū)域為neck區(qū)中間3μm,注入能量是40 keV,注入劑量是1e13—3 cm,傳統(tǒng)結構多晶硅柵完全覆蓋P-body島間漂移區(qū),正是由多晶硅柵和漂移區(qū)的交疊形成的柵漏電容在充電時需大量電荷,導致器件開關損耗很大,新結構將多晶柵和漂移區(qū)的交疊部分移除,可以大大降低柵電荷,提高器件的動態(tài)性能。

3 新結構的模擬結果

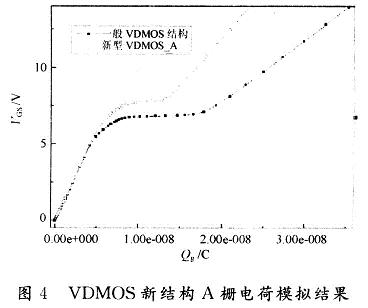

圖3給出了新型結構A的寄生電容模擬結果,從模擬結果來看,新型結構A增大了柵下耗盡區(qū)寬度,改變了柵下耗盡區(qū)的形狀,減小了柵漏電容Cgd對輸入電容、輸出電容沒有較大影響,在一定程度上減小了反饋電容。

柵電荷是比輸入電容更有用的參數,從電路設計的角度,由Qg=Igt可得到使器件在理想開啟時間內所需的柵電流值。柵電荷Qg是功率MOSFET兩個最重要的參數之一(另一參數為Ron)。使用非零的Vds提供Qg-Vgs曲線已經成為一種工業(yè)標準。在曲線里包含五種信息:共源輸入電容Ciss;共源反向傳輸電容Crss;使器件開啟必須加在柵上的電荷量;得到器件理想開關速度所需的柵電荷;器件在開關期間所損耗的能量。

電源電路設計工程師使用這些信息設計驅動電路,并估汁器件性能。采用TCAD(ISE)對新型結構A進行了模擬,模擬結果如圖4所示。

可以明顯看出新型結構A的柵電荷明顯比一般結構的柵電荷小很多,Qg定義為Vgs=12 V時柵上所存貯的電荷,新型結構A和一般VDMOS結構柵電荷分別為20.25 nC和30.57 nC,減小了33.67%。

4 結 語

本文提出一種減小VDMOS寄生電容,提高其動態(tài)特性的新結構。并用TCAD(ISE)軟件對其模擬。從模擬分析結果可看出,新型結構A與傳統(tǒng)VDMOS相比,能有效減小反饋電容及柵電荷,提高VDMOS器件的開關速度,提高器件的動態(tài)性能。