1 引言

功率金屬- 氧化物- 半導體場效應晶體管(MOSFET)、絕緣柵雙極晶體管(IGBT)、智能功率模塊(IPM)被譽為新型電力電子器件的代表,廣泛應用于工業(yè)控制、電力機車、家用電器、綠色照明、計算機、汽車電子等諸多領(lǐng)域。目前,我國功率MOSFET 產(chǎn)業(yè)已經(jīng)初步形成,產(chǎn)品主要集中在60V~600V 中小電流范圍,對于200V/100A以上的中高壓大電流器件,尚未見到國產(chǎn)的成熟產(chǎn)品。這類器件主要應用于大功率DC-DC 換流器、同步整流、開關(guān)模式或諧振模式電源、DC 斬波器、電池充電等領(lǐng)域。基于揚州國宇電子有限公司5 英寸功率MOSFET 技術(shù),本文提出了一種200V/100A VDMOS器件元胞結(jié)構(gòu),然后重點闡述了包括光刻、刻蝕、擴散等在內(nèi)的關(guān)鍵制造工藝,最后對測試結(jié)果進行了分析。

2 器件結(jié)構(gòu)

按照導電溝道相對于硅片表面的方向不同,功率MOSF ET 通常分為平面型VDMOS 和溝槽型TrenchMOS,二者均通過兩次擴散在柵氧一側(cè)形成長度不同的摻雜區(qū)域來構(gòu)造導電溝道。由于溝槽刻蝕使得柵氧形成于縱向,極大地提高了硅片表面利用率,并消除了JFET 區(qū),因而TrenchMOS器件橫向尺寸得以顯著減小,每平方厘米可達數(shù)千萬個元胞,其精細程度已進入深亞微米范疇。不過,由于溝槽底部拐點區(qū)域固有的電場集中效應,TrenchMOS 主要應用于數(shù)十伏的低壓領(lǐng)域,在150V~600V 的中高壓范圍內(nèi),平面型VDMOS 仍是主流。此外,平面型VDMOS 還具有工藝相對簡單、成品率高的特點。

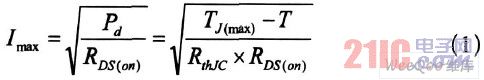

正向?qū)顟B(tài)下,功率MOSFET 最大額定電流主要受限于功率耗散,即:

其中Pd 為功率耗散,RDS(on)為導通電阻,TJ(max)、T 分別為器件允許的最高工作溫度和實際工作溫度,RthJC 為器件熱阻,與封裝有關(guān)。可見,導通電阻是最大額定電流的決定性因素之一,在器件綜合性能允許的情況下,最大程度地降低導通電阻是器件設計的關(guān)鍵環(huán)節(jié),也是功率MOSFET 自上世紀八十年代出現(xiàn)以來,工程師們持之以恒的追求。2009年8月,美國Fairchild 公司開發(fā)出世界上首只導通電阻小于1m Ω的功率MOSFET,最大額定電壓/ 電流為30V/60A,主要得益于高密度溝槽柵技術(shù)的采用使得單位面積內(nèi)有更多元胞并聯(lián),增大了溝道總有效寬度,從而顯著地減小了以溝道電阻為主的導通電阻。

對于中高壓平面型VDMOS 器件來說,增加元胞數(shù)量以減小導通電阻也是有效的方式,一方面可以減小漂移區(qū)電阻和JFET 區(qū)電阻,另一方面也增大了總的溝道有效寬度,盡管溝道電阻可能不再是主要矛盾。不過,元胞數(shù)量的增加必然增大器件面積,最終受限于由柵電容決定的開關(guān)損耗, 因此,VDMOS 器件設計需要折衷考慮導通電阻和開關(guān)損耗,對外延層厚度、摻雜濃度、元胞結(jié)構(gòu)、柵氧厚度、面積等參數(shù)進行優(yōu)化。對于一定的阻斷電壓,采用增大元胞內(nèi)溝道寬度以減小溝道電阻、增大多晶覆蓋下的非溝道區(qū)域柵氧厚度以減小柵電容是減小器件功率耗散的有效途徑。

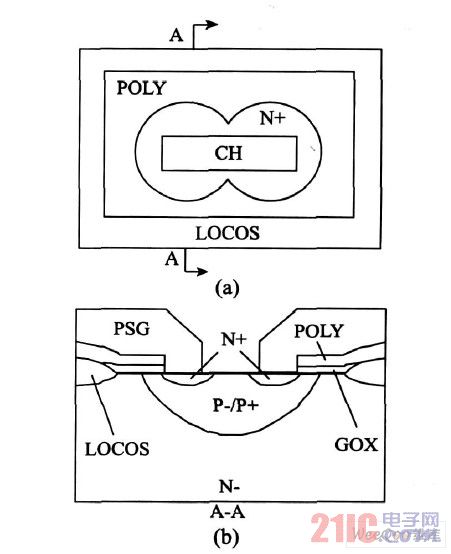

設計的器件元胞結(jié)構(gòu)如圖1 所示,圖1(a)為元胞俯視圖,圖1(b)為A-A 處剖面示意圖,其中LOCOS 為局域氧化區(qū),POLY 為多晶硅覆蓋區(qū),CH為歐姆接觸孔,GOX為柵氧,PSG為磷硅玻璃,N+、N-、P- 分別為N型高摻雜區(qū)、N 型低摻雜區(qū)、P 型低摻雜區(qū)。圖1(a)中多晶覆蓋區(qū)邊緣呈圓弧形,其溝道呈放射狀分布,具有比直線型排列溝道更大的寬度。

圖1 200V/100A VDMOS 器件元胞結(jié)構(gòu)示意圖

3 工藝流水

根據(jù)揚州國宇電子有限公司現(xiàn)有多晶硅柵自對準工藝,制定了如下工藝流程:

備片→薄氧氧化→ SiN 淀積→一次光刻→刻蝕→場氧化→ SiN 剝離→柵氧氧化→多晶硅淀積→ 多晶硅摻雜→二次光刻→多晶硅刻蝕→中劑量硼(P-)注入→三次光刻→大劑量硼(P+)注入→ P 阱推進→四次光刻→大劑量磷(N+)注入→PSG淀積→PSG致密→五次光刻→接觸孔刻蝕→金屬化→ 六次光刻→金屬刻蝕→合金→鈍化介質(zhì)淀積→七次光刻→刻蝕→原片減薄→背面金屬化→測試上述流程中,柵氧化、第三、四、五次光刻與第二次光刻套準、多晶硅刻蝕、P 阱推進等為關(guān)鍵工藝,需要重點監(jiān)控,其余工藝均相對成熟。

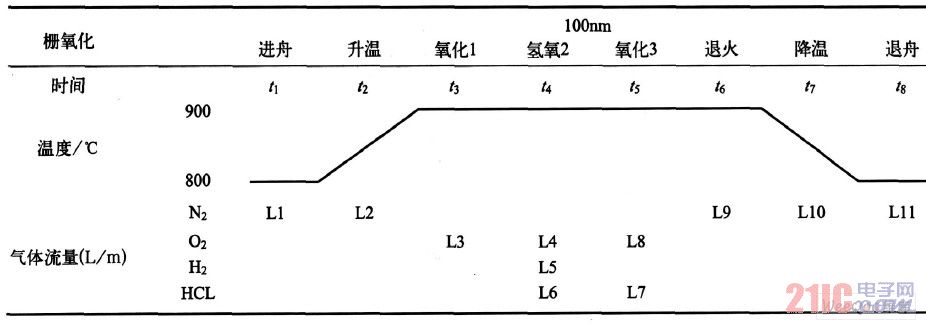

表1 柵氧化工藝條件

3.1 柵氧化

質(zhì)量較好的柵氧,其擊穿特性為本征擊穿,通常厚度為10nm的氧化層其擊穿電壓需達到8V以上。

除了熱氧化工藝本身外,氧化前處理也是重要環(huán)節(jié)。

此處采用SC3 液和HF溶液處理,完成后沖水、甩干,入擴散爐管進行熱氧化,加工條件如表1 所示。氧化完成后,用膜厚儀測試得到膜厚平均值為100 ±3nm,均勻性良好。

3.2 光刻套準

平面型VDMOS N+ 源區(qū)、P+ 注入?yún)^(qū)、歐姆接觸孔等位置在元胞內(nèi)通常呈中心對稱,如圖1 所示,這是器件電學特性一致性和可靠性的要求。由于自對準工藝采用多晶硅刻蝕后的圖形作為P- 注入掩蔽,其后的N+ 注入掩蔽需要位于多晶硅刻蝕窗口的中心位置,P+ 注入光刻和歐姆接觸孔光刻后形成的窗口也需要位于該區(qū)域中心。上述要求除了版圖設計時的精確度量以外,加工過程中的實際套準也至關(guān)重要。通常采用數(shù)套游標圖形以監(jiān)控光刻工藝中的套準,本次設計采用第三、四、五圖層游標對套第二層游標的方法,光刻顯影后的實際套準狀況如圖2所示。可見第四次光刻(NLS)與第二次光刻(PLY)套準良好,X 和Y 方向的誤差不超過0.1 μm。第三層與第五層也有類似結(jié)果,此處不再一一列出。

圖2 NLS 光刻與PLY光刻套準游標

3.3 多晶硅刻蝕

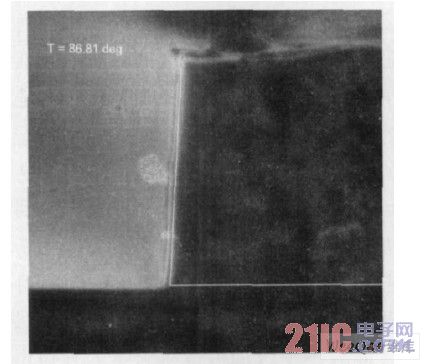

多晶硅柵自對準工藝要求作為P- 注入掩蔽的多晶硅覆蓋區(qū)邊緣光滑、側(cè)壁陡直,因此通常采用干法刻蝕工藝形成多晶硅刻蝕窗口,其中刻蝕氣氛、射頻功率、真空度等條件對刻蝕速率、均勻性、各項異性效果影響很大。采用HITACHI M-206 II 設備,首先以一定比例SF6 和CHF3 混合氣體去除多晶硅表面氧化層,然后用Cl2 和HBr 混合氣體刻蝕多晶硅及部分柵氧層。由圖3 可見,采用上述條件刻蝕多晶硅,可以得到接近87°的側(cè)壁角度,表面光滑齊整;尤其重要的是,刻蝕完成后的剩余柵氧厚度較為均勻,控制在500 ± 50 μm 的范圍,有利于后續(xù)P- 和N+ 注入的均勻性。

圖3 干法刻蝕多晶硅圖片

3.4 P阱推進

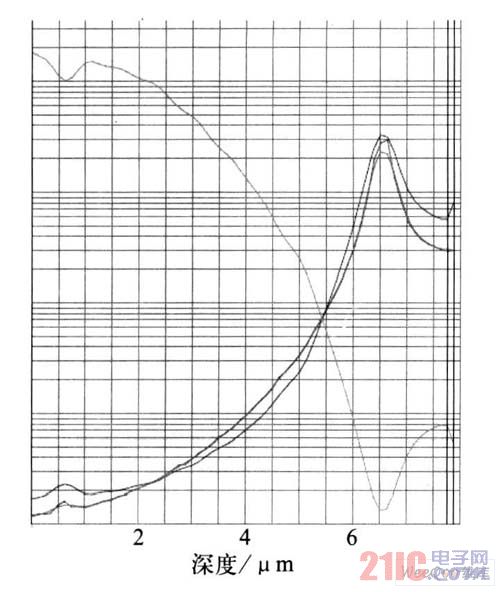

導電溝道形成于P 阱表面,該處雜質(zhì)分布是決定器件閾值電壓的關(guān)鍵參數(shù)之一,而且,P 阱深度及雜質(zhì)擴散輪廓與元胞和場限環(huán)擊穿電壓密切相關(guān),也是器件抗雪崩擊穿能力的決定性參數(shù)。盡管設計良好的器件對于P 阱推結(jié)工藝有一定容差,此工序仍應重點監(jiān)控。采用1150℃,純N2條件下推進330min,得到的結(jié)深約6.5 μ m,擴展電阻法測試結(jié)果如圖4所示。

圖4 P 阱擴展電阻測試曲線

4 測試結(jié)果

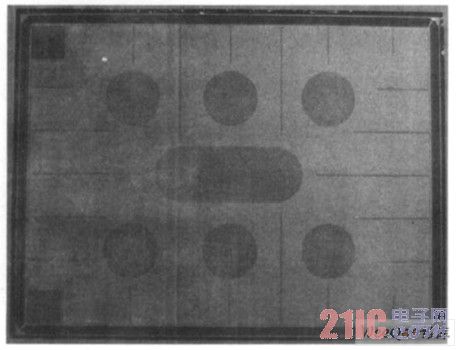

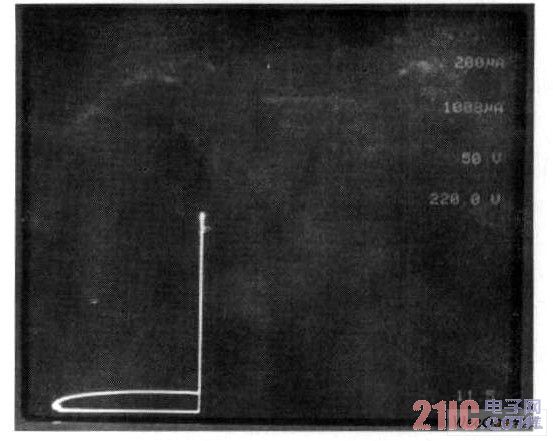

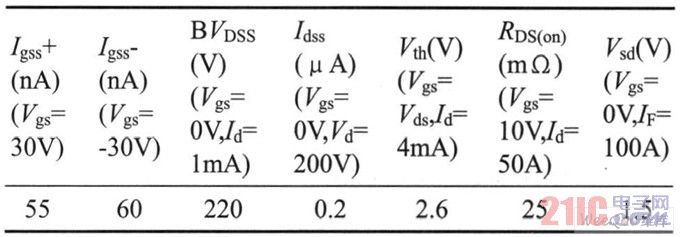

流水所得芯片如圖5 所示,面積14400 μ m ×10800μm,其中左邊兩個角上深色方塊為柵極壓點,中間區(qū)域七個深色圖形為源極壓點。采用JU NODTS1000 系統(tǒng)測試結(jié)果如表2 所示,各參數(shù)良好,其中RDS(on)和Vsd 均為脈沖測試。圖6 為元胞掃描電鏡圖片,其中N 阱、P 阱及多晶硅下的“鳥嘴”清晰可見,后者顯著減小了該區(qū)域柵電容。圖7、圖8 分別為Tektronics 371 晶體管圖示儀測試所得漏源擊穿電壓和柵源耐壓波形,可見器件漏源擊穿特性良好,柵源耐壓大于83V,達到本征擊穿。

圖5 200V/100A芯片照片

圖6 元胞掃描電鏡分析

圖7 漏源擊穿電壓波形

圖8 柵源耐壓波形

表2 200V/100A VDMOS器件參數(shù)測試結(jié)果

5 結(jié)論

本文采用圓弧形分布溝道與局域氧化相結(jié)合的方法開發(fā)出一種200V/100A VDMOS器件,在一定程度上解決了器件導通電阻改善與開關(guān)損耗增大的矛盾。對流水過程中的關(guān)鍵工藝進行了監(jiān)控,所得器件具有較好的綜合性能, 為國產(chǎn)大電流功率MOSFET 器件研發(fā)探索出一條途徑。