引 言

與機(jī)械電位器相比,數(shù)字電位器" title="數(shù)字電位器">數(shù)字電位器有許多優(yōu)點。但是在有些應(yīng)用場合,數(shù)字電位器的分辨率往往達(dá)不到設(shè)計要求,通常最大抽頭數(shù)為1 024。以X9241" title="X9241">X9241為例,內(nèi)部包括一個I2C接口和4個64抽頭的數(shù)字電位器,可獨立使用,也可串聯(lián)使用,如按常規(guī)方法使用,其分辨率較低,即使4個電位器串聯(lián),也只能達(dá)到256個抽頭。本文提出了一種軟件、硬件結(jié)合的方法,可使電位器的中間抽頭數(shù)達(dá)到8 001個,分辨率達(dá)到O.008%。

1 設(shè)計原理

1.1 基本原理

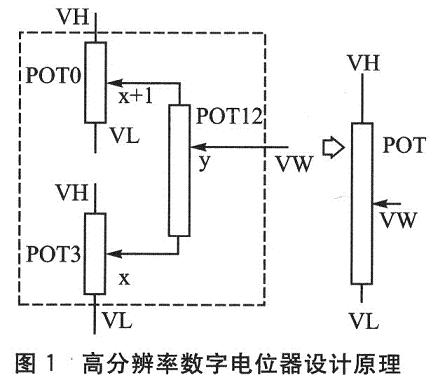

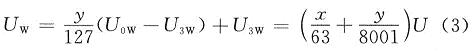

高分辨率" title="高分辨率">高分辨率數(shù)字電位器POT由4個電位器組成,如圖1所示,4個數(shù)字電位器POT0、POT1、POT2、POT3均為64抽頭數(shù)字電位器。POTO、 POT3的固定端并聯(lián),滑動端分別接POT12的固定端。POT12由POT1、POT2串聯(lián),組成一個127抽頭的電位器。4個獨立電位器阻值相等,可根據(jù)需要選取。高分辨率數(shù)字電位器的固定端為VH、VL,滑動端為VW,VW由POT1、POT2的2個滑動端并連。

假設(shè)POT0、POT1、POT2、POT3、POT12的滑動端位置分別為x0、x1、x2、x3、y,POT的滑動端位置為z。

現(xiàn)采取以下控制策略:

①若POT3的滑動端位置為x,則POTO的滑動端位置同步調(diào)節(jié)到x+1,即兩電位器始終保持1的間隔,相當(dāng)于粗調(diào)節(jié);

②調(diào)節(jié)POTl2滑動端位置y,相當(dāng)于把間隔為1的區(qū)間再細(xì)分若干等分,即細(xì)調(diào)節(jié)。

采用等校電路法,可得到z與x、y的關(guān)系。

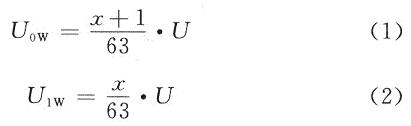

設(shè)VL、VH端電位分別為0、U,滑動端電位為UW,根據(jù)電學(xué)公式可得:

其中,U0W、U1W分別為POT1、POT1滑動端輸出電位,并加到POT12的兩個固定端。

由式(1)、式(2)推出式(3),得VW端輸出電位。

即電位器POT的滑動端相對于VL的電阻阻值為:

若規(guī)定z的步進(jìn)增量為1,則有:

![]()

其中,R為電位器固定端的阻值,x的取值范圍為0~62,y的取值范圍為0~127。z的取值范圍為0~8 001。分辨率為O.008%,中間抽頭數(shù)為8 001個。

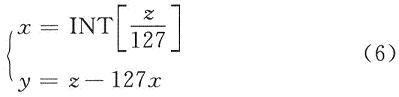

因為x、y、z均為整數(shù),所以有:

即x為z/127的取整,y為z/127的取余。

1.2 控制算法

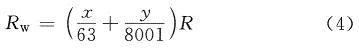

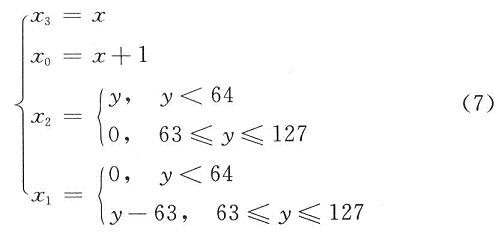

式(5)、(6)即為實現(xiàn)高分辨率數(shù)字電位器的基本公式。為了軟件設(shè)計,還必須建立POT的中間抽頭位置z與POT0、POT1、POT2、POT3的中間抽頭位置的關(guān)系。

根據(jù)圖1可知:

2 硬件電路

2.1 X9241數(shù)字電位器

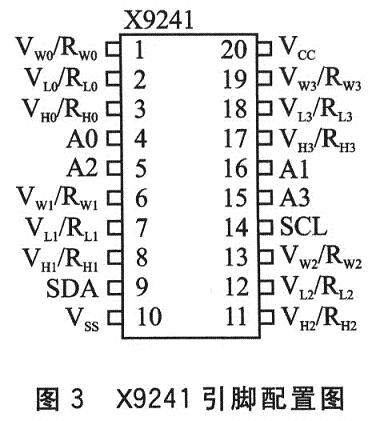

X9241是Xicor公司生產(chǎn)的數(shù)字電位器,內(nèi)部包括1個I2C接口和4個64位數(shù)字電位器POTO、POT1、POT2、POT3。每個數(shù)字電位器由電阻陣列及與之對應(yīng)的滑動端計數(shù)寄存器WCR、4個位數(shù)據(jù)寄存器R0~R3等部分構(gòu)成。其引腳配置如圖3所示。

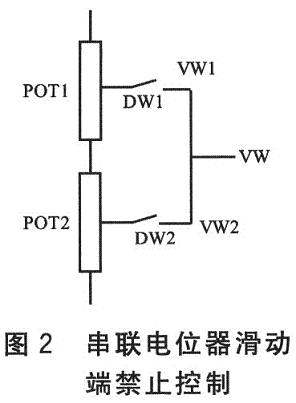

每個電位器由63個電阻段組成,每個電阻陣列的物理終端等效于機(jī)械電位器的固定端(VH、VL)。每個陣列的VH和VL以及每個電阻段之間的接點(即抽頭)通過FET開關(guān)連接滑動輸出端,而滑動端在電阻陣列中的位置由從WCR控制。其中,VW、VW1、VW2、VW3分別為4個電位器的滑動端,VL0、 VL1、VL2、VL3分別為4個電位器的低端、VH0、VH1、VH2、VH3分別為4個電位器的高端。如果將4個電阻陣列中的2個、3個或4個串聯(lián),可構(gòu)成127、190或253抽頭的數(shù)字電位器。芯片采用I2C總線接口,SDA、SCL分別為串行數(shù)據(jù)和串行時鐘。A0~A3為芯片地址設(shè)置位。

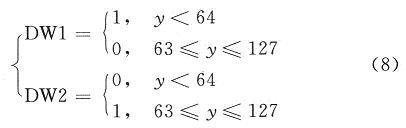

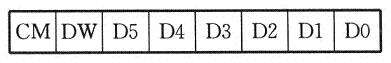

X9241提供了把陣列串聯(lián)起來的方法,可以把1個陣列的63個電阻元件與1個相鄰陣列的電阻元件串聯(lián)起來。其控制位在3字節(jié)的指令中,其數(shù)據(jù)字節(jié)包括用來定義滑動端位置的6位(LSB)加上高2位:CM(串聯(lián)方式)和DW(禁止滑動端)。數(shù)據(jù)字節(jié)如下所示:

2.2 電路設(shè)計

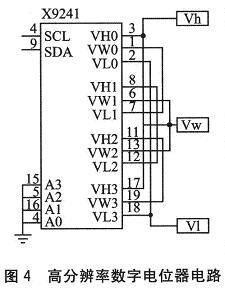

根據(jù)圖1的設(shè)計原理和圖3的引腳配置圖,可實現(xiàn)高分辨率數(shù)字電位器的電路設(shè)計,如圖4所示。

①SDA、SCL是I2C總線的串行數(shù)據(jù)和串行時鐘,與單片機(jī)的I/O線相連,單片機(jī)是主器件,X9241是從器件,器件地址為:

0 1 0 1 A3 A2 A1 A0

高4位固定,低4位由A3~A0的接線方式所決定,按照圖4電路的接線方式,X9241的從地址為50H。

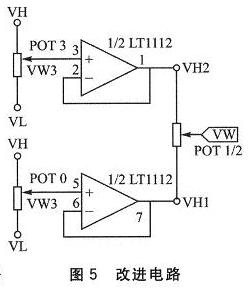

②為了提高線性度,可在VW0與VL1之間加入1級運算放大器組成的跟隨器,VW3與VH2之間也加入1級。其改進(jìn)電路如圖5所示。

3 程序設(shè)計

3.1 讀寫單個數(shù)字電位器函數(shù)設(shè)計

根據(jù)X9241的指令結(jié)構(gòu)和控制時序,可以編寫讀寫單個數(shù)字電位器的程序。

(1)改變電位器中間抽頭命令(寫WCR)時序以寫電位器POT0為例,把電位器0的中間抽頭WCR設(shè)置為20H(X9241每個電位器的最大抽頭數(shù)是 64,即有效值小于63)。命令控制字為101000000B,即AOH;若在電路中AOA1A2A3均接低電平,則器件地址為01010000B,即 50H。其命令序列如下:

Start→發(fā)送地址50H→Ack→發(fā)送命令字A0H→ACK→發(fā)送20H→ACK→Stop。

(2)讀電位器中間抽頭位置命令(讀WCR)時序以讀電位器POT1為例,把電位器1的中間抽頭WCR位置值讀回。命令控制字為100100000B,即90H;若在電路中AOA1A2A3均接低電平,則器件地址為01010000B,即50H。其命令序列如下:

Start→發(fā)送地址50H→Ack→發(fā)送命令字90H→ACK→接收1個字節(jié)→ACK→Stop。

3.2 主函數(shù)設(shè)計

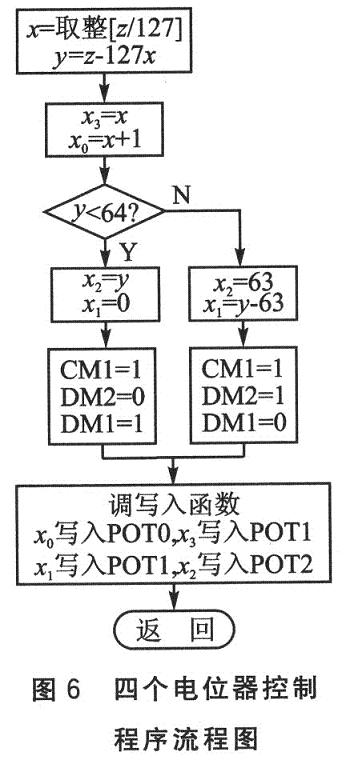

本函數(shù)的功能是把設(shè)計的數(shù)字電位器POT的中間抽頭位置z轉(zhuǎn)換為4個獨立數(shù)字電位器POT0~POT3的中間抽頭位置寄存器WCR的值x0~x3,同時控制POT1、POT2的控制位CM和DW,如圖6所示。

在流程圖中,當(dāng)y<64時,POT12(由POT1和POT2串聯(lián))的中間抽頭位置在POT2范圍內(nèi),所以POT1的中間抽頭失效,即置DM1=1;當(dāng)y≥64時,POT12的中間抽頭位置在POT1范圍內(nèi),所以POT2的中間抽頭失效,即置DM2=1。

結(jié) 語

采用軟硬件協(xié)同的方法,能以較低的成本實現(xiàn)高分辯率數(shù)字電位器的設(shè)計。同一芯片中4個數(shù)字電位器的良好匹配和電壓跟隨器的應(yīng)用,使設(shè)計的數(shù)字電位器具有更好的線性度。在實際應(yīng)用中,為了提高帶負(fù)載能力,需要在滑動輸出端接一輸出緩沖器。