半導(dǎo)體行業(yè)從一開始就以“更小、更快、更便宜、更好”為宗旨。當(dāng)前的掌上電腦(Pocket PC)比占地整整一幢樓的第一臺(tái)電腦功能更強(qiáng)大。然而,到目前為止,實(shí)現(xiàn)這一目標(biāo)的方法都是減小組成半導(dǎo)體器件的單個(gè)晶體管的體積。這也帶來了有趣的副作用。隨著晶體管變得越來越小,工作電壓也越來越低。在過去的嵌入式系統(tǒng)中應(yīng)用最普遍的就是5V電源。但典型嵌入式系統(tǒng)中的大多數(shù)元器件也轉(zhuǎn)而采用更低的電源電壓,以充分利用行業(yè)最新趨勢(shì)帶來的好處。另一方面,系統(tǒng)中的某些元器件需要更長(zhǎng)的時(shí)間才能完成轉(zhuǎn)變。因此,在轉(zhuǎn)變過程中,系統(tǒng)中的某些元器件可能需要不同的供電電壓(如,在3.3V系統(tǒng)中存在5V器件,反之亦然)。這給嵌入式設(shè)計(jì)人員帶來了一些設(shè)計(jì)方面的挑戰(zhàn)。一種解決方案是采用邏輯電平轉(zhuǎn)換器,但采用電平轉(zhuǎn)換器并非成本效益最高的解決方案。本文將討論3.3V單片機(jī)(MCU)與5V外設(shè)接口的一些低成本設(shè)計(jì)思路。

如果要將5V設(shè)計(jì)轉(zhuǎn)為3.3V,第一件事就是尋求電源為3.3V但其他性能相同的單片機(jī)。大多數(shù)情況下,都能找到支持3.3V電壓的同等器件。而且,基本上,3.3V器件的成本與之持平,甚至更低。如果找不到可運(yùn)行在3.3V條件下的替代器件,那么就必須采用雙電源了。本文的重點(diǎn)就是討論采用雙電源供電的設(shè)計(jì)。

對(duì)于5V和3V器件共存的設(shè)計(jì),首先必須理解邏輯電平和輸入/輸出結(jié)構(gòu)。對(duì)于輸入,需要考慮VIH(保證被檢測(cè)為高輸入的電壓)和VIL(保證被檢測(cè)為低輸入的電壓)。將3.3V系統(tǒng)連接到5V器件時(shí),VIH 通常會(huì)比VIL帶來更大的問題。當(dāng)然,這并不是說可以忽略VIL 參數(shù)。驅(qū)動(dòng)器件必須輸出高于接收器件VIH(min)值的電壓才能保證正確的邏輯檢測(cè)。但是,如果電壓太高也不好。

幾乎所有CMOS器件在所有I/O引腳都采用了某種形式的ESD保護(hù)。實(shí)現(xiàn)ESD保護(hù)最常見的方法是采用箝位二極管將這些引腳連接到Vdd 和 Vss。這通常意味著最大輸入電壓為Vdd +0.3V,最小輸入電壓為Vss - 0.3V。如果電壓超出這一范圍,保護(hù)二極管就會(huì)導(dǎo)通。如果輸入端沒有串聯(lián)電阻,就會(huì)導(dǎo)致這些二極管通過極大電流,并有可能造成器件鎖死。這肯定不是所希望發(fā)生的。如果電壓足夠高(如3.3V系統(tǒng)中的5V輸入),那么串聯(lián)電阻必須非常大才能保證箝位電流處于安全范圍內(nèi)。如果電阻足夠大,那么由于引腳電容和PCB布線而引起的低輸入容抗可能就會(huì)變得重要起來。RC時(shí)間常數(shù)會(huì)導(dǎo)致信號(hào)延遲。許多生產(chǎn)商都建議不要使用箝位二極管實(shí)現(xiàn)ESD保護(hù)。因此,采用串聯(lián)電阻并非將5V信號(hào)饋送到3.3V器件的最好方法。

讓我們看一下標(biāo)準(zhǔn)CMOS器件的邏輯電平,大多數(shù)器件的VIH (min)都是0.7 Vdd或 0.8 Vdd。而 VIL(max) 大致在0.2 Vdd或0.3 Vdd。對(duì)于5V邏輯,對(duì)應(yīng)的VIH 為 3.5V或4.0V,VIL(max) 為1.0V或1.5V。在低負(fù)載時(shí),大多數(shù)CMOS器件的輸出都接近于電源電壓(0.1 或 0.2V)。隨著負(fù)載電流增加,VOH 會(huì)變低。此時(shí),確定VOH必須要考慮負(fù)載電流。

與串聯(lián)輸入電阻相比,更好的方法是采用電阻分壓器將5V信號(hào)轉(zhuǎn)換到3.3V輸入范圍內(nèi)(見圖2)。電阻值的選擇必須考慮到所有公差。計(jì)算時(shí)可參考下面的公式:

R2/(R1 + R2)×VOH (min)>VIH(min) (輸入電壓為標(biāo)稱值5 V與最大負(fù)公差之和)

R2/(R1 + R2)×VOH (max)

在上述計(jì)算過程中還應(yīng)當(dāng)考慮到電阻值本身的公差。

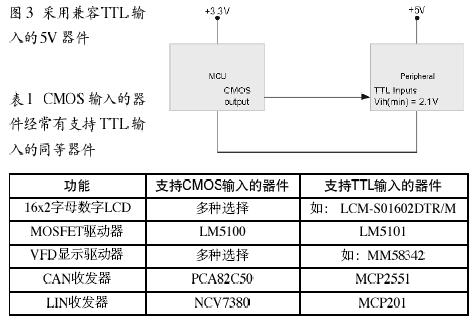

另一種更簡(jiǎn)單的解決方案是采用兼容TTL輸入的5V器件。TTL器件的VIH(min)是2.1V(Vdd為5V時(shí))。在大負(fù)載值條件下,大多數(shù)3.3V器件可以支持更高的VOH電平。此時(shí),解決方案是將外設(shè)器件更換為兼容TTL輸入的同等器件。

應(yīng)該很容易就可以發(fā)現(xiàn)帶有TTL輸入的類似器件。表1給出了一些例子。

如果正在使用必須采用5V供電的標(biāo)準(zhǔn)數(shù)字邏輯系列器件,那么可以尋找支持TTL輸入的同等器件。(如,可使用74HCT 系列代替74HC 系列。)如果需要使用電平轉(zhuǎn)換器,那么可使用“HCT”或“VHCT”型的數(shù)字緩沖器。在大多數(shù)情況下,這一TTL輸入解決方案都比采用專用電平轉(zhuǎn)換器便宜。

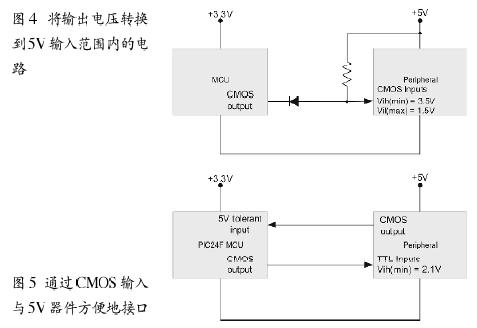

3.3V器件的VOH 電平一般比5V CMOS器件的VIH(0.7Vdd = 3.5V)稍低。一種簡(jiǎn)單的解決方案是使用二極管來實(shí)現(xiàn)電壓轉(zhuǎn)換。

上面的電路將輸出電壓增大了約0.6V。從而正好將3.3V CMOS輸出電壓轉(zhuǎn)換到了5V CMOS輸入范圍內(nèi)。對(duì)于邏輯低電壓信號(hào)也進(jìn)行了同樣大小的轉(zhuǎn)換。但,CMOS輸入的 VIL (max)約為1.5V,因此電壓轉(zhuǎn)換后的信號(hào)仍然滿足 VIL 參數(shù)的要求。對(duì)于這一配置,需要考慮幾件事。當(dāng)3.3V器件輸出0邏輯電平時(shí),電路的汲取電流也將增加。因此應(yīng)當(dāng)仔細(xì)研究一下3.3V器件VOL 規(guī)范對(duì)電路灌電流的限制。通常,灌電流越大,VIL就越高。因此需要小心不要違反VIL參數(shù)要求。如果CMOS 輸出VOL過高,則必須考慮加大上拉電阻值。如果電阻太大,二極管偏置電流會(huì)變低,從而導(dǎo)致二極管的開關(guān)速率降低。

Microchip新推出的16位PIC24系列單片機(jī)提供了可簡(jiǎn)化5V接口的獨(dú)特功能。該系列單片機(jī)的輸入引腳可承受 5V(或 5.5V)電壓,即使器件正常情況下運(yùn)行在3.3V或更低的Vdd電壓下。這些輸入引腳不需要連接到Vdd的箝位二極管,而是采用了不同的ESD保護(hù)機(jī)制。對(duì)于5V接口來說,這是非常重要的特性,因?yàn)檫@樣不需要電阻分壓器就可以直接將5V輸出連接到3.3V器件。讓我們回到圖3的例子,可見添加了這一功能即可實(shí)現(xiàn)無縫的5V接口。

有些單片機(jī)產(chǎn)品還進(jìn)一步增強(qiáng)了這一功能,提供了通過外部5V上拉電阻產(chǎn)生5V輸出的能力。3.3V器件驅(qū)動(dòng)3.3V輸出,但能承受5V的輸入。這些引腳提供數(shù)字控制的漏極開路輸出,使您可以選擇將引腳上拉到5V,而不會(huì)違反任何規(guī)范。這一功能支持通過CMOS輸入與5V器件方便地接口。

當(dāng)采用上拉電阻配置(見圖6)時(shí),需要考慮兩個(gè)器件間的連接電容,從而確定端口引腳處信號(hào)的上升/下降速率(和最大開關(guān)頻率),以及適用的電阻值。考慮下面的公式:

![]()

其中 τ = RC 時(shí)間常數(shù),R×C

PVdd = 外設(shè)電壓Vdd

PVih(min) = 外設(shè)的 Vih(min) 值

如果使用下述典型值:

上拉電阻 R = 1K

電容 C(由于引腳和PCB電容) = 10pF

PVdd = 5V

PVih(min) = 0.7×Vdd = 3.5V

則上升/下降時(shí)間≈12nS

如果可接受的最小上升/下降脈沖的時(shí)間寬度50nS,那么最大的輸出頻率為20MHz。對(duì)于大多數(shù)外設(shè)互連來說,這已經(jīng)足夠了。

這種方法有一個(gè)缺點(diǎn)就是當(dāng)MCU驅(qū)動(dòng)邏輯低電平時(shí),會(huì)通過上拉電阻消耗額外的電流。因此設(shè)計(jì)時(shí)需要考慮速度和電流大小兩個(gè)因素折衷選擇上拉電阻。需要為您的應(yīng)用選擇一個(gè)折衷的電阻值來提供所需的速度并且確保消耗的電流不超出規(guī)范。

有些人可能認(rèn)為不能采用這類配置來驅(qū)動(dòng)低阻抗負(fù)載。如果希望驅(qū)動(dòng)一個(gè)5V的繼電器,那么應(yīng)當(dāng)怎么做?幸運(yùn)的是,對(duì)于驅(qū)動(dòng)繼電器這樣的低阻抗負(fù)載,上述特性也有幫助。從圖7了解電路配置信息。要驅(qū)動(dòng)此類負(fù)載,需要將引腳定義為輸出并驅(qū)動(dòng)為低電平。這里,唯一的限制因素是器件的灌電流能力。要關(guān)斷負(fù)載,將引腳定義為輸入就可以了。關(guān)斷負(fù)載會(huì)將5V電壓直接饋入輸入引腳。由于引腳可以承受5V電壓,因此這一操作是正確的。換句話說,需要保持輸出鎖存器為邏輯低,并通過切換TRIS(輸入/輸出控制寄存器)來使負(fù)載接通/關(guān)斷。

本文介紹了橋接由5V和3.3V供電的電路的有效方法。這些方法完全可以和轉(zhuǎn)換階段橋接由不同電壓供電的電路的低成本智能解決方案媲美。同時(shí),大多數(shù)器件很可能會(huì)很快轉(zhuǎn)向使用更低的電源,從而不再需要進(jìn)行電路橋接。本文給出的方法對(duì)于充分利用半導(dǎo)體行業(yè)的最新發(fā)展趨勢(shì)以及降低系統(tǒng)成本肯定會(huì)有所幫助。