1 引言

近年來,數(shù)字信號處理器(DSP)的應(yīng)用越來越廣泛,其中TMS320F2812作為目前數(shù)字控制領(lǐng)域中性能較高的DSP芯片,被廣泛應(yīng)用于電機(jī)控制、工業(yè)自動化、家用電器和消費(fèi)電子等領(lǐng)域。由于TMS320F2812本身不具有D/A轉(zhuǎn)換模塊,因此在很多需要模擬量輸出的控制場合受到限制。所以D/A轉(zhuǎn)換芯片如何與TMS320F2812進(jìn)行接口,成為數(shù)字信號處理系統(tǒng)需要解決的一個重要問題。這里介紹了四路8位電壓輸出數(shù)字一模擬轉(zhuǎn)換器TLC5620I,并給出TLC5620I與TMS320F2812串口接口的軟、硬件設(shè)計實(shí)現(xiàn)方法。

2 TMS320F2812的SPI工作原理

TMS320F2812的SPI模塊的9個寄存器用來控制SPI的操作,其中SPICCR設(shè)置SPI的軟件復(fù)位、移位時鐘極性字符長度;SPICTL設(shè)置SPI的時鐘相位、工作模式等;SPISTS中包括溢出標(biāo)志位、中斷標(biāo)志位等;SPIBRR設(shè)置SPI波特率;SPIRXBUF和SPITXBUF為數(shù)據(jù)接收和發(fā)送緩沖寄存器,SP-IDAT用于發(fā)送/接收移位寄存器;SPIRXEMU僅用于仿真;SPIPRI控制中斷優(yōu)先級。該器件的SPI接口有一個16級的FIFO,用來減少CPU的開銷。圖1為SPI模塊與CPU接口結(jié)構(gòu)框圖。

由圖1可知,SPI模塊數(shù)據(jù)傳輸由40、41、34、35引腳完成,其引腳功能見表1。

TMS320F2812支持125種不同的波特率和4種不同的時鐘模式。根據(jù)SPI的工作模式(從動或主控),引腳SPICLK可分別接收一個外部的SPI時鐘信號或由片內(nèi)提供SPI時鐘信號。

在該設(shè)計中,SPI工作在主控模式,SPI時鐘由片內(nèi)的SPI產(chǎn)生并由SPICLK引腳輸出。TMS320F2812波特率的設(shè)置是由系統(tǒng)的低速外設(shè)模塊時鐘頻率LSPCLK和SPI主控制器中的SPIBRR寄存器的值決定的,其計算公式如下:

SPI波特率=LSPCLK/(SPIBRR+1)SPIBRR=3~127

SPI波特率=LSPCLK/4 SPIBRR="0"、1、2

引腳SPICLK上的四種不同的時鐘模式是由時鐘極性位和時鐘相位位控制的,其中時鐘極性位選擇時鐘有效沿為上升沿還是下降沿,時鐘相位位則設(shè)定是否選擇時鐘的1/2周期延時。四種不同的時鐘模式如表2所示。

3 TLC5620I簡介

TLC5620I是四路8位電壓輸出數(shù)模轉(zhuǎn)換器(DAC),帶有緩沖基準(zhǔn)輸入端(高阻抗),包含上電復(fù)位功能以確保可重復(fù)啟動,用5 V電源工作。DAC產(chǎn)生范圍在基準(zhǔn)電壓一倍或兩倍與地(GND)之間的輸出電壓,且DAC是單調(diào)變化的。TLC5620I使用4個電阻串(resistor-string)來實(shí)現(xiàn)D/A轉(zhuǎn)換。每個D/A轉(zhuǎn)換的核心是帶有256個抽頭的單電阻,分別對應(yīng)256個可能的代碼。每個電阻串的一端連接到GND端,另一端由基準(zhǔn)輸入緩沖器的輸出饋電。通過使用電阻串保持單調(diào)性。線性度取決于電阻元件的一致性以及輸出緩沖器的性能。由于輸入端是經(jīng)過緩沖的,所以DAC對于基準(zhǔn)源總是呈現(xiàn)為高阻抗負(fù)載。每一個DAC的輸出由可配置增益輸出放大緩沖,它可以配置為一倍或兩倍增益。

通過簡單的3線串行總線可數(shù)字控制TLC5620I,此總線與CMOS兼容且易于與所有常用的微處理器作為控制器器件接口。11位的命令字由8位數(shù)據(jù)(D0~D7),2個DAC選擇位(A0、A1)和1個范圍位(RNG)組成。后者允許在一倍或兩倍輸出范圍之間作選擇。DAC寄存器是雙緩沖的,允許完整的新數(shù)值組寫入器件,然后DAC輸出通過LDAC端的控制同時更新。每個通道輸出的電壓V0由下式計算:

V0=REF×(CODE/256)×(1+RNG bit value)

式中,REF為相應(yīng)通道基準(zhǔn)電壓,CODE是從數(shù)據(jù)位(D7~D0)計算出的十進(jìn)制數(shù),RNG是范圍位串行控制字的0或1。

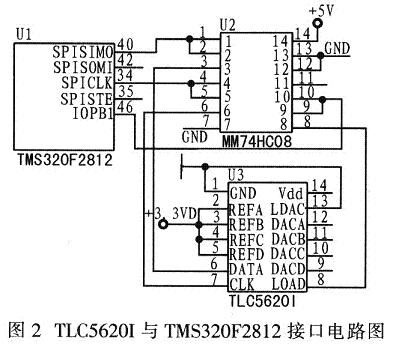

4 TLC5620I和TMS320F2812的接口電路

圖2為TLC5620I和TMS320F2812的接口電路。

該設(shè)計中,引出4路D/A轉(zhuǎn)換通道電壓,均由LM358構(gòu)成電壓跟隨器輸出,如圖3所示。該圖為AD0和AD1口由LM358組成的同向放大電路。AD2和AD3的放大電路與之相同。

TMS320F2812在引腳SPISIMO上將數(shù)據(jù)輸出,與之相對應(yīng)的是TLC5620I的DATA數(shù)據(jù)接收引腳:TMS320F2812的SPICLK引腳和TLC5620I的CLK引腳相對應(yīng),二者共用串行時鐘;TMS320F2812的IOPB1模擬控制TLC5620I的LOAD引腳電平,以鎖存數(shù)據(jù),更新輸出電壓。在數(shù)據(jù)傳輸時,有兩種方式控制TLC5620I輸出電壓的更新:LOAD引腳控制更新和LDAC引腳控制更新。該設(shè)計采用LOAD引腳控制更新方式,此時,LDAC引腳接低電平。開始控制LOAD為高電平,數(shù)據(jù)在CLK引腳的每一個下降沿與時鐘同步從DATA引腳輸入。當(dāng)所有的數(shù)據(jù)傳輸完畢時,控制LDAD引腳跳至低電平,所選擇的D/A通道的輸出電壓得到更新。由于TLC5620I的控制信號要求的VIH較高,所以需要將DSP輸出的SPI-CLK、SPISIMO以及I/O口模擬的CS信號的高電平提高,該設(shè)計采用MM74HC08器件來實(shí)現(xiàn)。

5 軟件設(shè)計

由于TLC5620I的工作頻率是1 MHz,故將DSP的SPI通信頻率也設(shè)置為1 MHz。程序采用C語言模塊化編寫,其流程如圖4所示,圖4a主程序完成系統(tǒng)初始化,中斷使能,等待中斷等工作;圖4b中斷服務(wù)程序主要完成輸出電壓的數(shù)字量計算和數(shù)據(jù)發(fā)送等工作。在編寫程序過程中,要注意TMS320F2812的低速外設(shè)預(yù)分頻和通信頻率間的關(guān)系。

利用該實(shí)驗(yàn)程序,可以通過示波器在DACOUT0和DA-COUT1接口輸出端觀測到三角波,利用萬能表在DACOUT2接口輸出端測得電壓為2.475 V,在DACOUT3接口輸出端測得電壓為1.65 V。

6 結(jié)束語

以TMS320F2812與TLC5620I為例,詳細(xì)討論兩者的串口通信的硬件接口及軟件設(shè)計,實(shí)現(xiàn)數(shù)字信號到模擬信號的轉(zhuǎn)換,擴(kuò)展TMS320TMS320F2812在控制領(lǐng)域的應(yīng)用范圍。在設(shè)計過程中,充分利用TMS320F2812的SPI模塊,只有少量的數(shù)據(jù)線和控制線,使電路設(shè)計簡化,提高了設(shè)計可靠性,并在實(shí)際應(yīng)用中效果良好。