1引言

存儲(chǔ)測(cè)試的特點(diǎn)是集多參數(shù)微型傳感器及信號(hào)調(diào)整、信息采集、信息存儲(chǔ)及傳輸接口電路為一體,對(duì)被測(cè)物體的工作環(huán)境、運(yùn)動(dòng)控制等多通道、大容量參數(shù)進(jìn)行(實(shí)時(shí)、動(dòng)態(tài))數(shù)據(jù)采集、存儲(chǔ)、事后回收、數(shù)據(jù)再現(xiàn)、數(shù)據(jù)分析。目前,存儲(chǔ)測(cè)試技術(shù)已經(jīng)在許多重大武器型號(hào)的研制、生產(chǎn)中得到成功應(yīng)用,并取得了一系列重要科研成果。解決了過(guò)去無(wú)法解決的重大測(cè)試難題,顯示出了突出的優(yōu)越性。

2 硬件設(shè)計(jì)

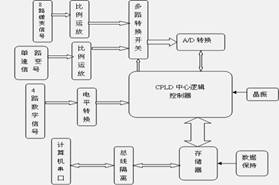

2.1 系統(tǒng)框圖:

本系統(tǒng)中有1路速變模擬信號(hào)、8路緩變模擬信號(hào)、4路數(shù)字信號(hào)。該采集系統(tǒng)能實(shí)現(xiàn)采集0~10V之間的模擬信號(hào),其中單路速變模擬信號(hào)采樣率不低于40Khz,8路緩變模擬信號(hào)采樣率不低于12.5Khz,兩者精度均在0.1%,同時(shí)還能夠存儲(chǔ)4路數(shù)字信號(hào)。信號(hào)記錄時(shí)間均不低于0.75s,整體設(shè)計(jì)如圖1所示。

|

|

|

圖1 采集系統(tǒng)整體框圖 |

2.2信號(hào)調(diào)理設(shè)計(jì)

在本系統(tǒng)中,由于模擬輸入信號(hào)的電壓范圍是0~10V,所以此次設(shè)計(jì)使用LM324運(yùn)算放大器組成的比例電路將輸入信號(hào)變換成0~2.5V電壓。然后輸入模擬開(kāi)關(guān)經(jīng)過(guò)跟隨器后,再輸入A/D轉(zhuǎn)換器。4路數(shù)字信號(hào)使用一個(gè)5V的穩(wěn)壓管,將輸入數(shù)字信號(hào)中大于5V的高電平信號(hào)鉗制在5V,起到了調(diào)壓的作用。如果是低于5V,那么電壓將不改變。

2.3輸入通道設(shè)計(jì)

存儲(chǔ)測(cè)試系統(tǒng)常常需要多通道同時(shí)采集。此次設(shè)計(jì)中根據(jù)被測(cè)信號(hào)的特點(diǎn)選用ADG506模擬開(kāi)關(guān)進(jìn)行各通道的切換,該模擬開(kāi)關(guān)具有開(kāi)關(guān)速度快、泄漏小等特點(diǎn),從而用最簡(jiǎn)單的硬件電路完成多路信號(hào)的存儲(chǔ)測(cè)試。

2.4采集芯片選用:

此次設(shè)計(jì)采用AD公司的AD7492采集芯片,AD7492為12位高速、低功耗、逐次逼近式AD轉(zhuǎn)換器。它可在2.7V-5.25V的供電電壓下工作,采樣頻率最高為1.25MSPS,從而為正確采集回速變、緩變信號(hào)提供保障。

2.5存儲(chǔ)電路設(shè)計(jì)

此系統(tǒng)中,我們共有1路速變模擬信號(hào),8路緩變模擬信號(hào),4路數(shù)字信號(hào)。首先,對(duì)于單路速變信號(hào)而言,其最低采樣頻率為40kHz,系統(tǒng)要求的最低記錄時(shí)間為0.75S此次設(shè)計(jì)中,用了一個(gè)模擬開(kāi)關(guān)和一個(gè)AD7492循環(huán)進(jìn)行數(shù)據(jù)采集,將1路速變信號(hào)和8路緩變信號(hào)交叉安排在ADG506上,這樣在每次速變信號(hào)采集后,緊接著采集8路緩變信號(hào),經(jīng)過(guò)循環(huán)交叉采集后,便使得速變信號(hào)采樣率是緩變信號(hào)采樣率的8倍,所以速變信號(hào)采樣率為8×12.5kHz≥40kHz。其次,對(duì)于8路緩變信號(hào),其單路采樣率為12.5kHz, 記錄時(shí)間為0.75s,共8路。最后,存儲(chǔ)4路數(shù)字信號(hào)。由于我們采用12路的AD采集,所以4路數(shù)字信號(hào)與AD產(chǎn)生的高4位信號(hào)合起來(lái)組成8位一起存入512K的SRAM 628512。因此不再單獨(dú)占用空間。由以上分析我們可以得到存儲(chǔ)容量為:M≥12.5kHz×8路×2×0.75+12.5kHz×8次×2×0.75=300kbyte。為了方便讀數(shù)和數(shù)據(jù)分析,在每組數(shù)據(jù)前加上通道標(biāo)志位,以區(qū)分是哪一路信號(hào)。為了確保存儲(chǔ)空間,此次設(shè)計(jì)我們一共選用兩塊容量為512K的SRAM進(jìn)行數(shù)據(jù)存儲(chǔ)。AD轉(zhuǎn)換和CPLD處理后的采集信號(hào)通過(guò)74LVC4245電平轉(zhuǎn)換后送入SRAM進(jìn)行存儲(chǔ)。

3 CPLD實(shí)現(xiàn)計(jì)算機(jī)異步串行通訊設(shè)計(jì)

3.1異步串行通信的幀格式

在異步串行通信中,數(shù)據(jù)位是以字符為傳送單位,數(shù)據(jù)位的前、后要有起始位、停止位,另外可以在停止位的前面加上一個(gè)比特位(bit)的校驗(yàn)位。其幀格式仍然采用1位開(kāi)始位+8位數(shù)據(jù)位+1位停止位.如圖2所示。此次設(shè)計(jì)中沒(méi)有奇偶效驗(yàn)位。停止位,為邏輯1,總在每一幀的末尾。此次設(shè)計(jì)中停止位為1位。

|

|

|

圖2 串行異步通訊的幀格式 |

3.2異步串行通信的波特率

串行口每秒發(fā)送或接收數(shù)據(jù)的位數(shù)為波特率。若發(fā)送或接收一位數(shù)據(jù)需要時(shí)間為t,則波特率為1/ t,相應(yīng)的發(fā)送或接收時(shí)鐘為1/t Hz。發(fā)送和接收設(shè)備的波特率應(yīng)該設(shè)置成一致,如果兩者的波特率不一致,將會(huì)出現(xiàn)校驗(yàn)錯(cuò)或者幀錯(cuò)。要產(chǎn)生9600b/s波特率,要有一個(gè)不低于9600 Hz的時(shí)鐘才可以。為產(chǎn)生高精度的時(shí)鐘,我們專門(mén)選取48M的晶振,通過(guò)5000分頻,最終頻率為48M/5000=9600BIT/S

3.3發(fā)送程序設(shè)計(jì)

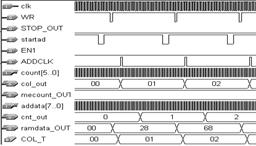

根據(jù)采用的幀格式,需要發(fā)送的數(shù)據(jù)為10位(1位開(kāi)始位、8位數(shù)據(jù)位、1位停止位),在發(fā)送完這10位后,就應(yīng)該停止發(fā)送,并使發(fā)送端電平處于邏輯1,然后等候下次的發(fā)送。發(fā)送電路一共有3個(gè)并行進(jìn)程如圖3所示,進(jìn)程1產(chǎn)生9600bps波特率,使系統(tǒng)能夠以9600的波特率發(fā)送幀。進(jìn)程2中,當(dāng)允許寫(xiě)信號(hào)WR下降延時(shí),發(fā)送完成標(biāo)志位tdEmpty變?yōu)榈碗娖剑_(kāi)始接受并行數(shù)據(jù),并將數(shù)據(jù)放入鎖存器鎖存。當(dāng)寫(xiě)允許WR標(biāo)上升延時(shí),發(fā)送完成標(biāo)志位變?yōu)楦摺_M(jìn)程3,將放入鎖存器中的并行數(shù)據(jù)并串轉(zhuǎn)換,并依照幀格式,將10位數(shù)據(jù),在TXD引腳上以9600波特率,串行輸出經(jīng)過(guò)串口芯片MAX232電平轉(zhuǎn)換后實(shí)現(xiàn)與計(jì)算機(jī)正常通訊。

|

|

|

圖3 發(fā)送模塊時(shí)序圖 |

3.4接收程序設(shè)計(jì)

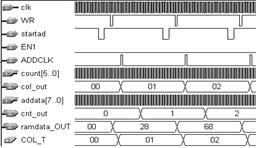

接收電路比發(fā)送電路要復(fù)雜,接收電路要實(shí)時(shí)檢測(cè)起始位的到來(lái),一旦檢測(cè)到起始位到,就要將這一幀數(shù)據(jù)接收下來(lái)。接受電路一共設(shè)計(jì)有三個(gè)并行進(jìn)程如圖4所示,其中進(jìn)程1 負(fù)責(zé)產(chǎn)生9600bps波特率,使系統(tǒng)能夠在9600的波特率與外界系統(tǒng)通訊。進(jìn)程2 產(chǎn)生接收信號(hào)RXD的完成標(biāo)志位,每次在接收到幀的起始位時(shí),標(biāo)志位RXDF變高,在完成接受數(shù)據(jù)后,標(biāo)志位RXDF變低。進(jìn)程3負(fù)責(zé)將RXD信號(hào)輸入的10位串行數(shù)據(jù),依照10位的幀格式,先去掉串口的接收起始位和接收結(jié)束位,取其中的8位有效數(shù)據(jù),并將8位有效數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換,變成并行數(shù)據(jù)后,由8位數(shù)據(jù)總線DATA0~DATA7并行輸出。

|

|

|

圖4 接收模塊時(shí)序圖 |

4采集存儲(chǔ)控制程序設(shè)計(jì)

4.1采樣主控程序設(shè)計(jì):

此次系統(tǒng)我們使用48M晶振,每路信號(hào)采樣率不低于12.5khz,一共相當(dāng)于16路模擬量,所以控制點(diǎn)為48M ÷ (16 12.5khz)=240點(diǎn),所以主控計(jì)數(shù)器中有240個(gè)計(jì)數(shù)點(diǎn)可以用于控制。在0~240個(gè)點(diǎn)中實(shí)現(xiàn)了通道選通、啟動(dòng)AD、幀計(jì)數(shù)、兩次SRAM地址遞推等工作。每次循環(huán)結(jié)束后,系統(tǒng)主控計(jì)數(shù)器清零,反復(fù)循環(huán)采集。具體細(xì)節(jié)如圖5所示。

|

|

|

圖5 控制程序的主控計(jì)數(shù)器及在其各個(gè)計(jì)數(shù)點(diǎn)時(shí)FPGA邏輯控制設(shè)計(jì) |

4.2 各個(gè)模塊的設(shè)計(jì)

在本設(shè)計(jì)中采用Altera公司EPM7064系列CPLD,程序使用VHDL語(yǔ)言編寫(xiě),并在Quartus II環(huán)境下編譯通過(guò),程序主要有“采集模塊”和“讀數(shù)模塊”。采集模塊:在采集模塊中,共有5個(gè)并行進(jìn)程,其中在進(jìn)程1中,首先在主控計(jì)數(shù)器COUNT=10時(shí)開(kāi)始結(jié)合內(nèi)部時(shí)鐘COL信號(hào)來(lái)產(chǎn)生多路開(kāi)關(guān)選通信號(hào)CNT,當(dāng)COL=0時(shí): CNT<=0000.COL=1時(shí):CNT<=0001.以次類推一直到COL=15時(shí)選通15路后,進(jìn)程1停止。在進(jìn)程2中,當(dāng)主控計(jì)數(shù)器COUNT在130和150區(qū)間內(nèi)時(shí),且內(nèi)部計(jì)數(shù)器信號(hào)COL在0~15范圍內(nèi),則開(kāi)始打開(kāi)AD,開(kāi)始采集。在進(jìn)程3中如果主控計(jì)數(shù)器COUNT=185~255時(shí)打開(kāi)RAM的寫(xiě)入狀態(tài)。在進(jìn)程4中當(dāng)主控制計(jì)數(shù)器count=200和220時(shí),結(jié)合內(nèi)部時(shí)鐘信號(hào)COL,分別選擇存入高4位、低8位或者幀計(jì)數(shù)。進(jìn)程5:count=235遞推幀標(biāo)志位和ADG506(模擬開(kāi)關(guān))選通標(biāo)志位,具體見(jiàn)圖6所示。

|

|

|

圖6 采集模塊時(shí)序圖 |

讀數(shù)模塊:讀數(shù)模塊共分為3個(gè)并行進(jìn)程:在進(jìn)程1中,當(dāng)時(shí)鐘上升延時(shí),且如果使能EN_R為高時(shí),且電腦控制讀數(shù)口CPUCLK=1時(shí)開(kāi)始讀數(shù)。在進(jìn)程2中,讀完一次數(shù)據(jù)后,將RAM地址遞推一次。進(jìn)程3中,如果系統(tǒng)為讀數(shù)模塊有效時(shí),數(shù)據(jù)將通過(guò)CPLD發(fā)送到MAX232通過(guò)異步串行的方法將數(shù)據(jù)上傳,具體見(jiàn)圖7所示。

|

|

|

圖7 讀數(shù)模塊時(shí)序圖 |

5 結(jié)束語(yǔ)

本文對(duì)多路數(shù)據(jù)采集系統(tǒng)的組成原理、單元電路設(shè)計(jì)、接口電路設(shè)計(jì)和系統(tǒng)控制程序設(shè)計(jì)進(jìn)行了詳細(xì)的闡述,完成了多路信號(hào)數(shù)據(jù)采集系統(tǒng)軟硬件設(shè)計(jì)。使系統(tǒng)工作安全可靠,數(shù)據(jù)采集精度較高,抗干擾能力較強(qiáng)。具有良好的應(yīng)用前景和很高的使用價(jià)值。