摘 要:介紹了基于浮點(diǎn)DSP處理器與雙CMOS攝像頭的數(shù)字圖像采集處理系統(tǒng)" title="處理系統(tǒng)">處理系統(tǒng),探討了系統(tǒng)的基本原理和設(shè)計(jì)方法,并給出了系統(tǒng)的實(shí)現(xiàn)方案。在該系統(tǒng)中,數(shù)據(jù)采集由兩個(gè)相互獨(dú)立的CMOS攝像頭完成,并由DSP進(jìn)行圖像處理,FPGA協(xié)同DSP完成時(shí)序邏輯控制" title="邏輯控制">邏輯控制和組合邏輯控制。處理后的圖像可以通過(guò)1394接口輸出。該系統(tǒng)主要由FPGA和DSP實(shí)現(xiàn),設(shè)計(jì)靈活,具有很強(qiáng)的重構(gòu)性。?

關(guān)鍵詞:圖像圖像處理 DSP FPGA IEEE1394?

?

??? 傳統(tǒng)的數(shù)字圖像處理通常采用圖像采集卡,將模擬電視信號(hào)轉(zhuǎn)換成數(shù)字信號(hào),然后由PC機(jī)進(jìn)行軟處理。這樣不僅不夠靈活,處理能力也受到PC機(jī)和軟件的限制。隨著CMOS成像芯片工藝的改進(jìn)和數(shù)字信號(hào)處理器功能的提升,使得數(shù)據(jù)量與計(jì)算量較大的圖像硬處理成為可能。本文詳細(xì)介紹了通過(guò)兩路CMOS攝像頭采集圖像,以浮點(diǎn)DSP為核心處理器,采用60萬(wàn)門FPGA實(shí)現(xiàn)邏輯控制的數(shù)字圖像采集處理系統(tǒng)的設(shè)計(jì)原理和實(shí)現(xiàn)方法。本系統(tǒng)所采用的芯片與器件,在保證性能的同時(shí),兼顧低功耗,整個(gè)系統(tǒng)可以由1394線纜供電。

1 原理概述

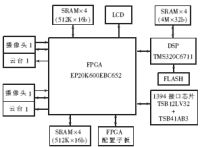

整個(gè)系統(tǒng)的原理框圖如圖1所示。系統(tǒng)上電后,FPGA配置子板把配置文件加載到FPGA中。DSP由外部 FLASH引導(dǎo),通過(guò)FPGA先設(shè)置1394接口芯片的內(nèi)部寄存器,再通過(guò)I2C總線設(shè)置攝像頭1、2的控制寄存器。FPGA提供攝像頭的工作時(shí)序和圖像序列的讀寫時(shí)序。云臺(tái)" title="云臺(tái)">云臺(tái)在DSP的控制下可以上下左右調(diào)整,捕捉感興趣的目標(biāo)。8片1MB的SRAM作為兩路攝像頭的數(shù)據(jù)存儲(chǔ)器,16MB的SDRAM則充當(dāng)DSP的外部數(shù)據(jù)緩沖。處理后的圖像既可以直接輸出至LCD進(jìn)行顯示,也可以通過(guò)1394總線傳送至PC機(jī)。 ?

?

圖1 數(shù)字圖像采集處理系統(tǒng)原理框圖?

2系統(tǒng)設(shè)計(jì)

整個(gè)系統(tǒng)由三部分構(gòu)成:圖像采集模塊、圖像處理模塊和圖像傳輸模塊。

2.1 圖像采集模塊

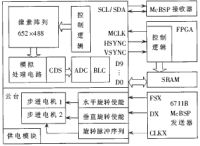

該模塊主要由兩組CMOS攝像頭和云臺(tái)組成。該模塊的接口信號(hào)見圖2。 ?

?

圖2 圖像采集模塊連接圖?

攝像頭采用韓國(guó)現(xiàn)代的HV7131R和五層玻璃透鏡。HV7131R采用0.3μm的CMOS工藝,有效像素30萬(wàn),功耗低于90mW,具有曝光控制、增益控制和白平衡" title="白平衡">白平衡處理等功能,最大幀率30fps@VGA。通過(guò)標(biāo)準(zhǔn)的I2C接口設(shè)置HV7131R的內(nèi)部寄存器,可以調(diào)節(jié)圖像的曝光時(shí)間、分辨率、幀率、RGB增益、鏡像等。HV7131R輸出10位的RGB原始數(shù)據(jù),本系統(tǒng)采用了其中的高8位。多層玻璃透鏡可以濾除波長(zhǎng)大于630nm的紅外線,并采用超焦距對(duì)焦方式,最小成像距離為3cm。

攝像頭借助云臺(tái)跟蹤運(yùn)動(dòng)目標(biāo),水平旋轉(zhuǎn)范圍為-180°~180°;垂直旋轉(zhuǎn)范圍為-45°~45°。

考慮到運(yùn)動(dòng)圖像處理至少需要3幀的序列圖像,每組攝像頭配備了4片RAM。3片做數(shù)據(jù)采集緩沖,1片存儲(chǔ)DSP處理后的結(jié)果。

2.2 圖像處理模塊

該模塊由DSP、FPGA和數(shù)據(jù)緩存器組成。

2.2.1主要器件的選型

DSP主要完成的功能有:

(1)加電自舉,初始化1394接口芯片;

(2)通過(guò)I2C接口設(shè)置攝像頭的寄存器;

(3)對(duì)圖像進(jìn)行預(yù)處理,提高成像質(zhì)量;?

(4)控制云臺(tái)的轉(zhuǎn)動(dòng),實(shí)現(xiàn)運(yùn)動(dòng)目標(biāo)的跟蹤。

FPGA在本系統(tǒng)中的作用有:

(1)提供圖像采集、存儲(chǔ)與傳輸?shù)墓ぷ鲿r(shí)序;

(2)協(xié)同DSP實(shí)現(xiàn)復(fù)雜的組合邏輯控制電路;

(3)實(shí)現(xiàn)標(biāo)準(zhǔn)的VGA接口,外接LCD顯示器。

基于以上要求,本系統(tǒng)采用TI公司的32位浮點(diǎn)DSP TMS320C6711B。6711B采用改進(jìn)的哈佛總線結(jié)構(gòu),主頻為150MHz,內(nèi)部集成硬件乘法器和累加器,采用流水線VelociTITM甚長(zhǎng)指令字(VLIW)指令,具有豐富的片上外設(shè),并有專門針對(duì)數(shù)字信號(hào)處理的指令系統(tǒng),運(yùn)算能力可達(dá)1200MFLOPS,適用于計(jì)算量大、實(shí)時(shí)性高的數(shù)字圖像處理領(lǐng)域。FPGA 則采用Altera公司Apex系列的EP20K600EBC652。EP20K600EBC652具有高速度(622MHz的數(shù)據(jù)速率)、高密度(有效邏輯60萬(wàn)門)、低噪聲和低功耗的特點(diǎn)。有4個(gè)PLL、480個(gè)低電壓差分信號(hào)(LVDS)的I/O口,工作電壓為2.5V和1.8V。

2.2.2圖像的預(yù)處理

運(yùn)動(dòng)目標(biāo)檢測(cè)與跟蹤、目標(biāo)的識(shí)別與提取等基于圖像內(nèi)容的處理,對(duì)圖像質(zhì)量要求較高。影響成像質(zhì)量的兩個(gè)重要因素為曝光和白平衡:人眼對(duì)外部環(huán)境的明暗變化非常敏感,在強(qiáng)光環(huán)境下,瞳孔縮小,使得景物不那么刺眼;而光線較弱時(shí),瞳孔擴(kuò)大,使景物盡可能地變清楚。這在成像中,稱為曝光。當(dāng)外界光線較弱時(shí),CMOS成像芯片工作電流較小,所成圖像偏暗,這時(shí)要適當(dāng)增加曝光時(shí)間進(jìn)行背光補(bǔ)償;光線充足或較強(qiáng)時(shí),要適當(dāng)減少曝光時(shí)間,防止曝光過(guò)度,圖像發(fā)白。改善成像質(zhì)量,僅靠調(diào)節(jié)曝光時(shí)間是不夠的。因?yàn)槲矬w顏色會(huì)隨照射光線的顏色發(fā)生改變,在不同的光線場(chǎng)合圖像有不同的色溫。這就是白平衡問題。傳統(tǒng)光學(xué)相機(jī)或攝像機(jī)通過(guò)給鏡頭加濾鏡消除圖像的偏色現(xiàn)象。對(duì)于CMOS成像芯片,可以通過(guò)調(diào)整RGB三基色的電子增益解決白平衡問題。

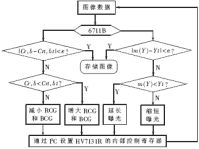

本系統(tǒng)的自動(dòng)曝光控制和白平衡處理實(shí)現(xiàn)方法如下:

采集一幀RGB原始圖像,在6711B中先計(jì)算出整幅圖像亮度的均值m(Y);然后對(duì)圖像做直方圖均衡化,再計(jì)算出此時(shí)圖像的亮度均值并作為一個(gè)閾值Yt。將m(Y)與Yt進(jìn)行比較,如果m(Y) < Yt,則調(diào)大HV7131R的INT(Integration Time)寄存器的值以增加曝光時(shí)間;反之,減小曝光時(shí)間。白平衡的調(diào)節(jié)與此相似,根據(jù)原始圖像與均衡化后的Cr和Cb的均值,通過(guò)HV7131R的RCG(Red Color Gain)、BCG(Blue Color Gain)調(diào)節(jié)紅色、藍(lán)色通道的增益。YCrCb和RGB的轉(zhuǎn)換關(guān)系式為:

Y=0.59G+0.31R+0.11B

Cr=0.713×(R-Y)

Cb=0.564×(B-Y)

其中,Y是亮度分量,Cr和Cb則是色差分量。

HV7131R的曝光時(shí)間范圍為0~(224-1)個(gè)像素時(shí)鐘周期,即0~[email protected];增益范圍一般為30~63。試驗(yàn)結(jié)果表明,經(jīng)過(guò)5~10次的迭代就能取得較為理想的效果。上述過(guò)程示意圖以及成像效果如圖3和圖4所示。 ?

?

圖3 曝光控制和白平衡處理

圖4 成像效果 ?

2.3 圖像傳輸模塊

本系統(tǒng)圖像傳輸模塊采用IEEE1394高速串行總線。1394總線支持點(diǎn)對(duì)點(diǎn)通信、即插即用和熱插拔,有等時(shí)和異步兩種傳輸模式,速率高達(dá)400Mbps,最大有效距離為4.5m。1394線纜可以提供8V~40V的DC電壓以及最高可達(dá)1.5A的電流,完全滿足整個(gè)系統(tǒng)的供電需求。該模塊主要包括鏈路層" title="鏈路層">鏈路層和物理層兩個(gè)控制器。?

2.3.1鏈路層控制器(LLC)

TSB12LV32具有2KB的通用接收FIFO(GRF)與2KB的通用發(fā)送FIFO(ATF),支持異步傳輸與等時(shí)傳輸。微控制器接口支持8/16位的數(shù)據(jù)寬度,工作時(shí)鐘最高達(dá)60MHz。TSB12LV32提供DMA方式,待發(fā)送數(shù)據(jù)邊讀取邊傳送,傳輸效率較高。

2.3.2 物理層控制器(PLC)

TSB41AB3提供三個(gè)1394端口,3.3V單獨(dú)供電,符合1394a標(biāo)準(zhǔn),支持等時(shí)傳輸和異步傳輸,支持100/200/400Mbps的傳輸速率,可以與TSB12LV21、TSB12LV31、TSB12LV32、TSB12LV41或TSB12LV01A等鏈路層控制器實(shí)現(xiàn)無(wú)縫連接,具有較高的通信速率與可靠性。

本系統(tǒng)為了便于調(diào)試,PC機(jī)被設(shè)定為根節(jié)點(diǎn)控制器,應(yīng)用程序和硬件通過(guò)驅(qū)動(dòng)程序進(jìn)行交互。Win32應(yīng)用程序通過(guò)設(shè)備驅(qū)動(dòng)程序、總線驅(qū)動(dòng)程序、端口驅(qū)動(dòng)程序與1394設(shè)備進(jìn)行通信,如圖5所示。 ?

?

圖5 主機(jī)與1394設(shè)備之間的通信?

其中,1394總線驅(qū)動(dòng)程序和端口驅(qū)動(dòng)程序處理所有繁瑣的底層通信,只需提供設(shè)備驅(qū)動(dòng)程序。LLC和PLC的內(nèi)部寄存器通過(guò)6711B設(shè)置,設(shè)備的發(fā)現(xiàn)與識(shí)別、驅(qū)動(dòng)程序的安裝、1394總線的初始化等也需要6711B的控制和響應(yīng)。

本系統(tǒng)圖像的最大數(shù)據(jù)量為640×480×30×2=18.4Mbps,1394a最高支持400Mbps的傳輸速率,圖像實(shí)時(shí)傳輸不需要經(jīng)過(guò)壓縮。實(shí)際傳輸過(guò)程中,為確保每幀圖像的完整,采用異步傳輸模式,圖像序列之間加入了幀同步信號(hào),使帶寬利用率有所下降,最終的實(shí)測(cè)速率為20fps@640×480。該系統(tǒng)采用32位浮點(diǎn)DSP和大容量、多I/O口的高速FPGA,數(shù)據(jù)處理能力強(qiáng),電路設(shè)計(jì)靈活,為今后運(yùn)動(dòng)目標(biāo)檢測(cè)與跟蹤算法的研究提供了軟硬件支持。

參考文獻(xiàn)

1 HV7131R. Data Manual V1.7,[DB]. Hynix Semiconductor,2004

2 TSB41ab3.Data Manual.[DB].Texas Instruments,2003

3 TSB12LV32.Data Manual.[DB].Texas Instruments,2000

4 TMS320C6711B.Data Manual.[DB].Texas Instruments,2003

5 Windows Driver Model. Walter Oney.[M].Microsoft Press

6 何東健.數(shù)字圖象處理.西安:西安電子科技大學(xué)出版社,2003