摘 要: 在某些存儲回放系統(tǒng)" title="回放系統(tǒng)">回放系統(tǒng)中,要求在存儲容量大、數(shù)據(jù)可靠性高的同時,具有較寬的數(shù)據(jù)帶寬,為此,可采用NAND型Flash實現(xiàn)容量要求和數(shù)據(jù)的非易失性;采用FPGA進(jìn)行多片存儲體并行讀取,從而克服了NANDFlash固有的讀取速度慢的缺點,并擴(kuò)展了存儲深度;同時引入雙主設(shè)備的設(shè)計,利用FPGA與PC104實現(xiàn)存儲和讀取的功能分離,是存儲方式靈活,控制方便的解決方案。本文介紹的方案降低了此類系統(tǒng)的實現(xiàn)難度,縮短了產(chǎn)品研發(fā)周期,已應(yīng)用于實際系統(tǒng)中并得到好評。

關(guān)鍵詞: NAND Flash FPGA PC104

閃存(Flash Memory)由于其具有非易失性、電可擦除性、可重復(fù)編程以及高密度、低功耗等特點,而被廣泛地應(yīng)用于U盤、MP3和數(shù)碼相機(jī)等的數(shù)據(jù)存儲" title="數(shù)據(jù)存儲">數(shù)據(jù)存儲設(shè)備中。NAND 和NOR Flash是目前市場上兩種主要的非易失閃存芯片。與NOR型Flash相比,NAND型Flash在容量、功耗、使用壽命等方面的優(yōu)勢使得它成為高數(shù)據(jù)存儲密度的理想解決方案。本文以Samsung公司生產(chǎn)的K9F1G08UOM為例,介紹NAND型Flash在板載大容量" title="大容量">大容量數(shù)據(jù)存儲回放系統(tǒng)中的應(yīng)用。

1 器件簡介

1.1功能特性

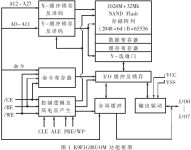

NAND型Flash芯片是Samsung 公司推出的新一代大容量數(shù)據(jù)存儲器件,電源電壓范圍為1.7~3.6V,功耗低,TSSOP封裝體積小,目前最大" title="最大">最大單片容量可達(dá)8Gb,按頁讀寫,按塊擦除。本次應(yīng)用開發(fā)的是容量為1Gb的K9F1G08UOM,其功能框圖[1]如圖1所示。由圖1可以看出,該器件按功能可以劃分為如下幾個部分:存儲陣列、輸入輸出緩沖、命令寄存器、地址譯碼寄存器和控制邏輯產(chǎn)生。其中,命令寄存器用來確定外部設(shè)備對存儲器進(jìn)行操作的類型,地址譯碼寄存器保存被訪問的地址并產(chǎn)生相應(yīng)的譯碼選通信號。主設(shè)備通過8位的I/O" title="I/O">I/O端口分時復(fù)用訪問器件命令、地址和數(shù)據(jù)寄存器,完成對芯片內(nèi)存儲體的訪問。

1.2 存儲體的組織結(jié)構(gòu)

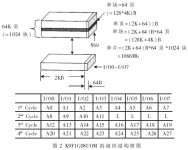

K9F1G08UOM的組織結(jié)構(gòu)框圖[1]如圖2所示。從圖2可知,該K9F1G08UOM存儲體由1024個塊(Block)組成,每個Block含有64個頁(Page),每個Page內(nèi)有2K+64個字節(jié),其中2KB為主存儲區(qū),用來保存用戶數(shù)據(jù);剩余的64個字節(jié)為輔助存儲區(qū),用來保存一些狀態(tài)信息,如:壞塊標(biāo)志位、ECC碼等。由圖2中所列的表可知,由于I/O端口的寬度為8位,訪問時需要在前兩個地址訪問周期內(nèi)給出12位列地址(沒有使用到的地址管腳必須拉至低電平),以及尋址到頁內(nèi)字節(jié),然后在接下來的兩個地址訪問周期內(nèi)給出16位的行地址以確定頁號和塊號;對于同等容量16位器件,由于二者的區(qū)別僅在于單頁字節(jié)容量不同,所以訪問時頁內(nèi)地址只需要給出11位,并且地址仍按8位經(jīng)由I/O0~I/O7給出,其余未使用的地址管腳拉至低電平。

?

1.3 選擇器件的參考因素

選擇NAND器件時,除了根據(jù)實際應(yīng)用選擇合適的容量以外,還需要考慮對NAND型Flash各種操作的速度是否能滿足系統(tǒng)需求。表1給出了1Gb容量兩種位寬類型的器件在讀、寫、擦除三種主要操作的近似速度,具體計算方法和參數(shù)可見參考文獻(xiàn)[2]、[3]。需要強(qiáng)調(diào)的是:

(1)位寬加倍對編程速度沒有太大影響,這主要是因為在將一頁數(shù)據(jù)寫入Flash片內(nèi)的寄存器后,器件自身將該頁數(shù)據(jù)寫入存儲單元的時間基數(shù)較大。

(2)位寬加倍使得讀取速度接近翻番。

(3)由于器件按塊擦除,所以位寬對擦除速度基本沒有影響。

2 應(yīng)用實例

以一板載大容量數(shù)據(jù)回放系統(tǒng)為例,其系統(tǒng)結(jié)構(gòu)如圖3所示,主要包括CPU模塊、FPGA、NAND Flash和數(shù)模轉(zhuǎn)換模塊四部分。其中,CPU模塊為一個與IBM-PC/AT兼容的PC/104 CPU模塊,并作為整個系統(tǒng)的主控設(shè)備,完成數(shù)據(jù)接收、存儲、回放參數(shù)設(shè)置等功能。CPU模塊直接通過標(biāo)準(zhǔn)PC/104接插件固定在母板上;FPGA采用Xilinx公司Spartan3系列XC3S1000[2],主要完成數(shù)據(jù)的回放功能;數(shù)模轉(zhuǎn)換模塊完成數(shù)據(jù)從數(shù)字域到模擬域的轉(zhuǎn)換,轉(zhuǎn)換速率為100MBps;NAND Flash采用8位位寬、單片1Gb容量的K9F1G08UOM,用來存儲回放數(shù)據(jù),考慮單片F(xiàn)lash的數(shù)據(jù)輸出率有限,系統(tǒng)中采用8片并行處理,所以存儲容量是8Gb。

FPGA模塊是本系統(tǒng)的關(guān)鍵,其片內(nèi)系統(tǒng)結(jié)構(gòu)如圖4所示。設(shè)計要點如下:

2.1 功能劃分

系統(tǒng)中允許兩個主設(shè)備即FPGA和CPU模塊訪問Flash;在此將FPGA在邏輯上劃分為Master和Slave兩種模式。Master表示FPGA作為Flash的主設(shè)備,占用Flash 的總線,此時CPU模塊只能訪問FPGA內(nèi)的控制寄存器;Slave則表示FPGA和Flash均作為CPU模塊的從設(shè)備接受訪問,F(xiàn)lash和FPGA均映射到CPU模塊的某段I/O地址空間。此時對Flash來講,F(xiàn)PGA只是提供CPU至Flash的數(shù)據(jù)和控制通路。FPGA片內(nèi)系統(tǒng)結(jié)構(gòu)如圖4所示。圖中:CPU通過PC/104總線訪問控制寄存器的相應(yīng)位來控制FPGA的狀態(tài)切換,粗黑線只代表數(shù)據(jù)鏈路(控制鏈路都為單向信號,較數(shù)據(jù)鏈路簡單,但連接方式與數(shù)據(jù)通路類似,為簡化框圖已省略)。

雖然CPU模塊與FPGA均能訪問Flash,但是在具體實現(xiàn)時,如圖4所示,F(xiàn)PGA內(nèi)只實現(xiàn)對Flash的讀控制,而其他諸如寫操作、擦除以及檢測壞塊(invalid block)等操作則由CPU模塊完成。這樣設(shè)計的原因是:

(1)系統(tǒng)帶寬要求。前面提到了系統(tǒng)要求的輸出數(shù)據(jù)速率為100MBps,而單片F(xiàn)lash的峰值數(shù)據(jù)輸出速率僅為16MBps;PC/104總線的時鐘頻率為8MHz,且一個指令周期至少需要6個時鐘,這樣即使多片F(xiàn)lash并片操作也難滿足系統(tǒng)要求。而FPGA實現(xiàn)時,則可以完全根據(jù)Flash的訪問時序要求設(shè)計狀態(tài)機(jī),時間裕量可以很精確地調(diào)整,從而盡可能地接近對Flash訪問的最大帶寬。因此用FPGA實現(xiàn)其控制,性能要優(yōu)于CPU實現(xiàn)的方案。

(2)簡化系統(tǒng)的設(shè)計和調(diào)試難度。雖然FPGA實現(xiàn)對Flash的訪問可以達(dá)到最大帶寬,但是它的設(shè)計以及調(diào)試卻遠(yuǎn)較CPU實現(xiàn)復(fù)雜和困難。在FPGA設(shè)計中,設(shè)計者必須很精確地以數(shù)據(jù)流形式描述整個設(shè)計,必須很清楚地了解每個時刻信號的變化,而且設(shè)計當(dāng)中的信號很不易觀測,出現(xiàn)錯誤后對問題的定位比較困難。相比之下,CPU模塊通過高級語言,以算法級的方式實現(xiàn),再輔助以良好的開發(fā)調(diào)試環(huán)境,實現(xiàn)Flash控制要容易得多。本應(yīng)用中將對Flash的寫、擦除、記錄壞塊表等對時間要求不高的操作轉(zhuǎn)移至CPU模塊,這樣可以大大降低整個系統(tǒng)的設(shè)計和調(diào)試難度。

2.2 FPGA與NAND Flash的接口設(shè)計

NAND Flash和通常使用的存儲器最大差別是接口的不同,通常使用的非易失性存儲器如NOR Flash,由于它有一套完整的地址映射即訪問接口,指定的地址總線和數(shù)據(jù)總線,從而可以很容易地訪問其內(nèi)部的每一個字節(jié)。而NAND Flash沒有專門的地址線;它的接口是一種間接類I/O接口[3],通過8位的總線分別發(fā)送命令和地址到命令、地址寄存器來控制。以典型的“讀”命令為例:寫“讀”命令到命令寄存器,寫入4字節(jié)的地址到地址寄存器,等待設(shè)備將要求的數(shù)據(jù)放到輸出寄存器,從數(shù)據(jù)寄存器讀取一頁的數(shù)據(jù)。NAND Flash這種接口的缺點是一般情況下無法用來引導(dǎo)系統(tǒng),除非外接專門的狀態(tài)機(jī)或控制器。其優(yōu)點是:由于地址寄存器在芯片內(nèi)部,芯片的管腳隨著芯片容量的增加基本上不變,而且FPGA實現(xiàn)Flash訪問,其接口設(shè)計無任何特殊要求,接口信號按通用I/O管腳設(shè)計即可(這里說的接口設(shè)計是指在Slave模式下,CPU模塊與Flash接口設(shè)計)。本設(shè)計中采用的接口如圖5所示。

由圖5可知,設(shè)計中通過L_A0、L_A1(在Slave模式下直接映射到PC/104總線對應(yīng)的低地位地址線;在Master模式下則連接至讀控制的對應(yīng)輸出端口)直接產(chǎn)生命令寄存器和地址寄存器選通信號,而芯片的Ready/Busy信號直接通過L_GPIO口傳遞給FPGA,然后給CPU模塊。這種設(shè)計結(jié)構(gòu)簡單,訪問速度快,唯一的缺點就是要求所使用的NAND型Flash必須具備CEDC(Chip Enable Don′t Care)特性,即不需要/CE(芯片使能信號)在整個操作的周期都一直拉低。

2.3 FPGA實現(xiàn)NAND型Flash讀狀態(tài)機(jī)的設(shè)計

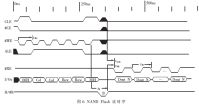

K9F1G08UOM的讀時序如圖6[2]所示。設(shè)計中的關(guān)鍵是保證命令、地址、數(shù)據(jù)以及控制信號在時序上的要求。由圖可知,對Flash的讀、寫操作的最小時鐘周期分別為tWC(45ns)和tRC(50ns)。為了方便設(shè)計,狀態(tài)機(jī)的時鐘選取40MHz(25ns)。當(dāng)然,在資源足夠的情況下也可以采用更高頻率的時鐘以減小時間裕量,從而提高訪問速度。本設(shè)計程序?qū)嵗缦拢?BR> //cle_o-命令寄存器使能; ce_o-片選使能; we_o-寫使能; ale_o-地址寄存器使能

//re_o-讀使能; rb_i-等待/忙信號 //start_i-讀啟動信號

always @ (posedge clk_i )

if ( rst_i) begin

MooreState<=S0; //復(fù)位狀態(tài)

cle_o<=1′b0;ce_o<=1′b1;we_o<=1′b1;re_o<=1′b1;ale_o<=1′b0;io_o<=8′hxx;

count_en<=1′b0; end

else

case (MooreState)

S0:begin MooreState<=start_i?S1:S0;re_o<=1′b1;end

S1: begin MooreState <= S2; //寫命令寄存器

cle_o<=1′b1;ce_o<=1′b0;we_o<=1′b0;io_o<=8′h00; end

S2: begin MooreState<=S3;we_o<=1′b1;end

S3: begin MooreState <=S4; //寫地址寄存器1

cle_o<=1′b0; we_o<=1′b0;ale_o<=1′b1;io_o<=

coladr_l; end

S4: begin MooreState<=S5;we_o<=1′b1;end

S5: begin MooreState<=S6; //寫地址寄存器2

we_o<=1′b0;io_o<=coladr_h; end

S6: begin MooreState<=S7;we_o<=1′b1;end

S7: begin MooreState<=S8; //寫地址寄存器3

we_o<=1′b0;io_o<=radr_l; end

S8: begin MooreState<=S9;we_o<=1′b1;end

S9: begin MooreState<=S10; //寫地址寄存器4

we_o<=1′b0;io_o<=radr_h; end

S10: begin MooreState<=S11;we_o<=1′b1;end

S11: begin MooreState <= S12; //寫命令寄存器

cle_o<=1′b1;we_o<=1′b0;ale_o<=1′b0;io_o<=

8′h30; end

S12: begin MooreState<=S13;we_o<=1′b1;end

S13: begin MooreState<= rb_i? //忙等待

S14: S13;

cle_o<=1′b0;io_o<=8′hxx; end

S14: begin MooreState <= S15; //循環(huán)讀一頁數(shù)據(jù)

re_o<=1′b0;count_en<=1′b1;end

S15: begin MooreState<= (count_n==4095)?S16:S14;

re_o<=1′b1; end

S16: begin MooreState <=S0; //結(jié)束

ce_o<=1′b1;count_en<=1′b0; end

endcase

always @ (posedge clk_i )

begin if (rst_i) count_n<=1;

else if (count_en) count_n<=count_n+1;

else count_n<=1;

end

上述程序中,在讀操作時使用了Moore型狀態(tài)機(jī),其最大特點就是輸出僅依賴于狀態(tài)機(jī)的狀態(tài),與它的輸入無關(guān);而描述Moore狀態(tài)機(jī)的最佳方式之一就是在always語句中使用case語句實現(xiàn)不同狀態(tài)間的轉(zhuǎn)換,且每種狀態(tài)的輸出邏輯都在相應(yīng)的分支中描述。

狀態(tài)進(jìn)程:本例中將讀操作分成17個狀態(tài),其中狀態(tài)S0用來初始化各輸出信號,狀態(tài)S1~S2和S12~S13完成對命令寄存器的寫操作,狀態(tài)S3~S11完成4次對地址寄存器的寫操作,狀態(tài)S14、S15則完成一頁數(shù)據(jù)的連續(xù)讀取。

組合進(jìn)程:組合進(jìn)程是根據(jù)當(dāng)前狀態(tài)(現(xiàn)態(tài))給輸出信號賦值,并決定下一狀態(tài)(次態(tài))。在本例中,狀態(tài)機(jī)根據(jù)不同的狀態(tài)對ce、ale、cle、we、re、io等Flash信號進(jìn)行賦值,以實現(xiàn)對Flash 的控制功能。

另外,增加一個always語句實現(xiàn)同步計數(shù),用于對讀取的數(shù)據(jù)個數(shù)計數(shù)。

上述程序只是讀操作部分,具體讀控制還包括地址產(chǎn)生、壞塊表檢測以及其他一些控制部分,由于篇幅有限,此處不贅述。

2.4 壞塊表的建立

由于NAND型Flash存儲容量較大,難免在使用過程中出現(xiàn)存儲單元的損壞,因此有必要記錄每片F(xiàn)lash壞塊的位置。設(shè)計中首先由CPU模塊通過PC104總線訪問Flash,檢測器件中的壞塊并建立壞塊表(invalid block table),然后存儲在FPGA內(nèi)的雙口RAM中。數(shù)據(jù)回放時,讀狀態(tài)機(jī)在跨塊時需要將當(dāng)前塊的塊號和壞塊表中的塊號按遍歷方式進(jìn)行比較,當(dāng)確認(rèn)該塊為壞塊時,將跳至下一可用塊;否則讀取該塊數(shù)據(jù)。檢測壞塊的程序流程如圖7所示,實現(xiàn)壞塊檢測的C代碼如下:

RAdr_H=0; RAdr_L=0;

for(k=0; k<256; k++)

//遍歷1024個block,檢測壞block

{

for(j=0; j<4; j++)

{ //讀取第1頁第2 048個字節(jié)

outportb(ComReg,0x00);

outportb (AddReg,0x00);

outportb (AddReg,0x08);

outportb (AddReg, RAdr_L);

outportb (AddReg, RAdr_H);

outportb (ComReg,0x30);

while( inportb(RB_Adr )!=0x01) { };

FP2048=inportb (DataReg);

outportb(ComReg,0x00);

//讀取第2頁第2 048個字節(jié)

outportb (AddReg,0x00);

outportb (AddReg,0x08);

outportb (AddReg,RAdr_L+1);

outportb (AddReg,RAdr_H);

outportb (ComReg,0x30);

while( inportb (RB_Adr)==0x01 ) {};

SP2048= inportb (DataReg);

if((FP2048!=0xff)or(SP2048)!=0xff) )

//判斷第1、2頁的第2048字節(jié)是否為0xff

{Inv_Add=RAdr_H*256+RAdr_L&0xC0;

outport(Inv_Add,Inv_Tab_Add);

Inv_Tab_Add=Inv_Tab_Add+1;}

RAdr_L=RAdr_L+0x40;

} /* end of for(..j..) */

RAdr_H=RAdr_H+1;

} /* end of for(..k..) */

上述代碼中,ComReg為命令寄存器地址,AddReg為地址寄存器地址,DataReg為數(shù)據(jù)端口地址,Inv_Tab_Add為壞塊表地址,RB_Adr則為芯片R/B信號反饋至GPIO口的端口地址。

2.5 數(shù)據(jù)緩沖問題

如前所述,F(xiàn)PGA內(nèi)部8個并行運(yùn)行的讀狀態(tài)機(jī)獨立完成每片F(xiàn)lash的讀取操作,并片后,必然會導(dǎo)致各片F(xiàn)lash在讀取數(shù)據(jù)時存在時間上的錯位,特別是當(dāng)其中一片F(xiàn)lash出現(xiàn)壞塊,讀狀態(tài)機(jī)需要跨塊讀取時,這個問題會更加嚴(yán)重。為了解決這個問題,F(xiàn)PGA的設(shè)計中增加了用來緩沖數(shù)據(jù)的FIFO,以隔離FIFO前后速度非一致的數(shù)據(jù)流。FIFO的深度由讀狀態(tài)機(jī)跨塊所需要的時間間隔和FIFO的輸出時鐘100MHz共同決定,以保證FIFO輸出數(shù)據(jù)流不間斷。

本文介紹的系統(tǒng)利用FPGA和PC104模塊分別完成對NAND型Flash的讀寫操作,不僅滿足了系統(tǒng)存儲深度8Gb的要求,而且利用FPGA內(nèi)多個獨立并行狀態(tài)機(jī)實現(xiàn)了多片F(xiàn)lash的并行讀取操作,滿足了數(shù)據(jù)回放的帶寬要求,并實際應(yīng)用于某干擾系統(tǒng)中,效果理想。

參考文獻(xiàn)

1 XILINX. Spartan-3 platform FPGA handbook[EB/OL],http://www.xilinx.com, 2003

2 Samsung. K9F1G08UOM K9F1G16UOM flash memory data-sheet rev.13[EB/OL],http://www.sumsung.com,2003

3 Samsung. NAND flash spare assignment recommendation [EB/OL],http://www.sumsung.com, 2003

4 TOSHIBA,What is NAND flash memory? [EB/OL],http://www.toshiba.com, 2003