引 言

光電混合模式識別以其高速并行處理和無串?dāng)_的優(yōu)點成為實現(xiàn)模式識別實用化和實時化的重要途徑,其在目標(biāo)識別、指紋識別、光纖檢測、工業(yè)零件識別、汽車牌照識別等領(lǐng)域得到了廣泛的研究和應(yīng)用[1.2],并取得了很好的識別效果。

但在實際應(yīng)用中,待識別的目標(biāo)圖像需要經(jīng)過圖像預(yù)處理和畸變處理等操作。針對圖像的實時處理要求,本文將聯(lián)合變換相關(guān)識別系統(tǒng)與數(shù)字信號處理中的雙CPU技術(shù)相結(jié)合,采用“FPGA+DSP+ARM”架構(gòu),研究與設(shè)計一種新型的光電混合圖像識別系統(tǒng)。利用TMS320C6416與FPGA完成目標(biāo)圖像的采集與處理,利用ARM9處理器S3C2440完成對相關(guān)功率譜的采集與目標(biāo)圖像識別,從而實現(xiàn)畸變不變模式識別的快速和準確性。并實現(xiàn)了該系統(tǒng)的智能化和網(wǎng)絡(luò)化。

該光電混合圖像識別系統(tǒng)每秒能處理25幀圖像,可實現(xiàn)真正的動態(tài)圖像識別,因而對圖像識別有很好的實用性。

1 光電混合圖像識別系統(tǒng)

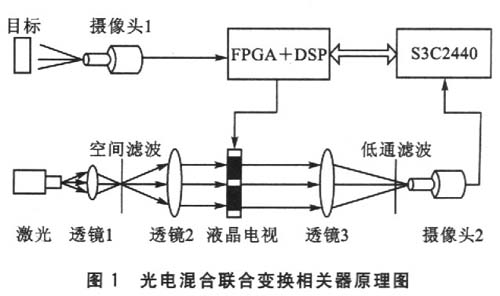

光電混合圖像識別系統(tǒng)是基于光電混合聯(lián)合變換相關(guān)器的一種系統(tǒng),本文提出并設(shè)計的光電混合圖像識別系統(tǒng)的結(jié)構(gòu)框圖如圖1所示。

ARM9處理器S3C2440與DSP間為主/從方式,DSP與FPGA問也為主/從方式。由DSP和FPGA組成的目標(biāo)圖像采集與處理模塊,將待識別的目標(biāo)通過攝像頭1傳輸?shù)紻SP中,DSP完成對目標(biāo)圖像的預(yù)處理和畸變處理等處理過程。然后,DSP將處理后的目標(biāo)圖像和參考圖像構(gòu)成的聯(lián)合輸入圖像實時輸出到液晶電視上,聯(lián)合圖像經(jīng)過激光光束的照射后,經(jīng)傅里葉變換透鏡3后,形成聯(lián)合圖像傅里葉頻譜。該頻譜經(jīng)低通濾波后,得到所需的中心頻譜[3],并通過攝像頭2接收進入ARM9處理器S3C2440,來完成圖像頻譜的振幅調(diào)制及傅里葉逆變換的處理,得到所需互相關(guān)結(jié)果。由于真目標(biāo)互相關(guān)信號較強,假目標(biāo)的互相關(guān)信號很弱,可以通過設(shè)定閾值來判斷真假目標(biāo)圖像,即當(dāng)相關(guān)結(jié)果大于閾值時,識為真目標(biāo),小于閾值時,識為假目標(biāo)。當(dāng)判為假目標(biāo)時,通過通信接口控制DSP繼續(xù)進行圖像采集與處理,實現(xiàn)下一個目標(biāo)的圖像識別,直至判別出真目標(biāo)。

2 系統(tǒng)設(shè)計

該光電圖像識別系統(tǒng)主要由目標(biāo)圖像采集與處理模塊、光電相關(guān)聯(lián)合變換模塊以及自動識別模塊組成,采用TMS320c6416DSP與FPGA來完成目標(biāo)圖像的采集與處理,采用ARM9處理器S3C2440來完成對相關(guān)功率譜的采集與目標(biāo)圖像識別。

2.1 TMS320C6416

C64x是TI公司推出C6000系列DSP中的最新成員,采用了VelociTI1.2結(jié)構(gòu),其主要在內(nèi)部CPU功能單元、通用寄存器組及其數(shù)據(jù)通路等方面進行了較大的改進。C64x具有8個相互獨立的功能單元,其中包含6個支持單周期內(nèi)單32位、雙16位

或4個8位數(shù)據(jù)操作的算術(shù)邏輯單元,以及2個支持單周期雙16×16位或4個8×8位數(shù)據(jù)操作的乘法器;內(nèi)部CPU的通用寄存器組含有32個32位寄存器,支持8位和64位定點數(shù)據(jù),并且寄存器A0也可用作條件寄存器;通用寄存器組內(nèi)部有兩條交叉通路,且都可以通過交叉通路訪問另一側(cè)的寄存器組;C64x還能夠利用非排列的存取指令訪問任意字節(jié)邊界的字或雙字。

與C62x相比,C64x平均每條指令在每個時鐘周期內(nèi)的運算能力增加了7.6倍。由于C64x支持雙16位和8位數(shù)據(jù)以及時鐘頻率的提高,使得其圖像處理能力比C62x提高了15倍左右。C64x為程序和地址兩級片內(nèi)存儲器結(jié)構(gòu)。一級存儲器由程序(L1P)和數(shù)據(jù)(L1D)緩存組成。其中L1P為512組32B的16KB直接映像式緩存,L1D為128組64B的16KB兩路組相聯(lián)式緩存。C64x具有與C621x、C67lx不同的存儲體結(jié)構(gòu),其存儲體位于32位邊界,因此對于相同存儲體訪問時,地址總線的3LSBs相同。另外,C64x具有豐富的外設(shè)資源,其中包括:64通道的增強型存儲器直接存取(EDMA)控制器;64位/16位數(shù)據(jù)總線的外部存儲器接口EMIFA/EMIFB;33MHz、32位PCI接口和針對異步傳輸模式的UTOPLA接口;16位或32位主機端接口;3個多通道緩沖串行口等。

內(nèi)部結(jié)構(gòu)的改進、并行處理能力的提高及豐富的外設(shè)資源,使得C64x在圖像處理領(lǐng)域具有巨大的開發(fā)潛力。為提高系統(tǒng)實時性能,本文采用主頻400 MHz的TMS320C6416GLZ作為目標(biāo)圖像處理單元來設(shè)計該識別系統(tǒng)。

2.2 目標(biāo)圖像采集與處理模塊

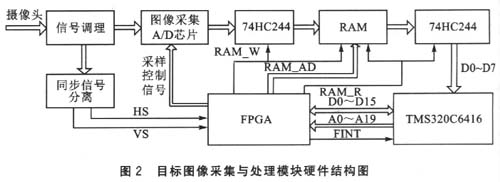

該模塊主要由DSP處理器TMS320C6416和FPGA來實現(xiàn),DSP和FPGA之間采用主/從方式。其中,DSP主要完成對目標(biāo)圖像的處理及控制FPGA采樣信號的啟動。FPGA則完成對目標(biāo)圖像的采樣控制過程,其硬件結(jié)構(gòu)圖如圖2所示。

由攝像頭拍攝到的圖像首先進行信號調(diào)理,即對圖像進行嵌位、錟相、放大以及同步信號分離。然后,由DSP啟動對圖像信號的采樣,即控制FPGA進行圖像的采樣,同時通過中斷查詢方式(FTNT),監(jiān)控FPGA發(fā)出的采樣完成信號。

采用TI公司的TLC5510芯片來進行高速A/D采樣。TLC5510為5V電源、8位、20Msps的高速并行ADC,最大量程為2V。為了達到實時處理的目的,本系統(tǒng)只采集灰度圖像,CCD圖像的幀頻為30Hz,幀圖像分辨率為512×512像素,每個像素點8位量化。

FPGA在行(HS)、場(VS)同步信號和時鐘信號的驅(qū)動下,產(chǎn)生A/D采樣的控制信號來控制采樣過程,同時,F(xiàn)PGA提供存儲器地址及片選與讀寫控制信號,數(shù)字信號按照該地址并在RAM_W有效時,寫入FPGA存儲器RAM中,為圖像預(yù)處理作好準備。

采樣完成后,F(xiàn)PGA產(chǎn)生外部中斷,向DSP發(fā)出中斷請求,DSP進入中斷處理:FPGA提供RAM的地址信號,并在RAM_R有效時,DSP將RAM中的采樣數(shù)據(jù)以EDMA方式讀至同步動態(tài)存儲器SDRAM中。SDRAM為4balaks×512 kb×32b,時鐘主頻為166 MHz,這樣就保證了工作時所需的存儲容量和實時性的要求。數(shù)據(jù)傳輸完畢,DSP啟動FPGA進行下一幀圖像的采樣,F(xiàn)PGA再次進入采樣控制處理過程,DSP則對目標(biāo)圖像數(shù)據(jù)進行預(yù)處理和畸變等處理。

在完成對目標(biāo)圖像的數(shù)據(jù)處理后,DSP將處理后目標(biāo)圖像和存儲在ROM中的參考圖像構(gòu)成的聯(lián)合輸入圖像實時輸出到液晶電視上的約定區(qū)域內(nèi),以便進行光信息處理。

2.3 自動識別模塊

自動識別模塊采用三星公司ARM處理器S3C2440來完成。S3C2440處理器是基于ARM920T內(nèi)核的32位RISC嵌入式

芯片。該ARM內(nèi)核的CPU主頻最高可達533MHz,此處使用499MHz,它除了集成3個串口、SD卡控制器、USB Host控制器、LCD控制器、Nand Flash控制器以及實時時鐘外,還增添了工業(yè)控制總線(CAN)、Camera控制器(數(shù)碼攝像機接口)、PCMCIA接口(可接無線網(wǎng)卡或調(diào)制解調(diào)器及其他外設(shè))。另外,用1個96針總線插槽引出CPU的局部總線,可外接其他總線設(shè)備并與多方通信。目前,S3C2440已被廣泛應(yīng)用于工業(yè)控制、多媒體處理、消費類電子及網(wǎng)絡(luò)通信等領(lǐng)域。

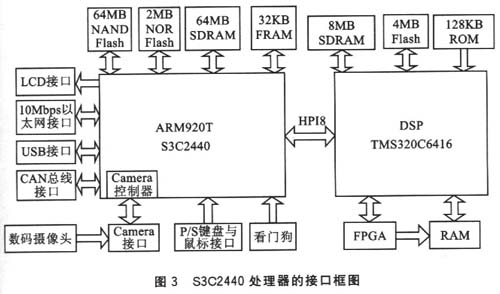

S3C2440處理器的接口框圖如圖3所示。S3C2440內(nèi)置Camera控制器,并支持最大為4096×4096像素的圖像輸入,因此本系統(tǒng)對聯(lián)合頻譜圖像的獲取選用130萬像素攝像頭進行視頻采集與傳輸,通過Catnera控制器完成對頻譜圖像的數(shù)據(jù)轉(zhuǎn)換與存儲,然后對頻譜進行振幅調(diào)制和傅里葉反變換,得到互相關(guān)結(jié)果,從而進行判別與處理。

圖3中,64MB NAND Flash采用三星的。K9F1208,用于存放應(yīng)用程序;2MB的NOR Flash采用AMD的AM29LV160DB,用于存放Bootloader及Kernel;64MBSDRAM采用現(xiàn)代的HY57V561620;32KB FRAM(鐵電存儲器),減少對Flash的頻繁操作,延長Flash壽命,同時防止掉電時數(shù)據(jù)丟失。

S3C2440作為主控處理器,還負責(zé)與上位機進行通信,并可通過網(wǎng)卡與Internet進行互聯(lián),實現(xiàn)該系統(tǒng)的智能化與網(wǎng)絡(luò)化。另外,還可通過USB接口進行數(shù)據(jù)的存取。

2.4 系統(tǒng)軟件主流程

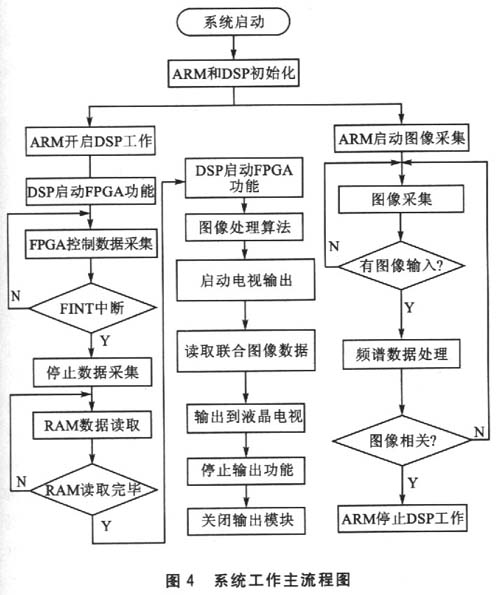

該光電混合圖像識別系統(tǒng)工作主流程如圖4所示。ARM和DSP在完成初始化后,通過HPI口加載DSP程序并通過中斷激活DSP運行;DSP在工作后啟動FPGA,F(xiàn)PGA控制A/D采樣芯片進行實時圖像采集。

3 結(jié)論

本文研究與設(shè)計了一種新型的基于雙CPU技術(shù)的光電圖像識別系統(tǒng)。該系統(tǒng)由TMS320C6416與FPGA完成目標(biāo)圖像的采集與處理,通過光電相關(guān)聯(lián)合變換器得到圖像的聯(lián)合頻譜,利用S3C2440完成對相關(guān)功率譜的采集與目標(biāo)圖像自動識別。該識別系統(tǒng)圖像處理能力達25幀/s,因而實現(xiàn)了真正動態(tài)圖像的圖像識別。與傳統(tǒng)光電圖像識別系統(tǒng)相比,該系統(tǒng)實時性和精度更高,并實現(xiàn)了智能化和網(wǎng)絡(luò)化,有較高的實用價值。